Analizziamo in questo articolo come utilizzare i blocchi ISERDES ed OSERDES delle Spartan-6 per la realizzazione di applicazioni seriali source-synchronous fino a 1080 Mbps.

Spartan-6 è la famiglia di FPGA correntemente supportata da Xilinx per applicazioni a bassa dissipazione di potenza e costi contenuti. I dispositivi offrono tecnologia di gestione avanzata della potenza, capacità logica fino a 150k celle, end-point PCI Express integrato, slice DSP con clock fino a 250 MHz, transceiver GTP a 3.2 Gbps, risorse Select I/O. Di seguito, in particolare, è discusso l’utilizzo dei moduli di ISERDES2/OSERDES2 per la realizzazione di applicazioni di trasmissione dati source-synchronous.

INTRODUZIONE AI BLOCCHI ISERDES2 ED OSERDES2

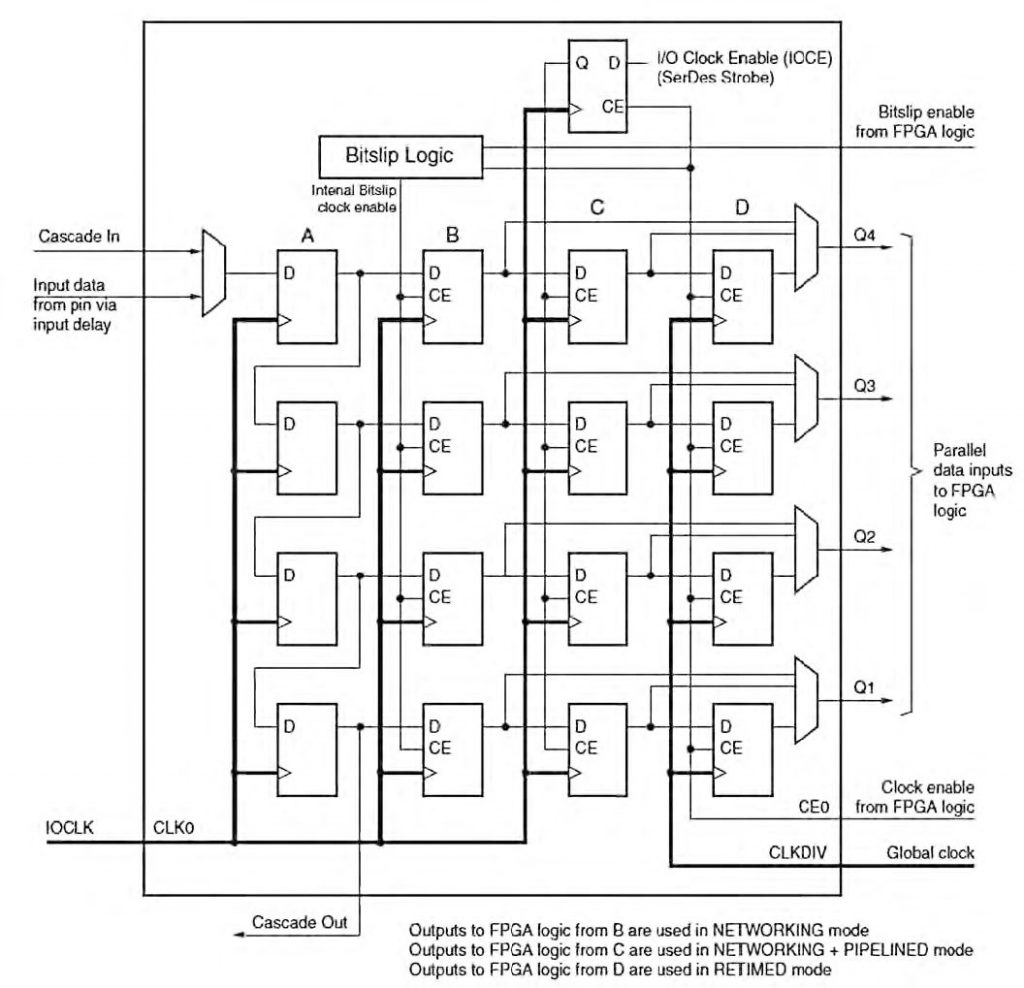

I blocchi di Input/Output (IOB) delle FPGA Xilinx Spartan-6 includono circuiti dedicati per serializzazione (OSERDES2) e deserializzazione (ISERDES2) dei dati. La Figura 1 mostra, in particolare, lo schema di principio della struttura di un blocco ISERDES2. Il dato seriale in ingresso è shiftato in un registro a scorrimento di profondità massima di 4 bit e quindi caricato in un registro parallelo dotato di abilitazione; entrambi i registri operano con il clock IOCLK, eventualmente generato mediante PLL interno alla FPGA. L’abilitazione è generata da un circuito BitSlip interno, dotato anche di controllo esterno per il riallineamento corretto dei dati nei casi di disponibilità di un segnale di framing. Il circuito di BitSlip consente di deserializzare i dati con fattori di 1:2, 1:3 ed 1:4. L’uscita del registro parallelo può essere connessa direttamente alla FPGA Fabric o ad un registro di risincronizzazione rispetto al segnale di clock globale proveniente dalla stessa. Il registro a scorrimento di ingresso dispone di uscita di riporto che consente la connessione in cascata di due deserializzatori per applicazioni con rapporto di ricostruzione fino a 1:8.

Figura 1: schema del circuito ISERDES delle FPGA Spartan-6

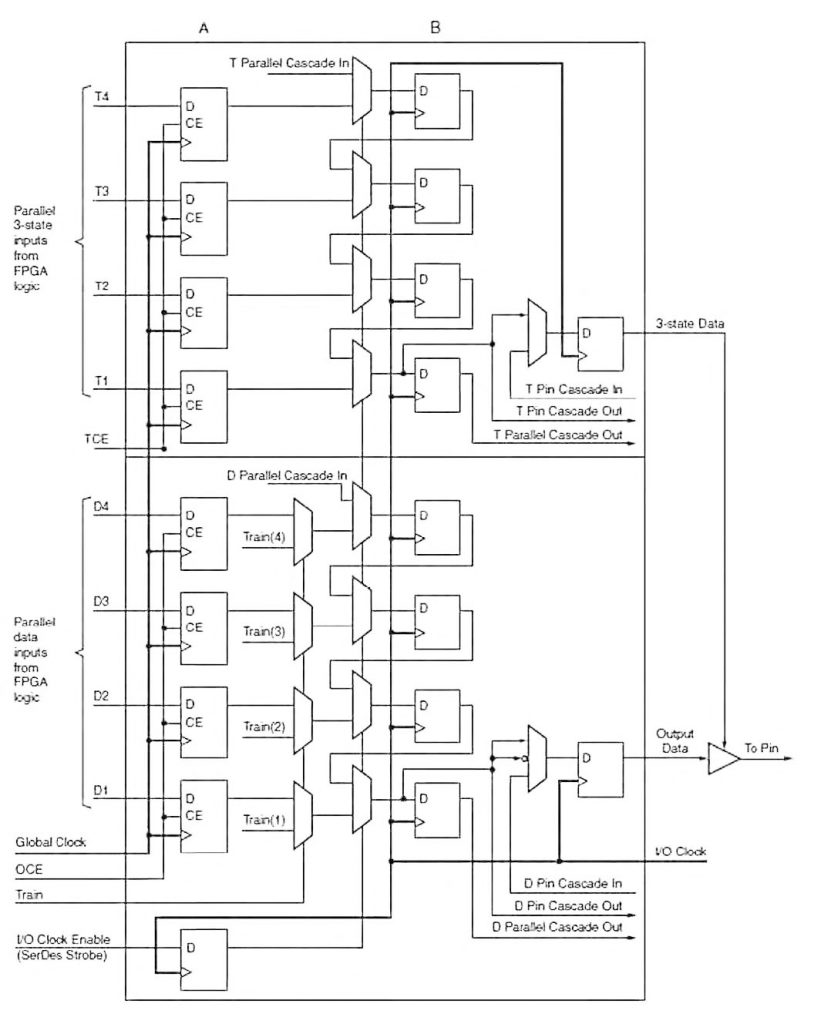

In Figura 2 è mostrato invece il circuito dei moduli OSERDES2, che includono due registri per il latch dei dati utente a 4 bit che sono sincroni alla frequenza del segnale di clock proveniente dalla FPGA Fabric e dotati di abilitazione propria; gli ingressi D rappresentano i dati mentre quelli T il corrispondente segnale di enable del tri-state di uscita. Altrettanti registri a scorrimento, pilotati dal segnale di clock di trasmissione, implementano quindi il circuito per la serializzazione; il caricamento dei dati in tali registri è controllato da una logica di strobe dedicata in grado di supportare fattori di serializzazione 2:1, 3:1 e 4:1. Come in precedenza, due moduli OSERDES per applicazioni con uscita differenziale possono essere connessi in cascata, supportando così applicazioni con fattori di serializzazione fino a 8:1. I circuiti ISERDES2 ed OSERDES2 sono in grado di operare con data rate fino a 500 Mbps per fattori di serializzazione 1:2 e fino a 1080 Mbps in applicazioni 1:4 o 1:8 con ingressi/uscite differenziali di tipo LVDS.

Figura 2: schema del circuito ISERDES delle FPGA Spartan-6

DESERIALIZZAZIONE

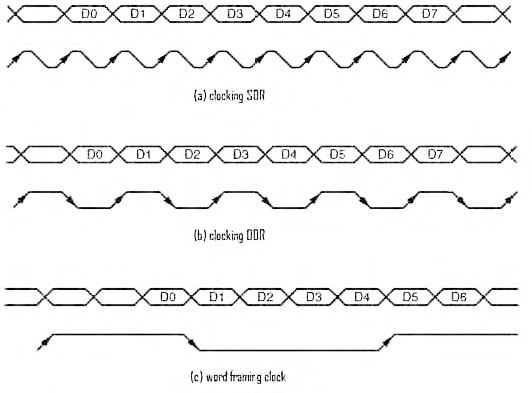

In generale, un protocollo di comunicazione si definisce source-synchronous se prevede la trasmissione del clock unitamente ai dati. Nelle applicazioni di trasmissione seriale di tipo source-synchronous, in particolare, si possono tipicamente trovare tre diversi schemi. Il più semplice, mostrato in Figura 3a, prevede la trasmissione di un clock di linea alla stessa frequenza dei dati. In alternativa (Figura 3b) il clock può avere frequenza pari alla metà di quella dei dati, secondo uno schema di clocking di tipo DDR (Double Data Rate). Nei casi più complessi (Figura 3c), il dato seriale commuta ad una frequenza multipla del clock, che rappresenta così principalmente un segnale di framing dei dati.

Figura 3: esempi di comunicazione seriale source-synchronous

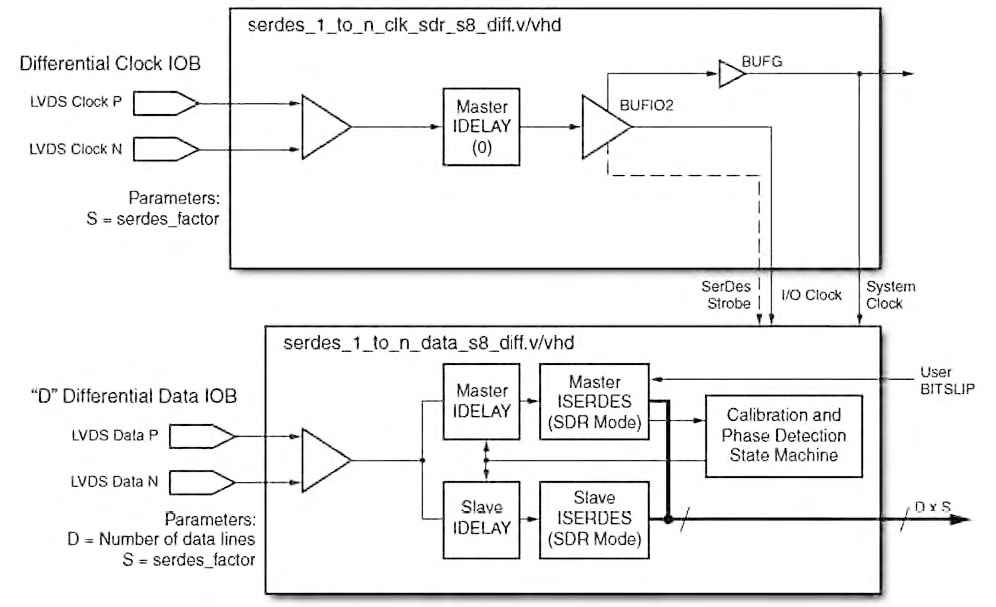

La Figura 4 mostra come implementare lo schema di ricezione di Figura 3a mediante dispositivi Xilinx Spartan-6 sfruttando le caratteristiche dei blocchi ISERDES2 descritti in precedenza. Il clock di ingresso è ritardato mediante IOBDELAY (per compensare i ritardi di propagazione interni alla FPGA dello stesso clock e della linea dati) e quindi distribuito mediante risorse dedicate al modulo ISERDES2 ed alla FPGA Fabric. La primitiva BUFIO2, in particolare, dispone di due uscite, di cui una è una replica del clock di ingresso che viene utilizzata per deserializzare i dati, mentre l’altra è ottenuta dividendo lo stesso per un fattore configurabile; il clock diviso viene utilizzato per risincronizzare nell’ISERDES2 il dato parallelo ricostruito e quindi clockare l’FPGA Fabric. Sia il BUFIO2 che il modulo ISERDES devono essere opportunamente configurati staticamente in funzione del rapporto di deserializzazione 1:n richiesto dalla specifica applicazione. In Figura 4 è mostrata, in particolare, la connessione in cascata dei due moduli ISERDES per applicazione, ad esempio, 8:1. In questo caso, con un clock di ricezione di 525 MHz (corrispondente ad un data rate di linea di 525 Mbps), il clock ricostruito per l’FPGA Fabric ha frequenza di 65.625 MHz.

Figura 4: deserializzazione con clocking SDR

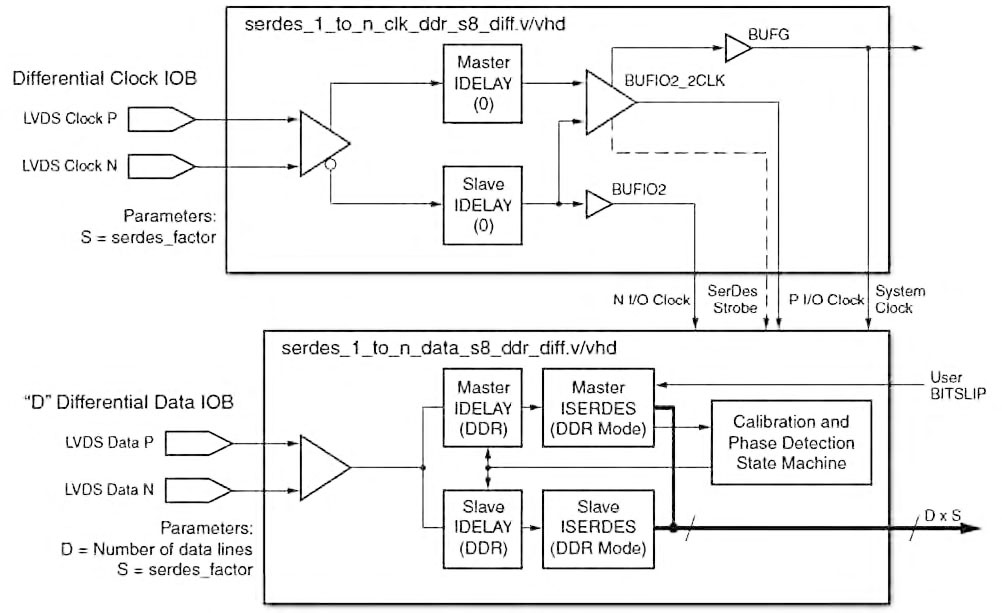

La Figura 5 mostra invece lo schema di principio della soluzione da adottare per implementare un'applicazione del tipo di Figura 1b. In questo caso il clock in ingresso è di tipo differenziale. I moduli ISERDES2 sono configurati in modalità DDR e clockati mediante repliche, opportunamente ritardate, delle linee positiva e negativa del clock di ingresso. Il clock per l’FPGA Fabric è quindi generato dalla primitiva BUFIO2_2CLK dividendo per un fattore n/2 lo stesso clock di ingresso.

Figura 5: deserializzazione con clocking DDR

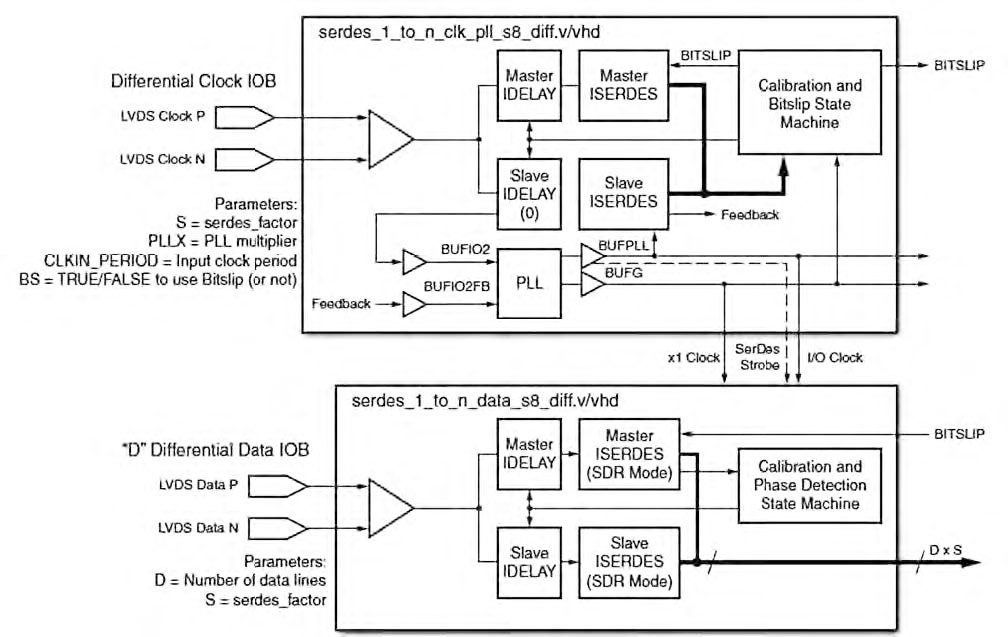

Ad esempio, con un clock di ingresso di 311 MHz (corrispondente ad un data rate di linea di 622 Mbps) ed un rapporto di serializzazione di 8:1, il clock ricostruito per l’FPGA Fabric è 77.75 MHz. Lo schema per implementare la soluzione di Figura 3c, infine, è mostrato in Figura 6. In questo caso, il clock per i circuiti ISERDES2 è generato mediante PLL, moltiplicando opportunamente il clock di ingresso. Una replica di questo è invece distribuita all’FPGA Fabric per la risincronizzazione dei dati paralleli. Il circuito implementa inoltre la funzionalità di BitSlip per la corretta ricostruzione dell’allineamento di parola nei dati ricevuti. Il clock di linea definisce la lunghezza di parola ma non determina univocamente tale allineamento.

Figura 6: deserializzazione con segnale di framing

SERIALIZZAZIONE

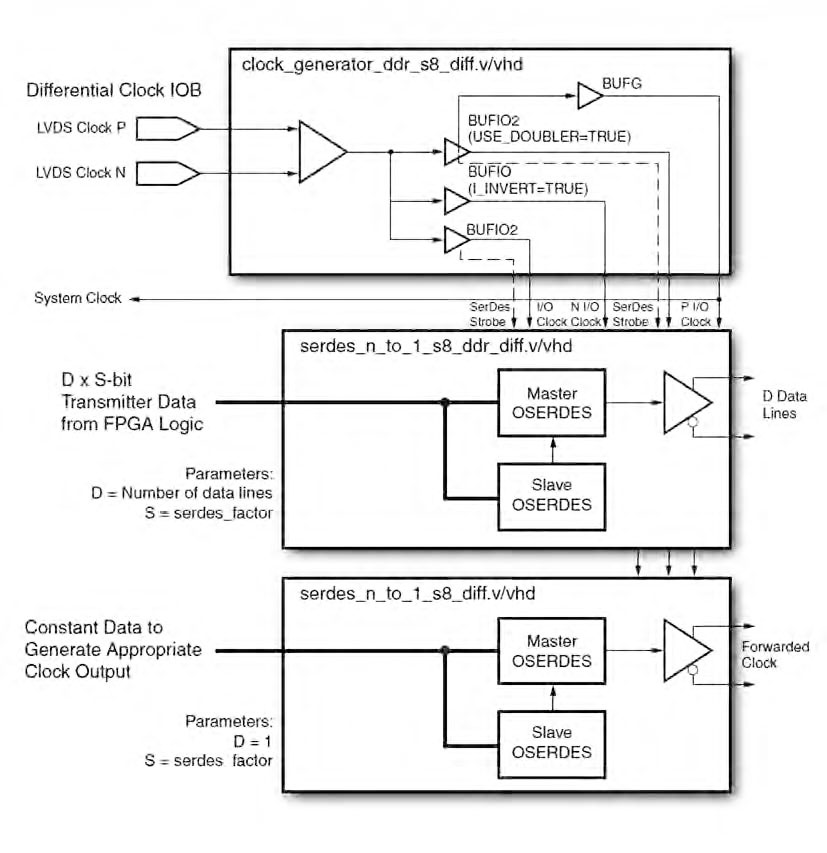

Come per i circuiti di deserializzazione, lo schema del serializzatore per applicazioni source-synchonous dipende dal tipo di applicazione specifica, ovvero dal formato dei dati e dal tipo di schema di clocking adottato. La Figura 7 mostra lo schema per un'applicazione di trasmissione dati seriali con forwarding di clock SDR/DDR; si assume che il clock di serializzazione sia generato da oscillatore esterno alla FPGA.

Figura 7: serializzazione dei dati e forwarding del clock

In questo caso, tale clock viene utilizzato per pilotare il circuito OSERDES2 in modalità SDR per la linea dati ma viene anche opportunamente diviso mediante il BUFIO2 (in funzione del rapporto di serializzazione scelto) per clockare l’FPGA Fabric. Il clock seriale viene quindi generato mediante un secondo circuito OSERDES2 avente pattern costante in ingresso; il circuito opera, a seconda della modalità di forwarding del clock scelta, in modalità SDR o DDR. Ad esempio, per un'applicazione con data rate di 622 Mbps e rapporto di serializzazione 8:1, disponendo di un clock di ingresso di frequenza di 622 MHz, l’FPGA Fabric è clockata a 77.75 MHz ed il pattern costante in ingresso all’OSERDES2 per il forwarding del clock è 10101010. Nel caso di forwarding di clock SDR, questo corrisponde effettivamente ad un clock di linea di 622 MHz; nel caso DDR, invece, produce un clock seriale di 311 MHz. Lo schema di Figura 7 può facilmente essere modificato qualora non si disponga di ingresso di clock esterno di frequenza pari a quella di trasmissione seriale. Nel caso in cui il clock disponibile sia di frequenza pari alla metà di quella richiesta, si può utilizzare un driver BUFIO2 accessorio e far lavorare anche l’OSERDES della linea dati in modalità DDR; in questo caso, tuttavia, sarà possibile implementare soltanto lo schema di forwarding del clock di tipo DDR. Più in generale, e qualora si intenda trasmettere clock di linea SDR, il clock di serializzazione può essere generato internamente alla FPGA moltiplicando opportunamente mediante PLL il clock d’ingresso disponibile.