Infineon ha sviluppato tempo fa una famiglia di dispositivi, AUDO che uniscono in un unico componente la potenza di calcolo dei DSP, l'efficienza dei processori con architettura RISC e la velocità dei microcontrollori. L'articolo descrive in dettaglio una sottocategoria di tale famiglia, indicati con la sigla TC1762.

I dispositivi della famiglia AUDO di Infineon sono micro ottimizzati per applicazioni in cui sono richiste elevate prestazione in real-time e capacità tipiche di un DSP, unite alla bassa latenza di interrupt e con la più elevata tolleranza ai guasti. I campi applicativi sono i più svariati e spaziano da automotive a telecom/datacom passando attraverso il controllo industriale (figura 1).

Figura 1: i campi di applicazioni del processori AUDO sono svariati. Automotive, controllo industriale, elaborazione ed memorizzazione dei dati, telecom/datacom, consumer sono solo alcuni esempi.

L’architettura TriCoreTM

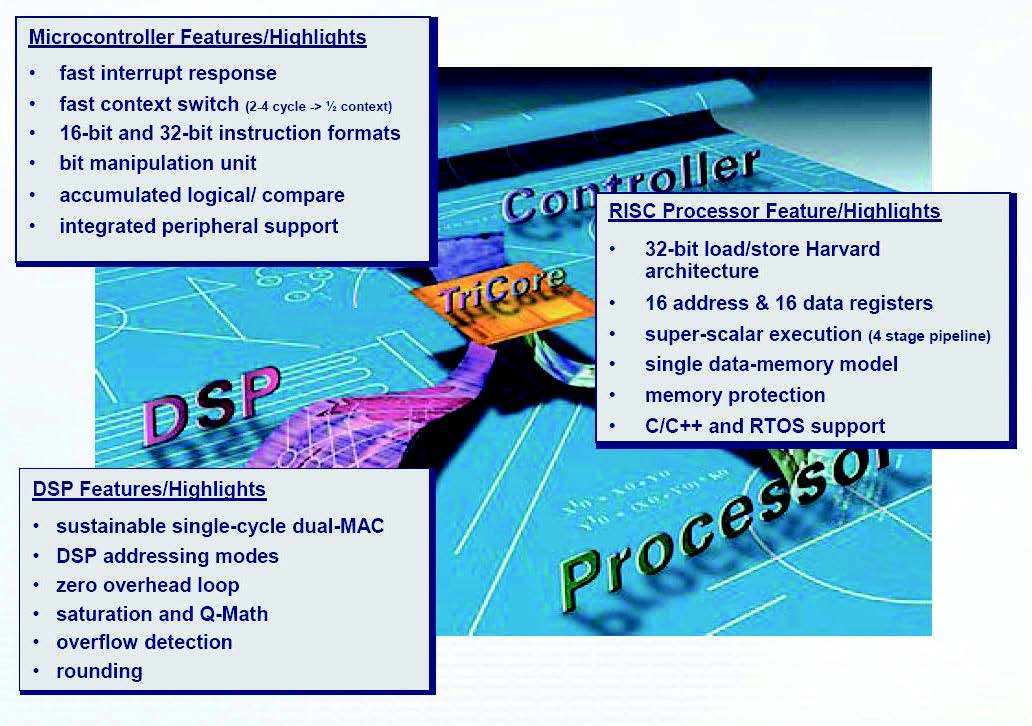

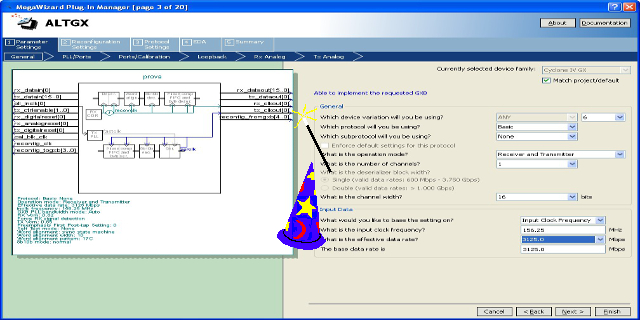

Con il termine TriCore Infineon si riferisce alla sua architettura di tipo superscalare, con risposta veloce agli interrupt, cost-sensitive ed un sistema real-time. Per applicazioni basate su FPGA è disponibile anche la relativa implementazione in linguaggio VHDL e Verilog. Questa strategia dovrebbe consentire (in breve tempo) ad Infineon di rendere la sua architettura un standard industriale. Quest’architettura riunisce in un solo modulo la potenza di tre componenti fondamentali di tutti sistemi embedded (figura 2):

➤ Controllore. Tra i vantaggi offerti da questo punto di vista: la risposta veloce agli interrupt, il formato delle istruzioni ottimizzato (16-bit e 32-bit) e il supporto di periferiche integrate che riduce l’area occupata su PCB.

➤ DSP. La possibilità di implementare molto semplicemente operazioni tipiche di DSP rende il micro TC1762 compatibile con tutti i task relativi all’elaborazione numerica del segnale.

➤ Processore RISC. L’architettura Harvard super-scalare permette la scrittura di codice C ottimizzato. Il micro TC1762 dispone di due bus indipendenti, come si evince anche dalla figura 3.

Figura 2: il microcontrollore della famiglia AUDO TC1762 racchiude in se la flessibilità e potenza di un controllore, di un processore RISC e di un DSP.

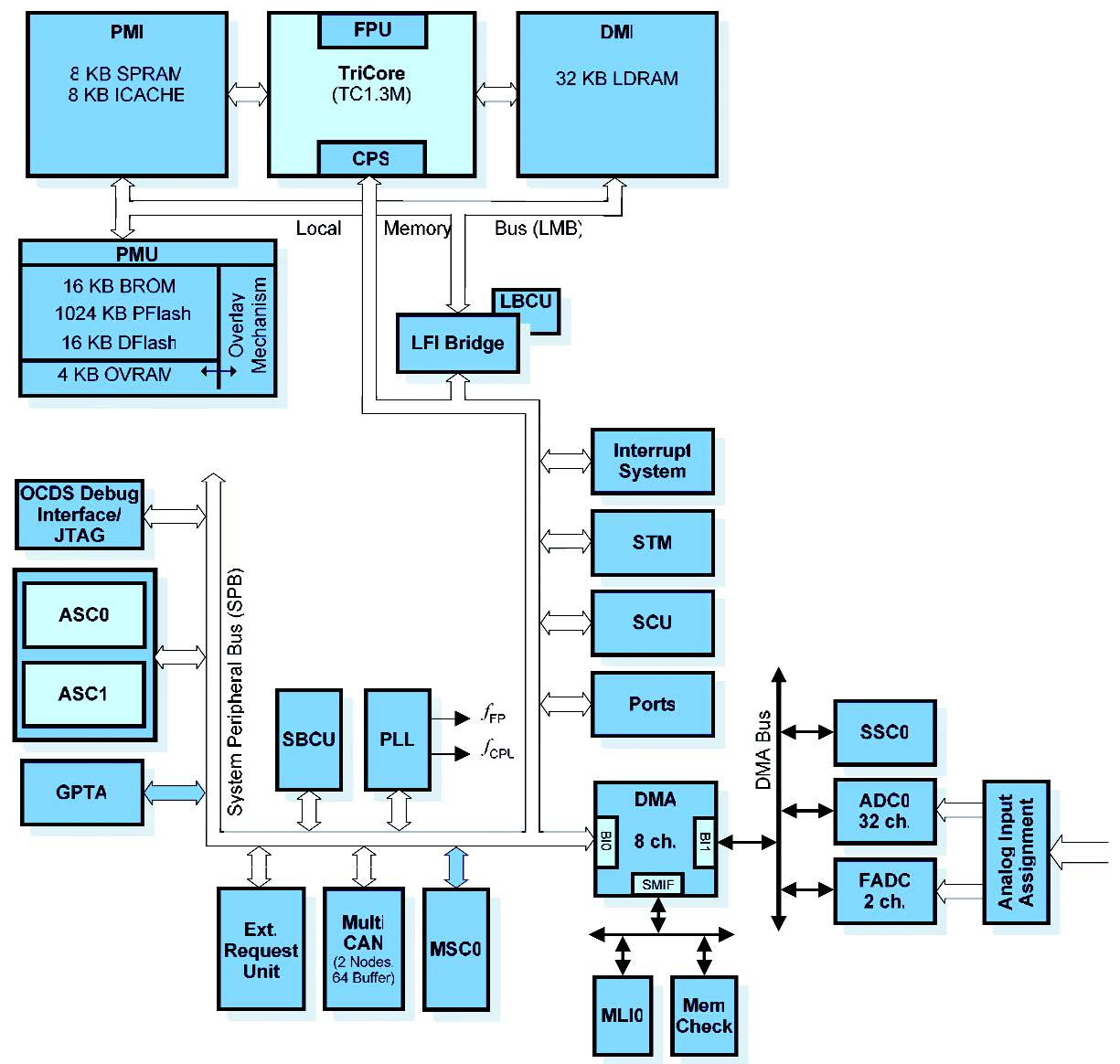

Figura 3: schema a blocchi del micro TC1762 della famiglia AUDO.

Local Memory Bus (LMB) System Peripheral Bus (SPB) Esiste, inoltre, un terzo bus che costituisce il punto d’unione dei primi due: FPI. Il primo ha il compito di collegare le risorse locali della CPU per i dati e le istruzioni estratte dalla ROM. Il bus della memoria locale interconnette l’unità di memoria e quella funzionale come CPU e PMU (Program Memory nit). Lo scopo è quello di evitare i colli di bottiglia, separando le unità ad elevata velocità con quelle a più bassa velocità: il concetto è simile a quello adottato da Intel che separa il suo chipset in NorthBridge e SouthBridge. Il bus LMB è di tipo sincrono con supporto di differente grandezza dei blocchi trasferiti (8, 16, 32 e 64bit). Il punto d’intersezione dei due bus è rappresenta dal bus FPI. In questo modo la CPU può accedere anche al bus SPB e quindi a tutte le periferiche on-board, come gli ADC o il modulo CAN. Il bridge FPI è progettato in modo da sostenere elevati data rate, ad esempio, con un frequenza operativa di 80MHz ed un bus dati di 32bit, è garantito un throughput di 320Mbyte/s. Questo significa, tra l’altro, un riduzione nella latenza di azione delle diverse periferiche.

Controller DMA

Il controller DMA (evidenziato in figura 3) ha lo scopo di garantire il trasferimento dati dalla sorgente alla destinazione (generalmente la memoria) senza l’intervento della CPU, la quale nel frattempo può essere utilizzata per altre operazioni. Ogni sotto-blocco dispone di otto canali DMA. Il bus switch consente di collegare una periferica al bus FPI o a quello DMA.

Interfacce di comunicazione seriali

Per implementare la comunicazione tra il TC1762 ed altre periferiche esterne o altri processori, sono disponibili due tipi di interfacce di comunicazione seriale:

➤ ASC (Asynchronous/Synchronous Serial Interface)

➤ SSC (High-Speed Synchronous Serial Interface)

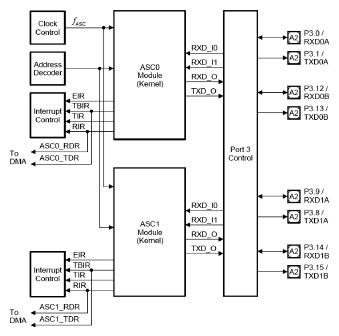

La figura 4 mostra una vista globale dei blocchi funzionali e delle interface dei due moduli ASC0 e ASC1.

Figura 4: Schema a blocchi dell’interfaccia seriale Sincrona/Asincrona

Essi forniscono una comunicazione seriale che supporta la modalità full-duplex asincrona e half-duplex sincrona. In quest’ultimo caso, i dati sono trasmessi e ricevuti attraverso un clock generato internamente dal micro. In modalità asincrona, si possono selezionare trasferimento a 8 o 9bit, generare i bit per il controllo di parità e di stop. È predisposto anche un meccanismo per distinguere i byte di dati da quelli di indirizzo: questa funzione è utile quando si realizza un bus di dispositivi seriali che necessitano di indirizzamento. L’interfaccia SSC supporta sia la modalità full che half-duplex fino a 40MBaud con una frequenza operativa di 80MHz. Trattandosi di una comunicazione sincrona essa necessita di un clock: questo può essere generato sia internamente (Master mode) che ricevuto da un dispositivo master (Slave mode). Ampiezza dei dati, direzione dello shift register, polarità del clock e fase sono tutti programmabili via firmware. In questo modo è possibile la comunicazione con tutti i dispositivi SPI-compatibili.

Modulo MultiCAN

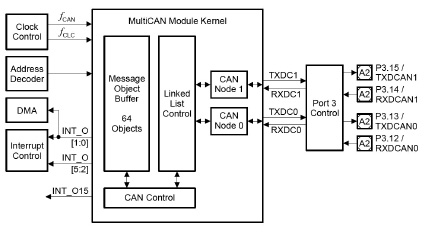

Il modulo CAN (mostrato in figura 5) contiene due nodi indipendenti con funzionalità Full-CAN.

Figura 5: Schema a blocchi del modulo MultiCAN

La trasmissione e ricezione dei frame CAN è gestita secondo le specifiche CAN ver 2.0B. Ogni nodo può ricevere e trasmettere frame con identificatore ad 11bit e frame estesi con identificatore 29bit. La temporizzazione è estratta dal modulo di controllo del clock (fCAN) e permette di raggiungere velocità fino a 1Mbit/s.

Interfaccia Micro Link

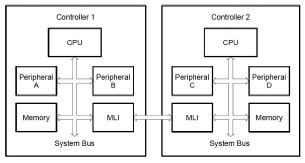

I TC1762 sono dotati di un’interfaccia particolare detta MLI (Micro Link serial bus Interface) che permette lo scambio di dati tra micro a 32bit della famiglia AUDO senza l’intervento della CPU. Si tratta di comunicazione seriale ad alta velocità di tipo sincrono. La figura 6 mostra una tipica connessione tra due micro tramite questa interfaccia.

Figura 6: Tipica interconnessione tra due micro della famiglia AUDO tramite interfaccia MLI

Il modulo di conversione analogica

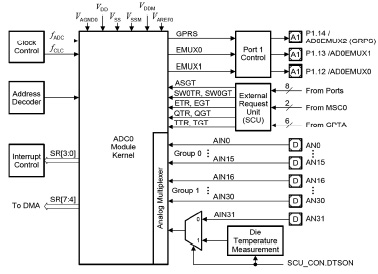

La figura 7 mostra la vista globale del modulo ADC con i vari blocchi funzionali e le interfacce.

Figura 7: Schema a blocchi del modulo di conversione analogicodigitale.

Questo modulo ha 16 canali di acquisizione. Un multiplexer analogico permette di selezionare tra 32 ingressi analogici (identificati con i pin AN0… AN31). La risoluzione di conversione può essere selezionata tra 8bit, 10bit o 12bit.

Il power management

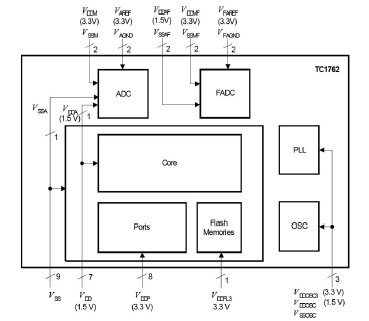

Il sistema per la gestione del consumo di potenza del TC1762 permette di configurare via firmware diverse modalità operative a cui corrispondono differenti consumi di corrente. In generale, la tale gestione è ottenuta attraverso la combinazione di varie tecniche: stop del clock della CPU, stop o riduzione dei clock delle singole periferiche. Run Mode, il sistema è a pieno regime. Tutti i clock e le periferiche sono abilitati. Idle Mode, il clock della CPU è disabilitato, in attesa di una condizione di ritorno alla modalità run. Tutte le periferiche restano alimentate e con il clock attivo.Sleep Mode, il clock è distribuito solo a quelle periferiche abilitate a funzionare in modalità sleep. Il TC1762 dispone di diverse linee di alimentazione per differenti classi di dispositivi, come schematizzato in figura 8:

➤ le linee a tensione 1.5V sono utilizzate per il core, l’oscillatore e il convertitore.

➤ le linee a tensione 3.3V sono riservate per gli I/O, memoria Flash, oscillatore e per il riferimento di tensione del convertitore A/D.

Figura 8: Linee di alimentazione del TC1762.

Ho valutato questi processori per studio personale e per arricchire il CV.

Purtroppo pero’ l’evaluation board meno cara che ho trovato e’ intorno ai 600 euro,