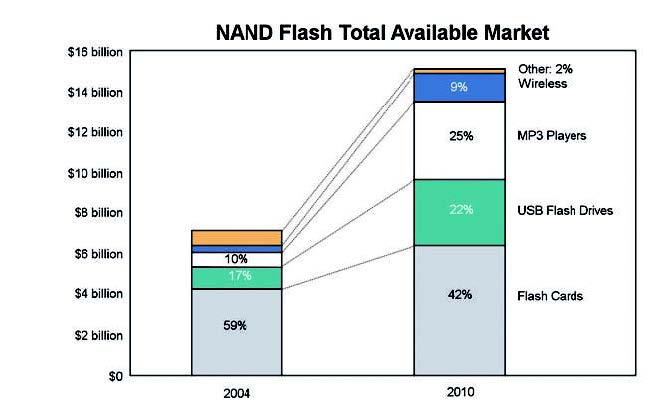

Le memorie flash di tipo NAND occupano un segmento di mercato sempre più rilevante nel settore embedded grazie al loro costo e all’offerta in termini di capacità di memoria. Le loro prestazioni, permettono inoltre di coprire soluzioni orientate all’elettronica di consumo.

Le soluzioni orientate verso il mondo embedded, almeno fino a qualche anno fa, utilizzavano proposte basate su memorie flash di tipo NOR, ma da diversi anni le richieste si sono spostate verso tecnologie di tipo NAND per sfruttare la loro alta densità, il costo abbastanza contenuto insieme alle ottime prestazioni. La figura 1 pone in evidenza le possibili applicazioni delle memorie NAND per tre differenti segmenti di mercato, quali dispositivi USB, MP3 player e macchine fotografiche digitali.

Figura 1: applicazioni delle memorie NAND.

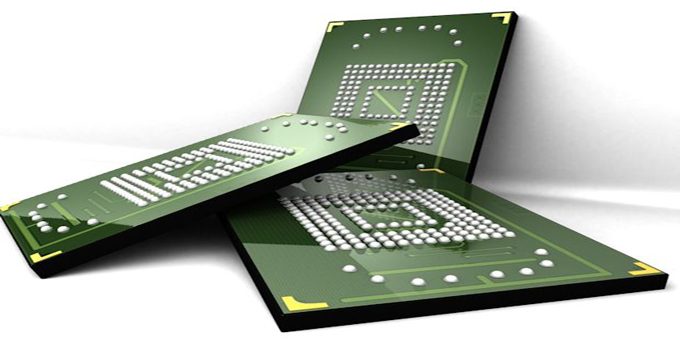

La Toshiba è stata la casa che ha realizzato le prime memorie NAND; in questo articolo vi proponiamo le memorie di casa Micron corredate da un driver scritto in VHDL per la loro corretta gestione.

Nand e nor: due tecnologie a confronto

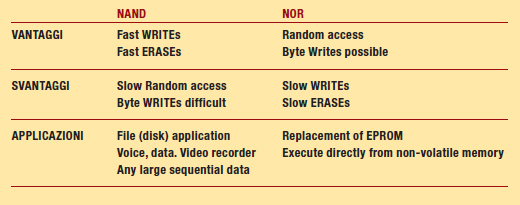

La tabella 1 pone in evidenza i diversi argomenti che sostengono le tesi a favore, o meno, di una e dell’altra tecnologia.

Tabella 1 – NAND Flash vs NOR Flash

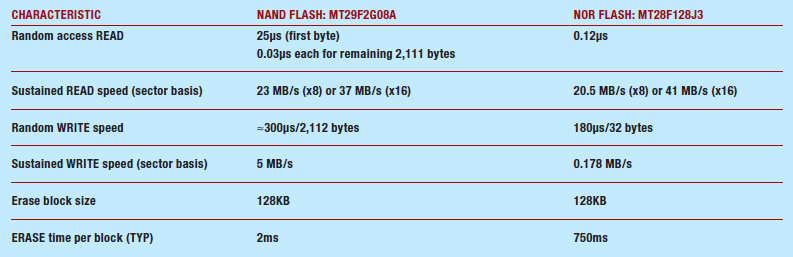

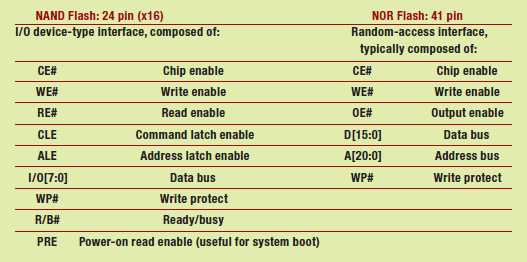

Vediamo che le memorie NAND rispondono in maniera efficace alle applicazioni orientate alla gestione delle informazioni organizzate secondo una struttura a file o sequenziale. Al contrario, le memorie NOR offrono maggiori prestazioni per le applicazioni ad accesso casuale. Inoltre, le memorie NAND offrono prestazioni migliori per le operazioni di scrittura e cancellazione, mentre le NOR offrono maggiori capacità nella scrittura a byte. Vediamo che la tabella 2 mostra le differenze, in termini di prestazioni, tra queste due soluzioni tecnologiche di casa Micron, mentre la tabella 3 mette in evidenza le loro differenze hardware.

Tabella 2 – comparazione tra NAND e NOR

Tabella 3 – differenze hardware tra Nand e Nor

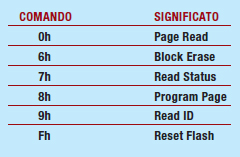

Nelle applicazioni di tipo embedded le soluzioni basate su memoria NOR sono tra quelle più richieste. Oggi, un numero sempre più alto di processori dispongono di un’interfaccia verso le memorie NAND e permettono di fare il boot direttamente da questi dispositivi, senza utilizzare le memorie NOR. I processori di questo tipo sono sempre più utilizzati e richiesti perché permettono di rispondere alle esigenze di costo, spazio e alle sempre più stringenti richieste di memoria. Le memorie Flash richiedono, ad ogni comando, il segnale CE# a un livello logico basso, i segnali CLE e ALE devono essere asseriti insieme al segnale di write enable WE#. Fino a quando il dispositivo risulta occupato (busy), non possono essere inviati comandi alla flash a meno di un reset e di un read status. La tabella 4 mostra i possibili comandi previsti dalla memoria Flash.

Tabella 4 - comandi della NAND Flash

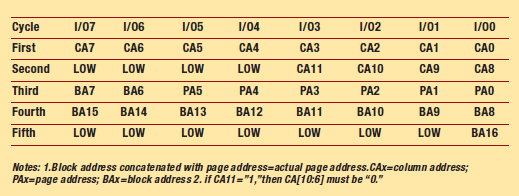

Tabella 5 – SLC NAND Flash addressing Scheme

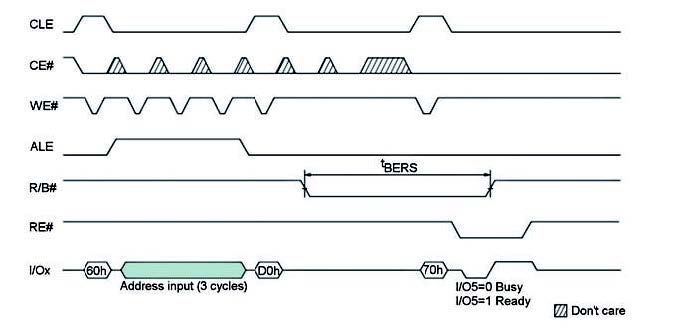

L’operazione, per esempio, di erase, block erase, utilizza il comando 60h per cancellare un intero blocco di 64 pagine, o 128Kb. Dalla figura 2 si nota che per inviare correttamente un comando di erase è necessario utilizzare il segnale WE#, con comando 60h, congiunto a CLE.

Figura 2: operazione di erase.

Vediamo poi i successivi tre cicli sugli indirizzi con il segnale ALE asserito per ogni byte della linea d’indirizzo. Questi tre cicli di indirizzo sono i cicli più significativi (come messo in evidenza in tabella 4), ed include l’indirizzo di blocco e di pagina. I sei bit della parte bassa del terzo ciclo di indirizzo sono ignorati, mentre solamente la porzione di indirizzo di blocco dei tre byte più significativi è utilizzata. Una volta che l’indirizzo è completamente acquisito, è necessario spedire la seconda parte (il comando del ciclo 2) con il valore D0h: questo è clockato con WE#, mentre CLE è asserito. Il secondo comando conferma l’operazione di erase e il dispositivo rimane occupato per circa 2ms. Una volta che il dispositivo completa l’operazione, questo diventa pronto per processare una successiva operazione. Il comando “read status” può essere attivato in ogni momento, anche quando la Flash è occupata durante l’operazione di erase. Il microprocessore, o il controller, può monitorare il dispositivo attraverso il comando read status.

Driver per nand flash

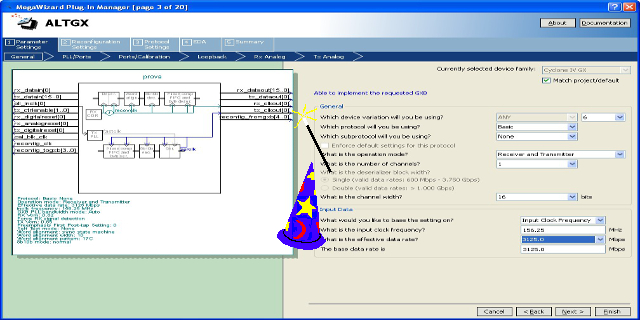

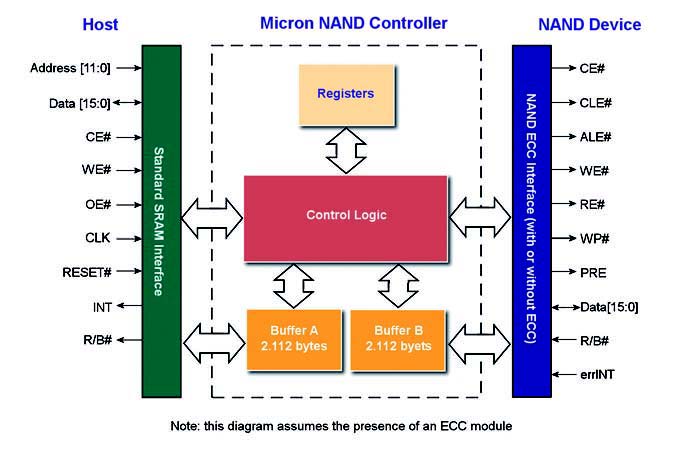

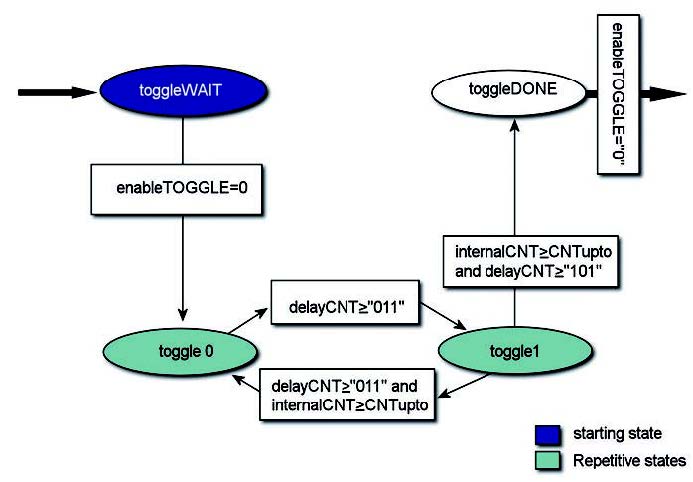

La figura 3 mostra il diagramma a blocchi della sezione controller della memoria NAND. L’architettura è organizzata in modo che il modulo di controllo del timing utilizzi solo due registri di 5 bit (CE#, CLE#, ALE, WE# e RE#) per fare il toggle dei segnali della NAND.

Figura 3: Flash controller

I registri sono acceduti dal main control logic che sovrintende al timing. L’interfaccia della Flash della Micron è implementata secondo il meccanismo del memory mapped. L’interfaccia verso la memoria è implementata con una serie di registri VHDL. Quando l’host scrive verso gli indirizzi dei registri interni, il codice VHDL scrive a degli registri specifici. Non tutti i bit dei registri sono utilizzati. La logica di controllo è divisa in due processi VHDL (figura 4).

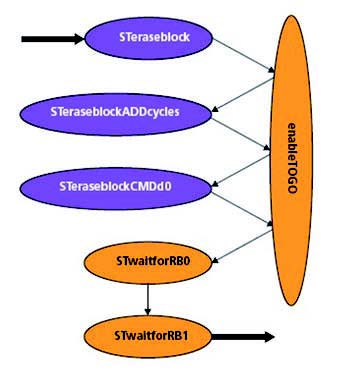

Figura 4: Erase, macchina a stati.

Il timing control logic genera un clock di 60ns con un duty cycle del 33,33% (per esempio, 40 ns a livello basso e 20ns alto). Il duty cycle è generato utilizzando un contatore che conta da 0 a 5. Questo delay counter incontra il segnale basso quando il contatore è 0,1,2 o 3 e alto quando incontra il valore 4 o 5. In questo modo pilota il primo registro outputVEC1 per 40ns e il secondo, outputVEC2, per 20 ns. Quando si vuole eseguire un’operazione di read della pagina, la parte host scrive il blocco e l’indirizzo della pagina ai registri localizzati a 0xFF4, 0XFF5 e 0xFF6. Dopo aver caricato gli indirizzi, l’host deve scrivere 0x00 verso il registro 0XFFA per eseguire il comando di read. In questo modo, la logica di controllo legge la pagina specificata dall’indirizzo nel registro e lo pone nel buffer. La logica di controllo inizia un ciclo di interrupt e cambia il buffer. Un’operazione status read è simile all’operazione read ID (read identification). La scrittura del valore 70h al registro 0XFFA (registro di comando) inizia uno status read. Dopo l’interrupt lo stato può essere letto dal registro 0xFF9. La logica di controllo monitora l’indirizzo al quale il controller sta scrivendo. Quando l’indirizzo diventa 0xFFA, la logica di controllo legge il bus dati per controllare il comando. In base al comando, si sposta la sequenza dei dati. Vediamo come svolge alcuni comandi, nel nostro caso erase e read status. Per compiere l’operazione di erase sono necessari cinque stati della nostra macchina a stati, vale a dire:

» STeraseblock. È il primo comando (valore esadecimale 60) e permette di attivare la macchina a stati, ed è composto da due sequenze verso la memoria flash.

» STeraseblockADDcycles. Aspetta tre address cycle per determinare il blocco da cancellare.

» STeraseblockCMDd0. E’ il secondo comando (valore esadecimale D0) e permette di iniziare l’operazione di erase.

» STwaitforRB0. Aspetta che la linea R/B# vada ad un livello logico basso: questo permette di determinare l’operazione di erase, in corso o meno.

» STwaitforRB1. In questo stato si aspetta che il segnale R/B# vada ad un valore logico alto. La transizione di stato permette di determinare la fine della procedura di cancellazione.

Figura 6: Address Control Logic States.

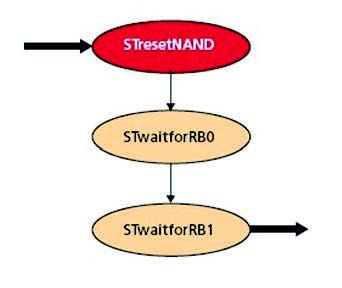

Figura 5: reset, macchina a stati

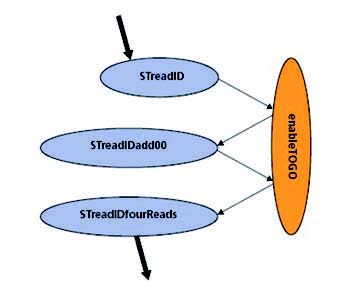

Gli stati R/B# usano il registro NEXTtonextST per determinare il prossimo stato. Al contrario, l’operazione di reset del dispositivo comporta la gestione di tre stati: STresetNAND, STwaitforRB0 e STwaitforRB1. Nel dettaglio lo stato STresetNAND è utilizzato per aspettare il comando 0xFF che dà luogo all’operazione di reset. I successivi due stati si devono preoccupare di concludere le operazioni gestendo il segnale R/B#; infatti, lo stato STwaitforRB0 aspetta che R/B# vada ad un livello logico basso (è in corso l’operazione di reset), successivamente, con STwaitforRB1, controlla la transizione verso un valore logico alto (l’operazione corrente si è completata con successo). Per concludere possiamo vedere come implementare l’operazione di Read Identification, o Read ID. Anche in questo caso l’operazione di read ID richiede la gestione di tre stati: STreadID, STreadIDadd00 e STreadIDfourReads. Nel dettaglio lo stato STreadID fa partire la macchina a stati per gestire la funzionalità attraverso il comando 90h. I successivi due stati si devono preoccupare di concludere le operazioni. A questo riguardo, lo stato STreadIDadd00 aspetta l’indirizzo 00h sul bus: questo fa parte della sequenza Read Id. Successivamente, con STreadIDfourReads si leggono i quattro byte di dati che contengono le informazioni identificative del dispositivo.

Figura 7: ReadID, macchina a stati.