VHDL e Verilog sono due linguaggi HDL utilizzati per descrivere modelli hardware. Anche se presentano alcune somiglianze, ciascuno ha caratteristiche proprie. Quali sono le differenze tra questi due approcci metodologici? L’obiettivo di questo articolo è di dare una risposta a questa domanda.

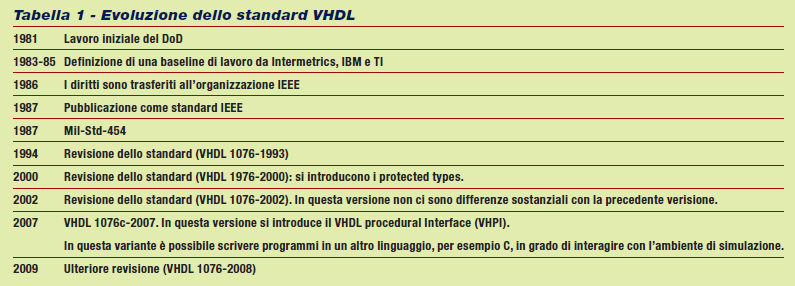

Il linguaggio VHDL è utilizzato per la sintesi e la simulazione di circuiti digitali ed è uno degli standard utilizzati per descrivere l’hardware. Nel 1987 questo linguaggio è stato adottato come standard dall’Institution of Electrical and Electronics Engineering, o IEEE, e siglato come VHDL-87. In realtà, del VHDL se ne parla già dagli anni ’80 da un progetto del DoD, dipartimento della Difesa USA, con il nome VHSIC, o Very High Speed Integrated Circuits e, in seguito, VHDL, o VHSIC Hardware Description Language. Il lavoro del DoD rispondeva all’esigenza di definire un linguaggio con capacità descrittive di modelli digitali in grado di lavorare su qualsiasi simulatore e assicurare l’indipendenza dalla tecnologia e dalla metodologia di disegno. Come nella prassi di ogni standard, anche il VHDL ha avuto processi di revisione e aggiornamenti, per esempio la variante VHDL-93. Il linguaggio VHDL non è la sola proposta; infatti, esistono in commercio, e adottati anche come standard, altri linguaggi per la descrizione dell’hardware. La tabella 1 mostra l’evoluzione nel tempo del linguaggio VHDL. Esiste per esempio l’ABEL (Advanced Boolean Equation Language) supportato da Xilinx, l’AHDL (Altera Hardware Description Language) supportato invece da Altera.

Tabella 1 - Evoluzione dello standard VHDL

La soluzione alternativa che riscuote il maggior successo è senz’altro il Verilog. Questo nasce da un lavoro della Cadence e poi regolamentato da IEEE nel dicembre 1995 in IEEE Std. 1364-1995. Il linguaggio ha poi subito una revisione nel 2001, IEEE Std. 1364-2001, e nel 2005, ma con minori apporti. Accellera ha sviluppato un nuovo standard, il SystemVerilog, che estende il Verilog. Come il Verilog anche la variante SystemVerilog nel 2005 acquisì lo status di standard (1800-2005).

Verilog

Come il VHDL, anche il Verilog è un linguaggio di programmazione orientato alla descrizione di strutture hardware (HDL) digitali. Il Verilog è utilizzato per descrivere sistemi digitali a differenti livelli: switch level, transistor level, gate level, porte logiche elementari, e Register Transfer Level (RTL), scambio dati tra registri. Il Verilog e’ stato introdotto nel 1985 da Gateway Design System Corporation e poi commercializzato da Cadence come Verilog-XL. Dal 1990 esiste la Open Verilog International che ha permesso la standardizzazione IEEE del linguaggio nel 1995 e la realizzazione di altri simulatori (VeriWell, VCS, VeriBest e altri). La tabella 2 pone in evidenza l’evoluzione del Verilog.

Tabella 2 - evoluzione di Verilog

Un progetto è di solito composto da diversi file HDL, ogni file, poi, può contenere uno o più moduli. Per poter simulare il progetto c’e’ bisogno di un modulo di test che permetta di applicare gli stimoli al circuito e che ne verifichi il comportamento (con stampe, salvando segnali grafici, o altro). In VHDL si utilizza un file di testbench. I listati 1 e 2 mostrano due esempi scritti in Verilog: la sintassi è differente rispetto al linguaggio VHDL anche se concettualmente rimangono pressoché identici.

// Simple 4-1 mux module mux4 (sel, A, B, C, D, Y); input [1:0] sel;//2-bit control signal input A, B, C, D; output Y; reg Y; // target of assignment always @(sel or A or B or C or D) case (sel) 2’b00: Y = A; 2’b01: Y = B; 2’b10: Y = C; 2’b11: Y = D; endcase endmodule

| Listato 1 - Esempio di programma Verilog |

dimodule

MUX2_1(out, a, b, sel);

output out;

input a, b, sel;

reg out; // Commento

always @(sel or a or b)

begin

if( sel == 0 )

out <= a;

else

out <= b;

end

/* Altro commento */

endmodule

| Listato 2 - Altro esempio di modulo Verilog |

Possiamo individuare alcuni elementi: definizione del tipo reg, la presenza di un blocco procedurale, l’uso di beginend, l’uso di strutture di controllo if-else o case, l’assegnazione <=, i commenti // e /* */, la presenza delle istruzioni di chiusura di module. Il listato 3 invece mostra come può essere simulato un programma Verilog: possiamo notare le differenze e i punti comuni con il testbench.

`timescale 1ns/10ps module test; reg A, B, selector; wire sig_out; MUX2_1 mux_instance(sig_out, A, B, selector); initial // inizializzazione al tempo 0 begin A = 0; B = 0; selector = 0; $shm_open(”waves.shm”); $shm_probe(”AS”); end initial // vettori di test begin #50 A = 1; #50 selector = 1; #50 B = 1; #50 $shm_close; $finish; // termina end endmodule

| Listato 3 - Simulazione |

LOAD_SWAP: process (Clock) begin if rising_edge(Clock) then if (Reset = ‘0’) then A_Hold <= (others => ‘0’); B_Hold <= (others => ‘0’); elsif (Load = ‘1’) then A_Hold <= A; B_Hold <= B; else if (A_lessthan_B = ‘1’) then A_Hold <= B_Hold; B_Hold <= A_New; else A_Hold <= A _New; end if; end if; end process LOAD_SWAP;

| Listato 4 - Esempio con VHDL |

always @(posedge Clock) begin: LOAD_SWAP if (Reset) begin A_Hold = 0; B_Hold = 0; end else if (Load) begin A_Hold = A; B_Hold = B; end else if (A_lessthan_B) begin A_Hold = B_Hold; B_Hold = A_New; end else A_Hold = A_New; end

| Listato 5 - Esempio con Verilog |

Tipi di dato

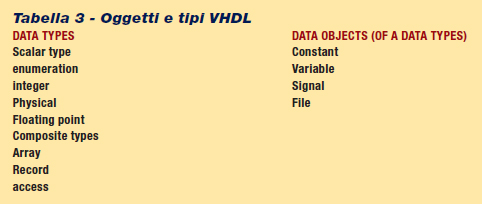

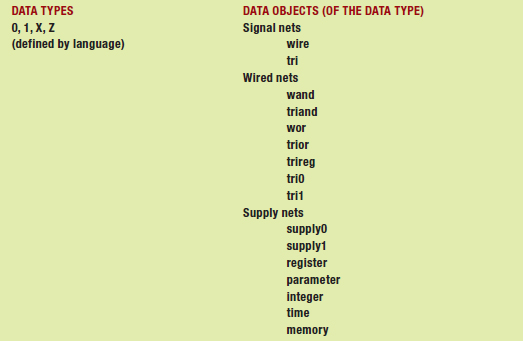

In VHDL possono essere utilizzati tipi definiti dall’utente, o user defined, ed è anche possibile utilizzare funzioni dedicate di conversione per convertire oggetti da un tipo all’altro. Il Verilog, al contrario, non permette al progettista di definire tipi propri, ma, in compenso, attraverso il continuous assignment: consente di modellare la logica combinatoria e cambiare nome ai segnali (anche per i 3-state). Questo può essere fatto ricorrendo al tipo wire che permette la connessione tra porte di varie entita’. Esistono diversi tipi wires: wand (wired and), wor (wired or) e tri (tristate). Il Verilog permette poi di utilizzare il tipo reg: questi partono dall’interno di un processo. Le tabelle 3 e 4 mostrano le differenze tra questi due linguaggi dei tipi e oggetti permessi.

Tabella 3 - Oggetti e tipi VHDL

Tabella 4 - Oggetti e tipi Verilog

Costrutti di alto livello

In VHDL esistono diversi modi per costruire un modello di alto livello rispetto al Verilog. Possono essere utilizzati, per esempio, tipi di dati astratti insieme alle asserzioni previste dal linguaggio VHDL:

» istruzione di package per aiutare il riuso dei componenti;

» istruzioni di configurazione per definire la struttura del nostro disegno;

» istruzioni di tipo generico per modelli generici con la possibilità di attualizzarle in base alle singole esigenze.

Tutti queste istruzioni sono poi utili anche in fase di sintesi. Viceversa, anche se esiste la possibilità in Verilog di parametrizzare il modello, non esiste qualcosa di equivalente come prevede il VHDL. Infatti, una dichiarazione di una entity, in VHDL, permette di descrivere il progetto di un I/O che può prevedere e includere parametri che possono personalizzarla. La dichiarazione di una entity è analoga ad un simbolo schematico che descrivere i collegamenti di un componente. Con la dichiarazione si specifica il nome: in questo modo può essere referenziata nel disegno architetturale. Così, per descrivere un multiplexer con quattro ingressi, due linee di selezione e un’uscita di quattro bit:

entity MUX is port (

a, b, c, d: in std_logic_vector(3 downto 0);

s: in std_logic_vector (1 downto 0);

x: out std_logic_vector (3 downto 0));

end MUX;

Una descrizione di un’architettura permette di mettere in evidenza la funzionalità, struttura e il contenuto di una design entity. Ogni dichiarazione di entity deve avere la sua architecture body. Il VHDL permette di scrivere il disegno utilizzando differenti approcci. Un’architettura può contenere qualsiasi combinazione possibile: behavioral, structural o dataflow. In questo modo è possibile descrivere un progetto con differenti livelli di astrazione. Il Verilog ha un approccio differente. Per prima cosa, il Verilog utilizza il costrutto module: è attraverso module che il Verilog riesce a descrivere la funzionalità o la struttura di un progetto, oltre a descrivere le porte, o linee di comunicazione, con gli altri moduli. In Verilog la parte dichiarativa è utilizzata per definire i registri e i parametri utilizzati all’interno di un modulo. Le istruzioni per mettono di specificare la funzionalità e la struttura del progetto. L’esempio che mostriamo è un modulo con due porte in ingresso e due di uscita. Tutte le porte hanno la dimensione di un bit, il modulo contiene due di istruzioni di assegnamento che ne descrivono il comportamento. Così:

module ESEMPIO (A, B, C, D);

//Nome del modulo

input A, B; // dichiarazione output C, D; // dichiarazione assign C = A ^ B; // Istruzione assign D = A & B; // Istruzione endmodule // End of module

Librerie

Nel linguaggio VHDL una libreria è un repository che contiene costrutti quali entities, architectures e packages particolarmente apprezzati per gestire diversi progetti. In Verilog non esiste il concetto di libreria come in VHDL, ma, in ogni caso, è possibile modellare librerie attraverso i moduli.

Gestioni di disegni complessi

Il linguaggio VHDL permette di utilizzare strumenti che possono fornire un valido aiuto per gestire progetti di grandi di mensioni. Il concetto di configuration, generate, generic e package possono senza dubbio essere utilizzati a questo scopo. Al contrario, in Verilog non esistono istruzioni di questo tipo.

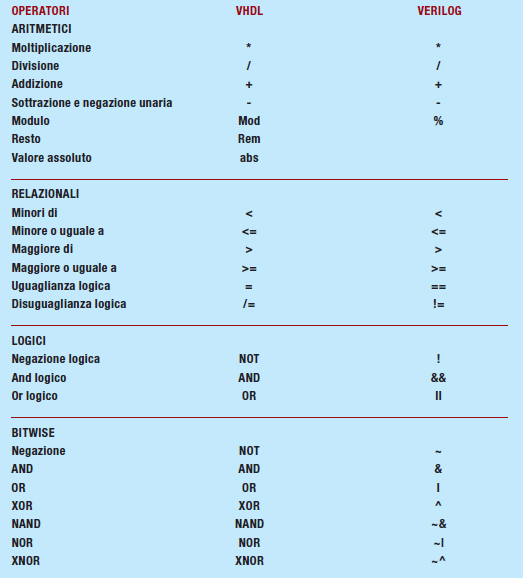

Operatori

La maggior parte degli operatori presenti in VHDL lo sono anche in Verilog, In realtà, il linguaggio Verilog presenta delle estensioni interessanti. La tabella 5 mostra alcune differenze.

Tabella 5 - Gli operatori tra VHDL e Verilog

Cicli di controllo

Il linguaggio VHDL utilizza una varietà interessante di strutture di controllo. Per esempio, supporta il ciclo loop, whileloop, for-loop, exit, next. Il Verilog, invece, permette di gestire il ciclo repeat, for e while. Per esempio, in Verilog:

repeat( 5 )

begin

i = i + 1;

$display(”i = %0d”, i);

End

O ancora:

for(i=0; i<10; i=i+1)

begin

$display(”i = %0d”, i);

end

Strutture condizionali

Il linguaggio VHDL permette di definire e utilizzare strutture condizionali if-thenelse/elsif (con priorità), case, selected assign, assign di tipo condizionale. Viceversa, il Verilog utilizza if-else (con priorità), case, casex e l’operatore condizionale utilizzato in assegnamenti concorrenti.

Modello comportamentale

I listati 1 e 2 mettono in evidenza il ruolo dell’istruzione Verilog always. La parola chiave always identifica un blocco procedurale e insieme ad initial rappresentano due proposte interessanti di Verilog. Il blocco procedurale initial viene eseguito una sola volta, mentre, al contrario, i blocchi always vengono messi in esecuzione fino a quando dura il processo. Non esistono particolari restrizioni sull’uso di questi blocchi, in pratica ogni definizione di modulo può contenere uno o più blocchi initial e/o always. I blocchi always aiutano il progettista a modellare il comportamento di reti logiche e sequenziali e la loro esecuzione non è sequenziale, ma sono schedulati in parallelo. Un blocco di tipo initial è messo in esecuzione, tipicamente, nei moduli di test. Le operazioni che sono racchiuse nel blocco begin/end di un blocco procedurale sono eseguite in maniera sequenziale. Si utilizza, poi, il tipo reg per dichiarare le variabili in un blocco procedurale. L’analoga istruzione in VHDL è senz’altro rappresentata da process. I listati 4 e 5 mostrano le due soluzioni possibili.

Controllo temporale

In Verilog per controllare la variazione del nostro modello hardware sono disponibili due costrutti. Con ‘#’ è possibile controllare il ritardo, cioè l’esecuzione è ritardata a seconda delle unità espresse o unità temporali, per esempio:

#10 A = 0; // dopo 10 nsec

Il valore dell’unità temporale è identificata con la direttiva ‘timescale, così:

`timescale 1ns/10ps // unita’ di 1 nsec, con precisione di 10 psec

Con ‘@’ si vuole interrompere l’esecuzione fino all’occorrenza di un determinato evento:

@( B ); // aspetta una variazione di B

Il controllo temporale in VHDL viene invece svolto ricorrendo alle istruzioni AFTER e WAIT.

Conclusione

Abbiamo visto in quest’articolo alcune differenze tra i due linguaggi HDL. L’argomento è ampio e non può esaurirsi in un articolo, anche se abbiamo dato alcune indicazioni di massima. In successivi articoli approfondiremo i diversi aspetti.

Grazie dell’articolo. Aspetto i prossimi