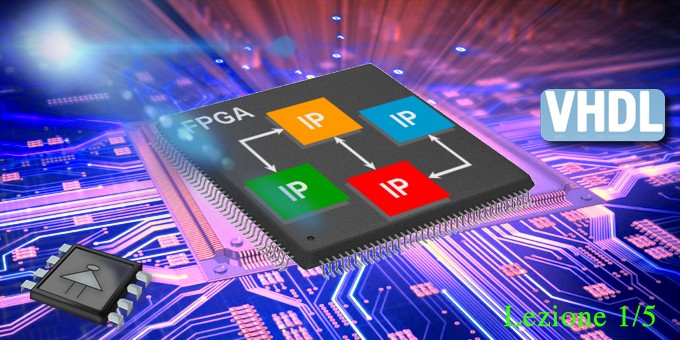

La necessità di prestazioni sempre superiori e di consumi sempre più ridotti ha spinto il mondo dell'elettronica ad un uso sempre più massivo di dispositivi quali FPGA. Tali dispositivi devono la loro fama per la peculiarità di essere programmabili o meglio configurabili grazie a linguaggi come il VHDL o il Verilog, anche se sono linguaggi abbastanza complessi. Questi sono dedicati alla descrizione dell'hardware e consentono quindi di specificare il comportamento di circuiti elettronici sia semplici (ad esempio una funzione booleana o un sommatore) sia molto complessi come i processori. Con questo articolo iniziamo un corso sul VHDL muovendo i primi passi nello sviluppo di un generico componente. Il corso affronterà tutti i concetti base e la metodologia di sviluppo che si nasconde dietro un linguaggio estremamente complesso ma allo stesso tempo molto potente. Nella prima lezione vi fornirò una panoramica generale sul linguaggio, sulla struttura di uno progetto, sui tool che possono essere utilizzati. Nelle successive lezioni si entrerà nel dettaglio dello sviluppo delle funzionalità di un componente. Il corso terminerà con le basi per lo sviluppo di componenti più complessi e la simulazione degli stessi.

Cenni storici

Il termine VHDL è l'acronimo di VHSIC Hardware Description Language e nasce in ambito militare (nel contesto del progetto VHSIC della difesa americana) a seguito dell'esigenza di dotarsi di uno strumento universale per la descrizione dell'hardware sviluppato. Nel 1987 l'istituto IEEE adotta il VHDL come linguaggio di descrizione standard e viene rilasciato ufficialmente come VHDL-87. Successivamente, nel 1993, vengono apportate leggere modifiche e viene rilasciato come VHDL-93.

Caratteristiche peculiari

Uno degli scopi principali del VHDL è quello di realizzare circuiti digitali per dispositivi programmabili (FPGA e CPLD) o per ASIC. Ma c'è da puntualizzare che non tutti i costrutti del VHDL sono sintetizzabili. Può sembrare prematuro dire questo nella prima lezione, ma come vedremo durante il corso, sarà importante capire cosa è sintetizzabile, ossia realizzabile, e cosa no.

In genere quando si parla di VHDL si fa riferimento quasi sempre alla "programmazione" delle FPGA anche se in realtà può essere utilizzato con dispositivi quali CPLD o ASIC. Ma quali differenze ci sono tra FPGA, CPLD e ASIC? Iniziamo con il CPLD, acronimo di Complex PLD, è un dispositivo realizzato tramite blocchi PLD (Programmable Logic Device). I PLD sono dispositivi la cui funzione logica può essere programmata semplicemente configurando la matrice delle interconnessioni tra gli input e gli ouput. I CPLD, più complessi, sono un insieme di PLD in cui devono essere programmati i singoli blocchi e anche le interconnessioni tra i vari blocchi. I dispositivi ASIC (acronimo di application-specific integrated circuit) sono circuiti che escono di fabbrica già configurati con le funzionalità che devono svolgere. Tale scelta consente di ottenere prestazioni eccellenti in termini di velocità e di consumi energetici ma contro non possono essere più riprogrammati. La loro funzionalità vengono sempre definiti con linguaggi quali VHDL o Verilog. I principali produttori mettono a disposizione prodotti con diverse tecnologie in modo tale da offrire al progettista sempre la soluzione più adatta alle proprie esigenze (a tal proposito vi consiglio la lettura di questo articolo presente in archivio).

Prima di affrontare la sintassi del VHDL precisiamo che il linguaggio non è case-sensitive, ossia maiuscole e minuscole non creano differenze. Le parole chiave del linguaggio non sono tantissime ma non possono essere utilizzate se non per gli scopi prefissati. Per aumentare la leggibilità del codice scritto per la sintassi e per gli esempi dimostrativi adottiamo le seguenti "buone" regole:

Regola#1. tutte le parole chiave del VHDL le scriviamo in MAIUSCOLO.

Regola#2. tutti i nomi (componenti, segnali, architetture, etc) inizieranno sempre in minuscolo. Le maiuscole saranno usate all'interno del nome per diversificare le parole, oppure sarà usato il simbolo underscore (es: "nomeComponente" oppure "nome_componente").

Regola#3. In VHDL possono essere scritti dei commenti e ne faremo un utilizzo abbondante per aumentare la leggibilità delle istruzioni. In VHDL i commenti sono introdotti da due trattini “--“.

Affrontiamo ora nel dettaglio l'iter che segue la progettazione di un nuovo componente hardware. Il processo di design inizia con la descrizione in linguaggio VHDL del componente. Tale descrizione sarà riportata in un file con l'estensione ".vhd". Al termine della descrizione può essere eseguita la fase di sintesi. Tale processo attua una conversione dalla descrizione VHDL alla descrizione RTL (register transfer level). La rappresentazione RTL è un modo molto comodo in fase di progettazione funzionale per descrivere il comportamento del componente facendo riferimento a registri, segnali e operazioni logiche sul flusso di dati. Di fatto, il processo di sintesi produce in uscita anche una netlist con porte elementari (porte logiche e registri) interconnesse tra loro.

Terminato il processo di sintesi, viene eseguito un processo di ottimizzazione. Questo può seguire principalmente due opzioni selezionabili dall'operatore: ottimizzazione per velocità oppure ottimizzazione per area. La selezione della modalità desiderata comporta un processo di semplificazione o comunque riadattamento della netlist in termini delle prestazioni richieste. Terminato il processo di ottimizzazione si ottiene una descrizione dell'hardware completa a tal punto che può essere utilizzata già effettuare le simulazioni e verificarne il corretto funzionamento. Le attività di simulazione a questo livello consentono di verificare il corretto funzionamento del sistema sviluppato anche in termini di temporizzazioni in modo tale da poter valutare se intervenire in altro modo nella strategia di ottimizzazione. L'ultima operazione da attuare prima del caricamento sui dispositivi fisici è il Place&Route. Questa fase dipende strettamente dal componente [...]

ATTENZIONE: quello che hai appena letto è solo un estratto, l'Articolo Tecnico completo è composto da ben 2329 parole ed è riservato agli ABBONATI. Con l'Abbonamento avrai anche accesso a tutti gli altri Articoli Tecnici che potrai leggere in formato PDF per un anno. ABBONATI ORA, è semplice e sicuro.

Un corso molto interessante sul VHDL. Vi consiglio di seguire tutte e 5 le puntate estremamente interessanti 😉

Sono interessato al corso e mi serve per rivangare tutte le reminiscenze affrontate durante il corso di Architettura e Progettazione digitale all’università. Seguo anche il testo “VHDL progetto di sistemi digitali” di Mark Zwolinski e volevo approfittare per chiedere info riguardanti le FPGA e l’hardware occorrente per effettuare qualche test di programmazione.

Grazie.

Se vuoi qualcosa di economico per fare piccoli passi ti consiglio di cercare qualche demo-board basata su Xilinx CoolRunner-II. Il chip non è una FPGA ma una CPLD. Non potrai chiedere tantissimo ma puoi farti un’infarinatura generale con meno di 50€. Se hai esigenze più specifiche, devi valutare tra le innumerevoli demo-board, ma in quel caso ti consiglio di valutare delle schede Altera che sono più complete a prezzi più competitivi.

Volevo sapere se era in programma un corso per utilizzo di Vivado per FPGA della xilink.

Grazie

Salve Salvatore,

per ora non abbiamo in programma un corso per l’utilizzo di Vivado per FPGA della xilink, ma terremo conto della richiesta.

Grazie