Questo articolo presenta nel dettaglio l’IGLOO nano STARTER KIT di ACTEL/Microsemi, dal costo contenuto, per FPGA, che potrà essere usato come banco prova per molte sperimentazioni di progetti disponibili gratuitamente. Questa scheda è stata presentata molti anni fa ed è interessante notare come le tecnologie embedded si sono evolute nel corso del tempo.

Descrizione generale

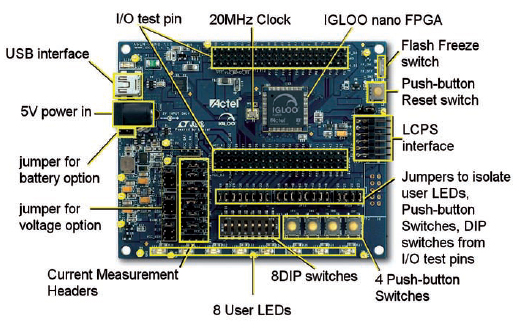

La scheda di sviluppo (figura 1) monta direttamente saldata una FPGA della famiglia IGLOO (la versione ultra low power della famiglia Proasic3) a cento pin VQFP.

Figura 1: la scheda di sviluppo Igloo nano.

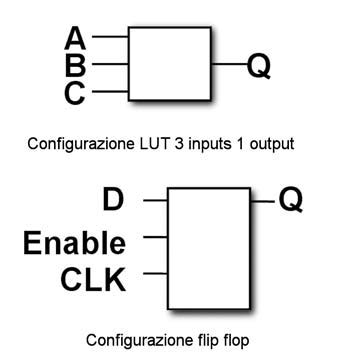

Per la maggior parte di coloro che non sono interessati specificatamente alle applicazioni a basso consumo, informiamo che la struttura di base della famiglia IGLOO è identica a quella della Proasic3 e i componenti delle due famiglie sono pin to pin compatibili. Pertanto qualsiasi progetto provato con questo KIT potrà girare, senza sostanziali cambiamenti strutturali, sul medesimo componente della Proasic3, fatta eccezione di una maggiore velocità operativa di quest’ultima. Sul KIT IGLOO viene fornito come taglio un 250Kgate, che significa avere a disposizione 6.144 Flip Flop o 6.144 porte combinatorie a tre ingressi e una uscita (figura 2).

Figura 2: le configurazioni possibili con il kit Igloo nano.

Poiché la famiglia IGLOO ha il suo punto di forza nei minimi consumi, la sezione di alimentazione è stata curata in modo particolare, dando la possibilità di scegliere varie tipologie di alimentazione attraverso ponticelli richiudibili. Le porte di I/O della FPGA sono riportare quasi completamente sui connettori J4-6-7-8 tipo strip a passo 2,54 mm, quindi comodi per potersi interfacciare. Quattro pin non sono riportati all’esterno: in particolare due sono usati per la seriale UART to USB CP2102 (pin 16 e 19), uno è il clock di sistema (pin 15) e l’ultimo è il reset di scheda (pin 10).

Sezione di alimentazione

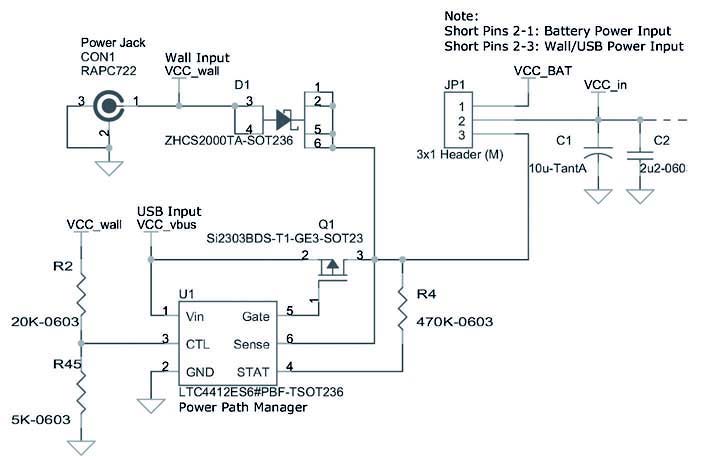

La sezione di alimentazione è stata volutamente progettata con numerose opzioni, per permettere tutte le prove possibili e l’utilizzo di varie sorgenti, compresa una eventuale batteria esterna (figura 3).

Figura 3: alimentazione dello starter kit.

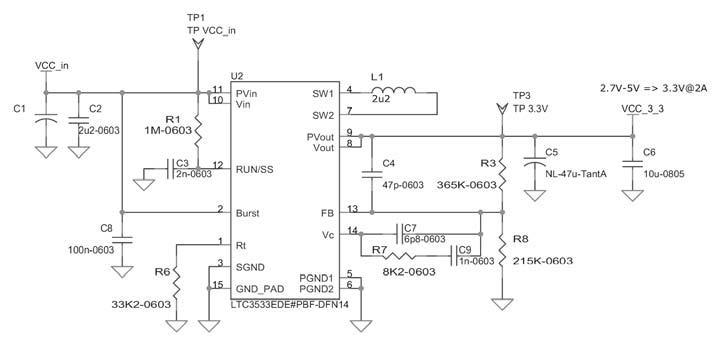

Sono disponibili le seguenti sorgenti di alimentazione: esterna utilizzando un AC/DC con presa Jack(CON1), diretta usando l’alimentazione della connessione USB(CON2), oppure da presa di batteria esterna (J1). Per tutte le sorgenti la massima tensione ammessa è di 5,5V. Nel KIT è stato inserito un LTC4412, che è un circuito in grado di rilevare la presenza della alimentazione esterna, se inserita su presa jack e selezionarla in alternativa al 5V, in arrivo dalla porta USB. A valle di questa selezione automatica, è presente il connettore JP1 (Header a tre vie), che con ponticello fra pin 2-3 seleziona il 5V dell’ alimentazione esterna (o della USB), mentre chiuso fra pin 1-2 permette l’uso dell’alimentazione della batteria (o comunque di un’ulteriore sorgente a 5V) inserita sul connettore J1 (positivo pin1 GND pin 2). La sorgente di alimentazione selezionata arriva al regolatore di scheda LTC3533 (figura 4), che è uno switching sincrono di tipo Buck Boost, in grado di erogare fino a 2A e qui configurato per fornire il 3,3V di scheda.

Figura 4: il regolatore di tensione.

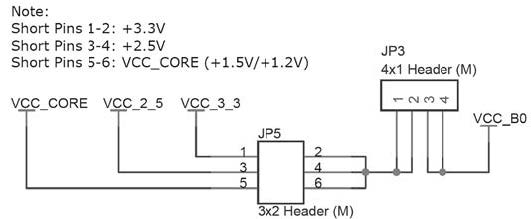

Poiché il chip IGLOO può essere alimentato come core sia a 1,2V sia a 1,5V, i progettisti della ACTEL hanno inserito un regolatore a bassa caduta lineare LT3080(U4), che fornisce le due tensioni. La selezione per generare 1,5V oppure 1,2V viene effettuata tramite il ponticello a tre vie JP2, che in posizione 1-2 chiuso, permette la generazione della tensione a 1,5V, mentre posizionando il ponticello su 2-3 consente l’erogazione della 1,2V. Massima corrente ammessa per questo regolatore è di 0,5A. Infine, per coloro che volessero usare gli I/O a 2,5V, è stato inserito un ulteriore LT3080(U3), che dal 3,3V genera un 2,5V, con corrente massima 0,5A. Dato che il componente dispone per i pin di I/O di quattro banchi separati, ognuno in grado di poter lavorare con una propria alimentazione, per il banco di I/O 0 e 1 e per l’alimentazione della porta JTAG necessaria alla programmazione sono stati inseriti dei connettori di selezione. Nel dettaglio (figura 5) guardando il banco 0 attraverso il connettore Header JP5 è possibile scegliere se alimentarlo a VCC CORE (che sarà 1,2V o 1,5V), VCC 2,5V oppure VCC 3,3V.

Figura 5: la selezione dell’alimentazione attraverso i jumper.

L’uscita di questa selezione passa da un ulteriore connettore JP3, che ha la funzione di sezionatore, per permettere la misura della corrente assorbita dal banco stesso. Tale descrizione vale anche per il banco 1 e la porta JTAG. Il banco 2 e 3 non dispongono di selezioni e sono alimentati sempre a 3,3V. Anche questi banchi, così come la VCC CORE e la VCC PUMP (l’alimentazione per la programmazione della FPGA), sono forniti di ponticelli sezionatori utili alle misure di corrente.

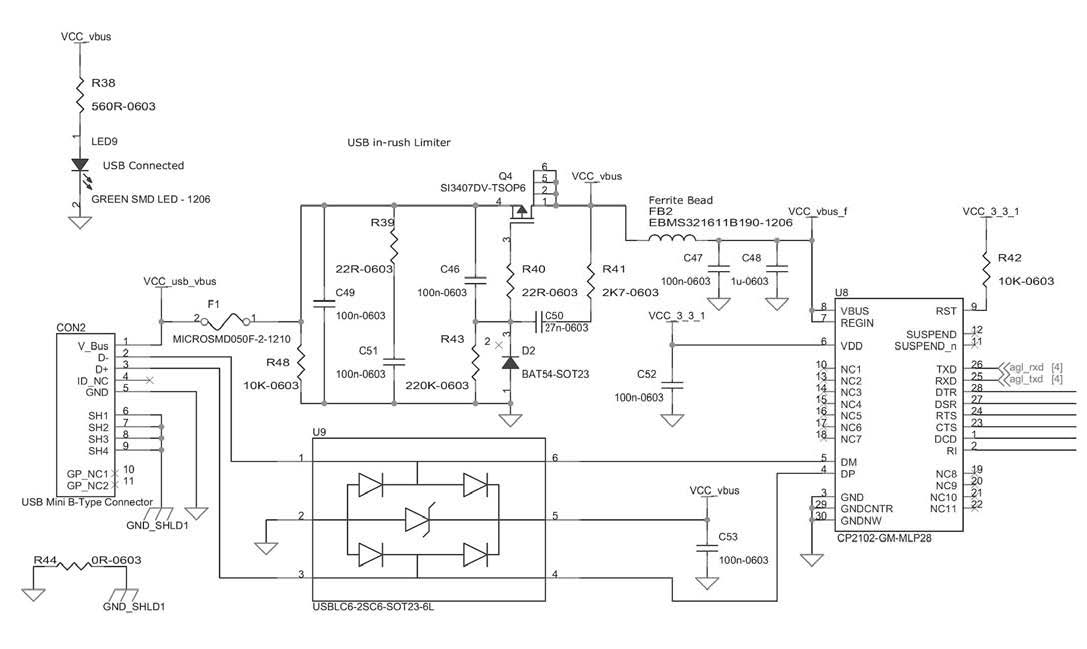

Porta USB

La porta USB fornita può essere utilizzata (come spiegato nella sezione alimentazione) come sorgente per alimentare completamente la scheda. Indipendentemente da questa scelta, essa è collegata al chip di conversione da USB a seriale CP2102 (figura 6).

Figura 6: il convertitore USB/seriale per la connessione della scheda al PC.

Il CP2102 supporta lo standard USB 2.0 full speed a 12 Mbit/s e può essere configurato via PC per uscire in asincrono verso la FPGA con un baud rate da 300 a 1Mbit/s, con dati, parità e numero di stop bit, anch’essi programmabili. Per una sperimentazione di questa sezione è utile ricordare che nella suite tools Libero 8.5, fornita insieme al KIT, troverete e potrete utilizzare gratuitamente la IP UART, per poter dialogare con il CP2102, così come è stato proposto nel demo fornito con il KIT. Come ultimo dettaglio di questa sezione, vi facciamo notare la presenza di un led di tipo SMD LED9, che si accende in presenza di alimentazione in arrivo dalla porta USB.

Led e Switch

Per poter facilmente effettuare diverse prove, sono stati inseriti sulla scheda led e switch di vario tipo. Una porta di otto led ( LED1…LED8) è collegata e disponibile sul connettore JP13, formato a sua volta da otto ponticelli. A ponticello aperto il relativo pin della FPGA andrà esclusivamente sul connettore di espansione J7, mentre a ponticello chiuso piloterà anche il led ad esso associato. Uno zero logico in uscita dalla FPGA provvede all’accensione del led. Il dip-switch SW5 a otto vie in condizione ON, forza i relativi pin della FPGA a zero logico e viene collegato fisicamente a essa attraverso i ponticelli JP14. Infine i pulsanti SW1-2-3 e 4 sono normalmente aperti, con chiusura a zero logico e si posso connettere alla FPGA, chiudendo i ponticelli del connettore JP15.

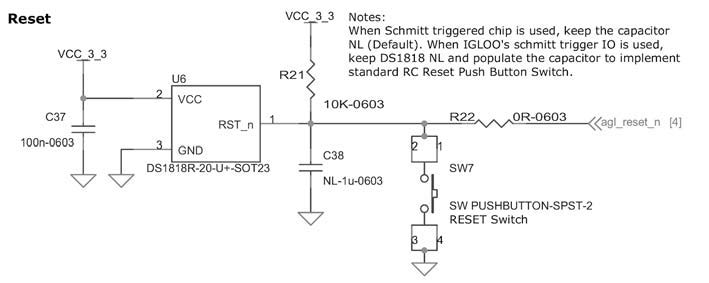

Funzione di Reset, Clock e Flash Freeze

La funzione di Reset e supervisione di alimentazione viene gestita dal DS1818R-20, che effettua il reset (portando la sua uscita a livello basso), quando l’alimentazione scende sotto 2,5V (figura 7).

Figura 7: la funzione di Reset e supervisione di alimentazione viene gestita dal DS1818R-20.

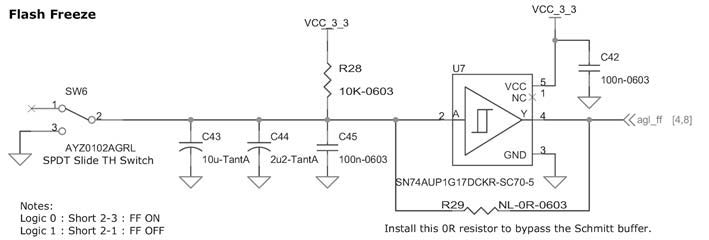

L’uscita reset è di tipo open collector, per cui è stato collegato su di essa un pulsante SW7, che premuto forza tale uscita a zero logico. Questa funzione è interna alla scheda e non è disponibile sui connettori di espansione. Il clock di scheda è fornito da un oscillatore quarzato da 20Mhz (Y1), alimentato a 3,3V e collegato al pin 15 della FPGA. Anch’esso non è portato sui connettori di espansione. Ricordiamo che le FPGA della serie IGLOO e Proasic3 sono fornite di PLL interno, per cui da questa frequenza di base, potrete generare fino a tre frequenze interne nella FPGA, per poterle usare nelle varie applicazioni. La funzione Flash Freeze è specifica ed esclusiva per i componenti della famiglia IGLOO. Essa infatti permette, portando un pin dedicato della FPGA a livello logico zero, l’attivazione della funzione Freeze, che congela il componete nella condizione logica detenuta all’istante (figura 8).

Figura 8: la funzione Freeze.

Pertanto i registri interni manterranno il valore caricato, i pin di output rimarranno nello stato logico definito al momento del freeze e il PLL interno andrà in power down automaticamente. Il tempo necessario alla messa in freeze del componente è di 1µs e il consumo in questa condizione della FPGA è di soli 2 µW. Esiste ed è supportata dalla funzione di libreria del Tool di sviluppo, la possibilità di condizionare la messa in stato di freeze del componente, non solo dallo stato logico del pin, ma anche dall’OK, in arrivo da una sezione logica interna della FPGA, configurabile in fase di sviluppo. In questo modo il progettista ha modo e tempo di settare la condizione di riposo degli eventuali registri, oppure di stati macchina interni e infine gli output di scheda. Gli I/O possono essere programmati in modo da poter scegliere quale sia la loro condizione in stato freeze. Le condizioni consentite sono: mantenimento del valore logico al momento del freeze, posizionamento in stato tri-state oppure weak pull up/weak pull down.