I requisiti di un sistema di alimentazione per FPGA esaminati dal punto di vista del progettista di sistema in termini di linee di tensione di alimentazione e di livelli di corrente, sequenza di applicazione delle tensioni, e caratteristiche di start-up.

La Xilinx Virtex™-5 e l’Altera Stratix® III sono famiglie di FPGA avanzate basate su un core da 65-nm che riunisce varie piattaforme ed è disponibile in varie tipologie di velocità, fattori che consentono di ottenere un elevato livello di prestazioni e di flessibilità. In questo articolo si discute dei requisiti di un sistema di alimentazione per FPGA esaminati dal punto di vista del progettista di sistema in termini di linee di tensione di alimentazione e di livelli di corrente, sequenza di applicazione delle tensioni, e caratteristiche di start-up. Di seguito viene presentata la soluzione per un sistema di alimentazione basato sui dispositivi LM1771 e LM3880, che si distingue per le elevate prestazioni, la densità di potenza e l’efficienza.

Le Necessità di Alimentazione delle FPGA

Le FPGA Virtex-5 o Stratix III richiedono generalmente almeno due differenti tensioni di alimentazione. La tensione per l’alimentazione del core di Virtex-5, denominata VCCINT, è di 1,0V±50mV, mentre quella del core Stratix III, denominata VCCL, può essere scelta tra 0,9V±40mV e 1,1V±50mV. In funzione dello standard di I/O che si deve implementare. La tensione di alimentazione di I/O per le Virtex-5, VCCO, può variare tra 1,14V e 3,45V. In modo analogo, per la famiglia Stratix III la tensione di alimentazione dell’I/O, VCCIO, può variare tra 1,14V e 3,15V, consentendo di interfacciare sistemi che operano a 1,2V, 1,5V, 1,8V, 2,5V e 3,0V. In aggiunta a queste tensioni, Xilinx dispone di una linea di alimentazione ausiliaria dedicata alle risorse di clock dell’FPGA, VCCAUX, che richiede una tensione di 2,5V±5%. Altera definisce linee di alimentazione aggiuntive dedicate alle sezioni analogiche e digitali del PLL, ai pre-driver di I/O, agli ingressi differenziali di clock, ecc... Le caratteristi che del sistema di alimentazione prevedono che vengano maneggiate elevate correnti durante il transitorio di accensione, che si riducono a valori decisamente inferiori durante il funzionamento normale. La rampa di accensione per le varie linee di alimentazione deve essere compresa tra 0,2ms e 50ms per la Virtex-5, mentre per la Stratix III i valori sono compresi tra 0,1ms e 100.0ms.

Criteri di Progettazione dell’Alimentatore per FPGA

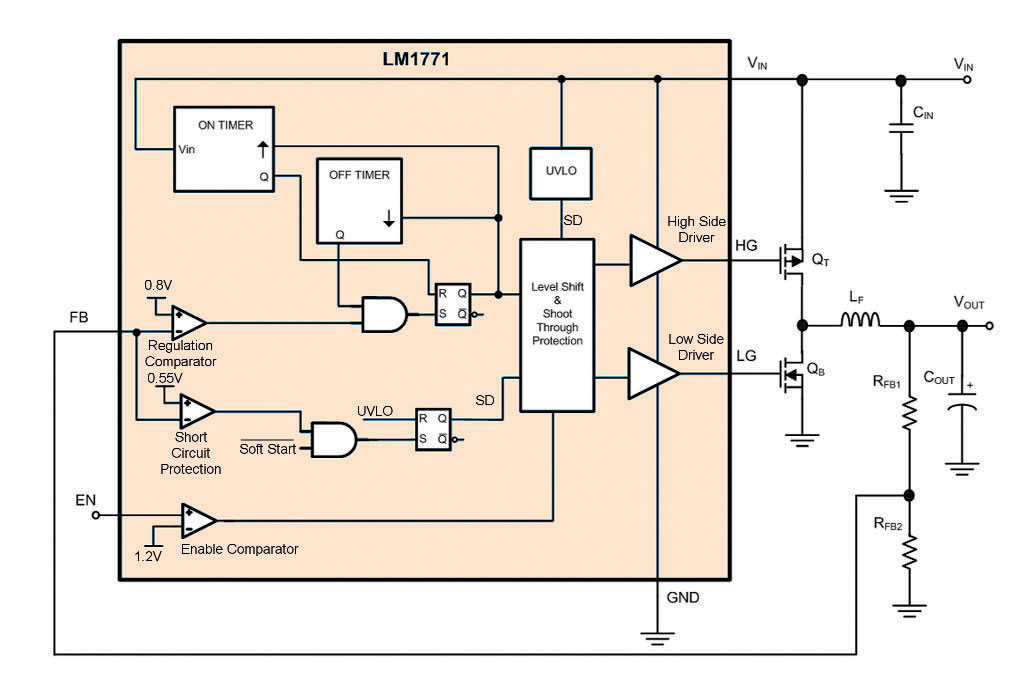

La proposta di questa soluzione per l’alimentazione di FPGA è destinata alla famiglia Virtex-5, ma una analoga strategia può essere utilizzata per l’alimentazione di dispositivi Stratix III, con le sole modifiche marginali che riguardano le differenze delle tensioni. La sequenza di poweron raccomandata da Xilinx è VCCINT, VCCAUX, e VCCO. Anche se ogni sequenza di power-on con caratteristiche monotoniche può essere accettata, l’impiego della sequenza raccomandata consente a Xilinx di definire il valore della minima corrente di inrush richiesta dal core dell’FPGA, dalle sezioni ausiliarie e dall’I/O, denominate rispettivamente ICCINTMIN, IAUXMIN, e ICCOMIN, che assicurano una accensione e una configurazione corretta. La soluzione proposta impiega tre controllori di PWM LM1771 che consentono di controllare individualmente il power-up e il power-down di ogni singola tensione per mezzo di un dispositivo sequenziatore LM3880. Lo schema a blocchi del l’LM1771 comprensivo dei componenti esterni è riportato nella figura 1.

Figura 1: schema a blocchi del convertitore buck LM1771 che impiega l’architettura di controllo COT.

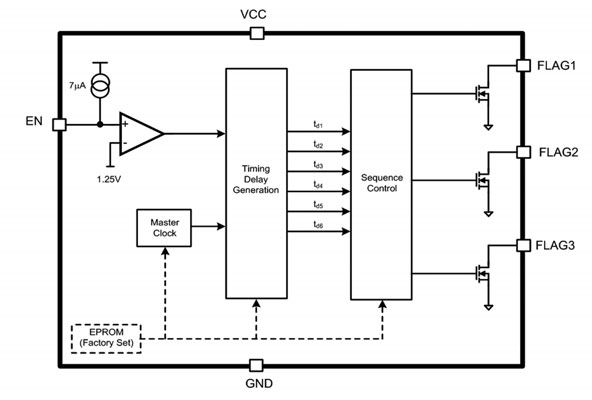

L’LM1771 è un convertitore buck ad alta efficienza disponibile nei contenitori MSOP-8 e LLP-6, in grado di convertire una tensione di ingresso di valore compreso tra 2,8V e 5,5V in una tensione di uscita stabilizzata con un valore minimo di 0,8V. Il dispositivo controlla uno switch high-side costituito da un PMOS e uno switch low-side NMOS, ed impiega una architettura di controllo basata sul costant-on-time (COT) che elimina la necessità di un amplificatore errore e di conseguenza dei componenti esterni per la compensazione. Questo approccio consente di ottenere tempi di risposta alle variazioni del carico estremamente ridotti, e grazie alla presenza di un ingresso di abilitazione con soglia molto precisa è possibile realizzare sequenze accurate e garantire la massima flessibilità nello stabilire il campo operativo dell’alimentatore. L’LM1771 è disponibile in tre diverse opzioni di timing identificate dai suffissi S, T e U, che si traducono in tre possibili opzioni di frequenza per una specifica tensione di uscita. Per una specifica opzione di timing, la frequenza di switching è indipendente dal valore della tensione di ingresso dato che la modalità feed-forward di ingresso del convertitore provvede a variare il tempo di conduzione dello switch high-side in funzione della tensione di ingresso allo scopo di mantenere costante il valore dei volt-secondo al nodo dello switch. Grazie al contenitore di piccole dimensioni, l’LM1771 consente la realizzazione di un alimentatore completo in uno spazio estremamente ridotto, senza dover sacrificare efficienza e prestazioni. La figura 2 riporta lo schema a blocchi del dispositivo sequenziatore LM3880, che è disponibile in un contenitore SOT23-6, e dispone di tre uscite open-drain che consentono il controllo degli ingressi di abilitazione dei tre LM1771.

Figura 2: schema a Blocchi del sequenziatore LM3880.

Attivando l’ingresso di abilitazione dell’LM3880 otterremo che le tre uscite verranno rilasciate in modo sequenziale e con ritardi specifici, consentendo il corretto start-up dell’alimentatore. Le uscite di abilitazione seguiranno una sequenza inversa durante il power-down allo scopo di evitare condizioni di latch-up. Sono disponibili opzioni di timing standard di 10ms, 30ms, 60ms e 120ms. L’LM3880 può essere anche programmato durante il processo di fabbricazione allo scopo di ottenere opzioni di temporizzazione particolari combinate con sei diverse sequenze di power-down.

Realizzazione dell’Alimentatore per FPGA

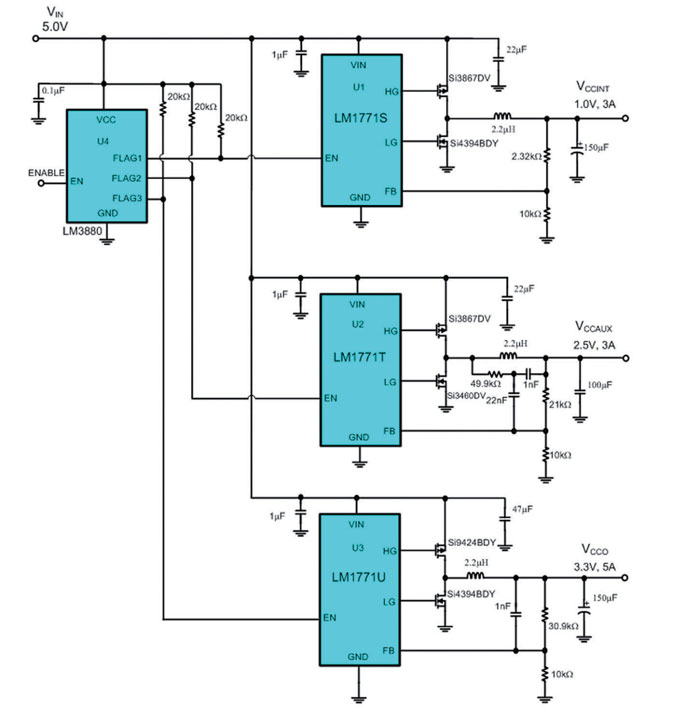

Lo schema dell’alimentatore basato sull’impiego dell’LM1771 e dell’LM3880 è riportato nella figura 3.

Figura 3: schema elettrico del sistema di alimentazione per FPGA Virtex-5.

Per questo progetto, i tre canali costituiti da regolatori buck sono in grado di erogare una corrente continua sul carico di 5A, 3A e 3A destinati rispettivamente alle linee di alimentazione di ICCO, ICCAUX, e ICCINT. La tensione di I/O è fissata a 3,3V ma può essere facilmente variata modificando il valore di una delle resistenze di reazione. Le linee di alimentazione del core e delle funzioni ausiliarie sono fissate rispettivamente a 1,0V e a 2,5V. I regolatori per il core, le funzioni ausiliarie e l’I/O usano rispettivamente i controllori LM1771S, LM1771T e LM1771U che operano alla frequenza di 606kHz, 758kHz e 500kHz. Ciascun alimentatore dispone di un proprio filtro di ingresso collocato il più vicino possibile ai powerMOS p-channel e n-channel che realizzano le funzioni di switch buck e sincrono. Oltre a questo, è previsto un piccolo condensatore di bypass collocato in prossimità di ciascun LM1771. I condensatori che costituiscono il filtro di uscita delle linee di alimentazione del core e dell’I/O sono al tantalio e scelti per presentare il corretto valore di ESR che garantisce un sufficiente valore di ripple in-fase all’ingresso di feedback FB del dispositivo. Un condensatore di feedforward connesso tra VCCO e FB aumenta l’ampiezza del ripple visto dall’LM1771. Il condensatore di filtro dell’uscita destinata all’alimentazione delle funzioni ausiliarie è ceramico allo scopo di minimizzare il rumore di uscita su questa linea. In parallelo all’induttanza di filtro di questa linea troviamo una rete RC che crea un segnale triangolare che viene accoppiato in ac al nodo FB, e che consente di rilevare il valore della corrente erogata. Questo circuito può essere utilizzato anche per le uscite che alimentano il core e l’I/O, nel caso che i condensatori al tantalio si dimostrino inadatti, e venga richiesto l’impiego di condensatori ceramici a basso ESR sia all’uscita del regolatore che nei pressi dell’FPGA. L’induttanza di filtro deve essere in grado di accettare correnti di elevato valore e presentare un basso valore di resistenza sia in DC che in AC allo scopo di massimizzare l’efficienza. Il valore dell’induttanza è determinato dal valore del ripple di corrente che di norma presenta un valore picco-picco pari al 30% della corrente nominale di uscita. E’ anche desiderabile scegliere una induttanza con caratteristiche di saturazione soft in grado di maneggiare transitori di corrente elevata ma di breve durata che presentino valori di corrente superiori a quelli di progetto. I powerMOS impiegati per l’uscita ausiliaria utilizzano un contenitore TSOP6, mentre per l’uscita destinata all’I/O il contenitore è un SO8. L’uscita che alimenta il core, grazie al fatto di operare con un duty-cycle particolarmente basso, utilizza un dispositivo high-side in contenitore TSOP6, mentre quello low-side è in SO-8. Per questa applicazione la scelta ottimale per l’LM3880 è rappresentata dalla versione -1AB che corrisponde all’opzione con timing da 30ms. Per garantire il corretto funzionamento è necessario connettere una resistenza di pull-up sulle uscite di flag che comandano gli ingressi di abilitazione degli LM1771.