Lo sviluppo di periferiche di I/O per pc sempre più prestanti e veloci, ha determinato la nascita di un nuovo standard di comunicazione, il pci express per superare i limiti del PCI.

Peripheral Component Interconnect (PCI), (interconnessione componente periferica), è l’interfaccia sviluppata da Intel intorno agli anni Novanta per collegare al computer le più svariate periferiche. La larghezza di banda dell’interfaccia PCI è rimasta negli anni ancorata a 133 MB/s, generata da una trasmissione dati con frequenza pari a 33MHz a 32bit. Questa tecnologia è considerata la seconda generazione che ha soppiantato la precedente tecnologia conosciuta con il nome di Industry Standard Architecture (ISA o Bus AT). I primi limiti dello standard PCI si sono fatti sentire poco dopo in sistemi come server e workstation, dove vi è bisogno di un enorme larghezza di banda per la trasmissione dei dati. Fu così che si iniziò a cercare e progettare sostituti per questa interfaccia: i più fortunati sono stati il PCI a 66MHz, il PCI X ed ora il PCI Express. Il primo è la diretta conseguenza del classico PCI: si caratterizza per un aumento della frequenza da 33 a 66MHz, per poi essere sfruttato sia con interfaccia a 32 che a 64bit per una banda massima teorica di 528MBytes/s. Accanto a queste nuove interfacce, il PCI ha subito nel corso del tempo delle leggere mutazioni: ad esempio abbastanza importante è la presentazione del PCI 2.3. Con questa nuova versione le prestazioni rimangono inalterate, ma sono stati introdotti i moduli che funzioneranno o esclusivamente a 3.3V (come per il PCI X) o in modo universale, riconoscendo la tensione adeguata (3.3V o 5V) e adeguandosi di conseguenza. Lo standard è sviluppato dal consorzio Peripheral Component Interconnect Special Interest Group.

Tecnologia PCI Express: il presente

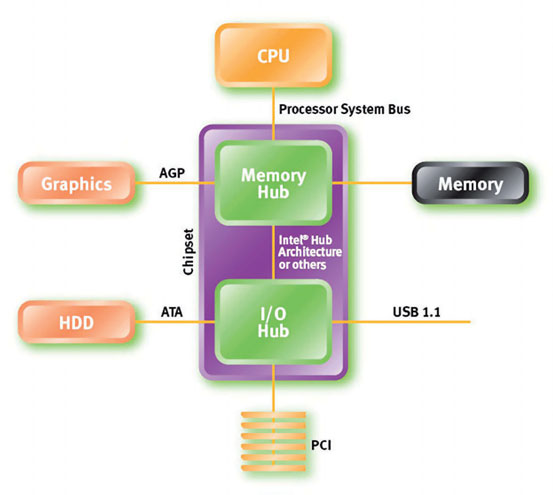

La figura 1 mostra la tipica architettura precedente all’introduzione di PCI Express. Durante tutti questi anni, il bus di comunicazione per il processore ha subito un rapido processo di scaling verso frequenze sempre maggiori e tensioni sempre minori. Per mantenere lo stesso passo del processore, anche le velocità delle memorie sono aumentate in ugual misura. Come si nota dalla figura 1, il chip set di una tipica scheda madre è partizionato in un memory hub e un I/O hub, dati i rapidi cambiamenti del primo.

Figura 1: tipica architettura dei PC prima dell’avvento del bus PCI Express. I differenti bus di interconnessione hanno differenti requisiti in termini di larghezza di banda.

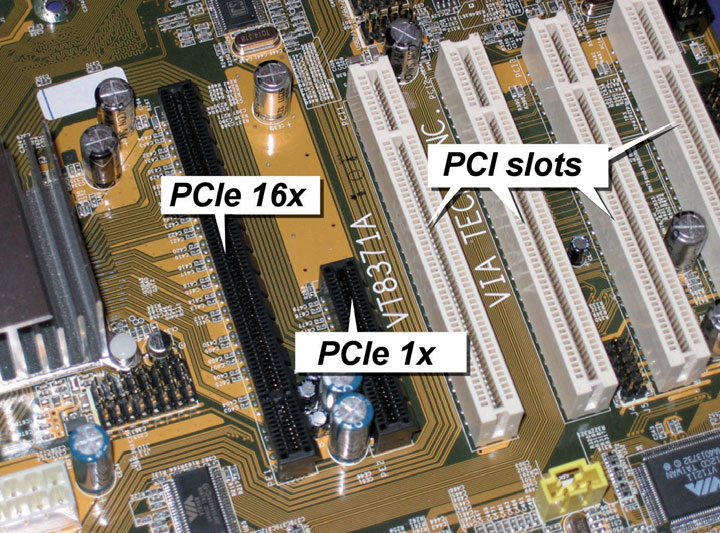

In tutto questo contesto il collo di bottiglia è rappresentato chiaramente dalle periferiche di I/O che non hanno subito altrettante rapide variazioni nel tempo. Il bus PCI è parallelo di tipo multi-drop. Le velocità attualmente raggiunte sono vicine ai suoi limiti teorici e questo rende moltodifficile uno scaling verso l’alto in frequenza e verso il basso in tensione; un aumento della frequenza comporterebbe problemi di skew del clock che degraderebbe troppo i dati. Un bus parallelo comporta anche l’impossibilità di realizzare una comunicazione full-duplex, poiché un solo device per volta potrà “parlare”. Sulla base dei limiti delle precedenti generazioni di piattaforme per il collegamento di periferiche I/O, il consorzio PCI-SIG ha sviluppato una nuova tecnologia profondamente differente dalle precedenti. Si tratta di un comunicazione di tipo duplex seriale che consente di raggiungere velocità comprese tra 250MB/s e 8GB/s. Il suo nome è PCI Express o spesso abbreviato con il termine PCIe. Si tratta di un bus completamente nuovo nell’architettura. Infatti, è stata abbandonato il bus parallelo per uno di tipo seriale (figura 2).

Figura 2: confronto tra i connettori PCI e PCI Express. La riduzione delle dimensioni e l’aumento della banda di

PCIe è stato possibile grazie all’architettura completamente rivisitata che prevede una connessione duplex seriale anziché un bus parallelo.

Ogni dispositivo è collegato all’altro in una connessione di tipo punto-punto e questo ha permesso di superare i limiti di velocità cui si accennava prima, garantire un comunicazione full-duplex e ridurre l’ingombro di piste su PCB. Va sottolineato però che nonostante questo profondo cambiamento, il PCIe conserva la compatibilità software con PCI. Dal punto dista pratico PCI Express sostituisce, tra l’altro, lo slot AGP (Accelerated Graphics Port) per le connessioni grafiche e permette l’interfacciamento con chipset GBEtherent.

PCI Express 1.1 e 2.0 - Overview

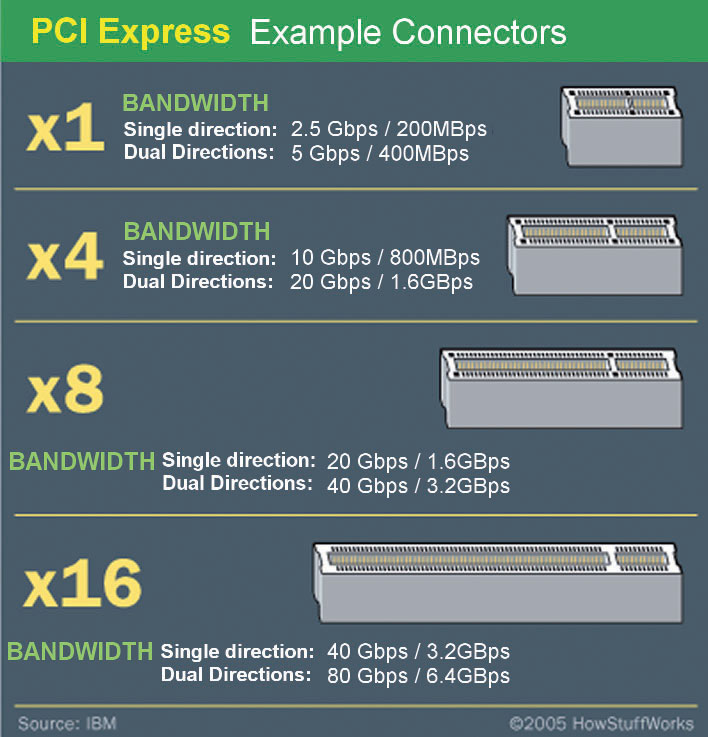

Nella prima versione di PCIe, spesso indicata come PCI Express 1.1, ciascuno slot può trasportare una (x1), due (x2), quattro (x4), otto (x8), sedici (x16) o trentadue (x32) linee (o lane) dati tra scheda madre e card PCIe (figura 3).

Figura 3: i connettori PCIe si differenziano tra loro a seconda del numero di lane supportate.

Figura 4: logo di PCI Express.

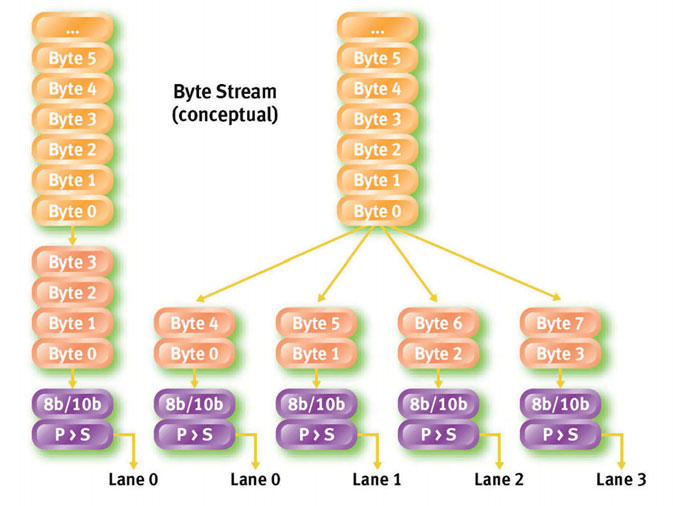

Ciascuna linee può trasportare teoricamente 2.5Gb/s che si riducono però a 250MB/s per il tipo di codifica utilizzata (8B10B, la stessa usata, ad esempio, per il Fast Ethernet). La massima velocità di trasferimento usando 32 linee è pari a: 32 x 250MB/s = 8GB/s.

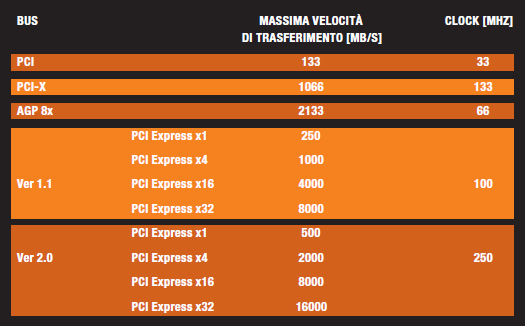

Comunque, la massima velocità tipicamente utilizzata è x16, quindi 4GB/s. Per maggiore chiarezza, in figura 3, si riportano i differenti connettori PCIe. Quindi uno slot PCI Express x1 raggiunge circa il doppio della velocità del classico PCI, mentre il x4 ha un velocità confrontabile con la versione PCI-X 1.0 ed ancora x8 raggiunge le prestazioni di uno slot AGP. Sulla scia del successo della prima versione, il 16 gennaio 2007 è stato presentato lo standard che andrà progressivamente a sostituire questa prima generazione del PCI Express. Per evidenziare che non si tratta in realtà di un vero e proprio nuovo bus di interconnessione ma piuttosto di un’evoluzione dell’attuale, la nuova tecnologia si chiamerà PCI Express 2.0 e servirà soprattutto per raddoppiare l’ampiezza di banda del BUS e la potenza fornita ai dispositivi collegati. La nuova versione raddoppia l’ampiezza di banda portandola da 2.5Gb/s per ogni lane a 5Gb/s. Cambia inoltra la frequenza di clock che da 100MHz è stata portata a 250MHz. Dal punto di vista meccanico ed elettrico le piattaforme PCI Express 2.0 sono pienamente compatibili con le precedenti versioni 1.1, non creando quindi problemi in caso di aggiornamenti delle piattaforme contenenti periferiche PCI Express 1.1. È prevista anche l’implementazione di una tecnologia per il controllo degli accessi che, oltre a permettere al software di gestire direttamente il routing dei pacchetti, dovrebbe impedire l’intrusione nella comunicazione dati allo scopo di rubare informazioni. La nuova generazione risolve anche il problema di alimentazione delle schede video che con PCI Express è limitato a 75 W; questo valore è da tempo insufficiente per le schede video di medio-alto livello, tanto che quasi tutte ormai montano un connettore d’alimentazione ausiliario collegato direttamente all’alimentatore per far fronte al fabbisogno energetico. Il PCI Express 2.0 dovrebbe permettere di rifornire la scheda video con 225 o 300W. La tabella 1 riporta un confronto tra le prestazioni dei diversi standard di seconda e terza generazione.

Tabella 1: confronto tra le massime velocità dei precedenti standard (PCI e AGP) e dello standard PCI Express.

Requisiti di 3GIO

Quando PIC-SIG ha deciso di sviluppare una nuova architettura per le periferiche di I/O (spesso anche indicata con 3GIO – ossia 3th Generation I/O) si è posta come requisiti fondamentali:

■ 1-Supporto per le applicazioni di differenti segmenti di mercato, ossia la necessità di un’architettura unificata per desktop, mobile, server, piattaforme di comunicazione, workstation e dispositivi embedded.

■ 2-Basso costo ed elevato volume. Perché si sviluppi PCIe, sostituendosi a PCI, la 3GIO deve necessariamente avere un costo inferiore o al massimo uguale.

■ 3-Compatibilità software con PCI. La possibilità di continuare ad utilizzare il software precedente anche su PCIe è stato un punto cardine nello sviluppo di PCIe.

■ 4-Prestazioni. Possibilità di aumentare la banda semplicemente aumentando il numero di linee di interconnessione. Questo è impossibile con PCI che ha un’architettura rigida e prefissata.

■ 5-Supporto di connessioni multi-piattaforma.

■ 6-Funzionalità avanzate. Lo standard prevede gestione della potenza dissipata, QoS, Hot Plug e Hot Swap, gestione degli errori.

PCI Express – Topologia

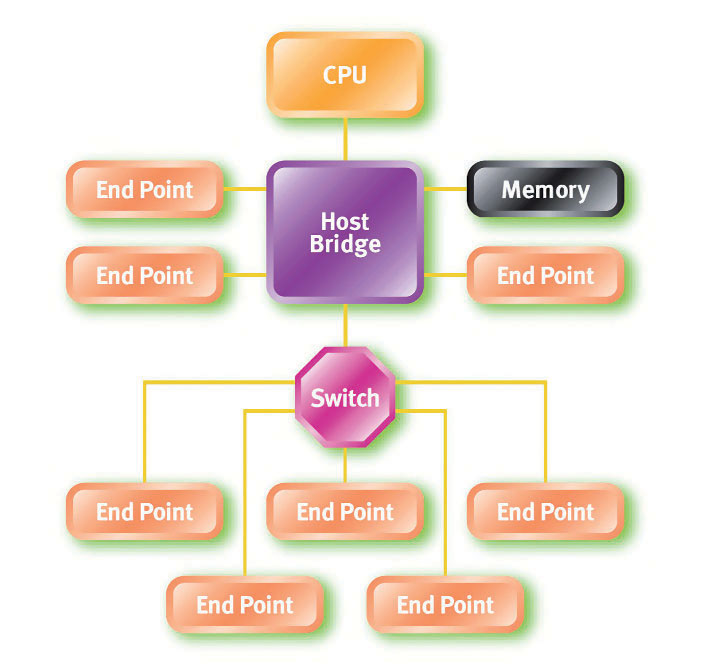

La topologia PCIe è costituita da un host bridge e diversi endpoint (ossia, i dispositivi I/O veri e propri), come illustrato in figura 5.

Figura 5: topologia PCI Express in cui si mostrano i tre elementi chiave: host bridge, switch ed endpoint.

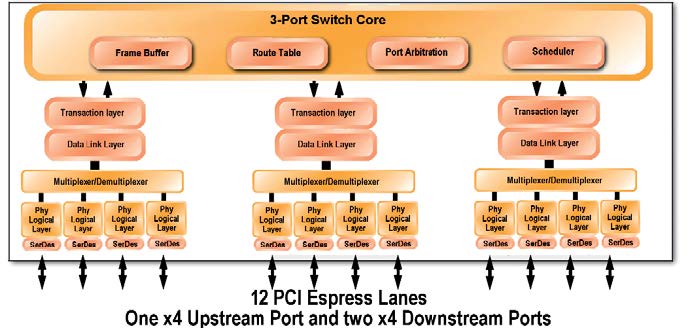

Si è già accennato in precedenza, il tipo di connessione è di tipo punto-punto e questo quindi introduce un nuovo elemento nella topologia PCI Express: lo switch. Esso ha il compito di sostituire il bus multi-drop, permettendo di incrementare il numero di dispositivi che vi si possono collegare. Mentre in PCI il limite era dettato da problemi come skew del clock e diafonia tra piste, in questo caso il limite è imposto dallo switch che è un circuito elettronico. Quindi ciò consente di andare ben oltre il limite teorico di PCI. Lo switch assicura anche comunicazioni peer-to-peer tra differenti endpoint e tale traffico non necessita di transitare per l’host bridge (un concetto molto simile a quello del DMA): ciò comporta una notevole riduzione del traffico dati e quindi un aumento della banda massima. Anche se nella figura 5 lo switch è rappresentato come un elemento logicamente separato, esso potrebbe in taluni casi essere integrato all’interno dell’host bridge. Lo switch ha un unico upstream, orientato verso l’host bridge. Il numero di porte di downstream, verso gli endpoint può essere ritenuto indefinito, ma in pratica è fissato un limite superiore di 256. Tra i principali produttori al mondo di switch PCIe, IDT sicuramente riveste un ruolo preminente. A titolo di esempio in figura 6 è mostrato lo schema a blocchi del modello 89HPES12NT3, dotato di 3 porte ed una capacità massima di 6GB/s.

Figura 6: schema a blocchi dello switch IDT modello 89HPES12N3. Si tratta di uno switch a 3 porte e 12 lane che offre una capacità complessiva di 6GB/s.

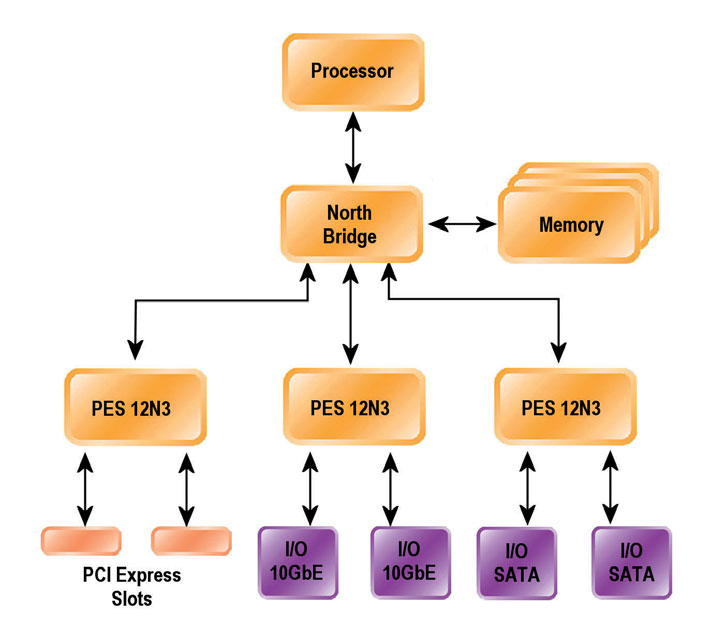

Ciascuna porta è dotata di quattro SerDes che consentono di selezionare (anche in modalità automatica) il numero di lane da utilizzare per la trasmissione. In figura 7 è presentato una tipica applicazione di questo componente. Due delle tre porte posso essere impiegate per interfacciarsi con gli endpoint (dispositivi 10GbE o slot generici), mentre la restante linea è impiegata per dialogare con l’host bridge.

Figura 7: esempio applicativo del chip 89HPES12N3 della IDT. Due delle tre porte possono essere utilizzate per il

downstream verso gli endpoint, mentre l’altra serve per l’upstreaming verso l’host bridge.

Architettura PCI Express

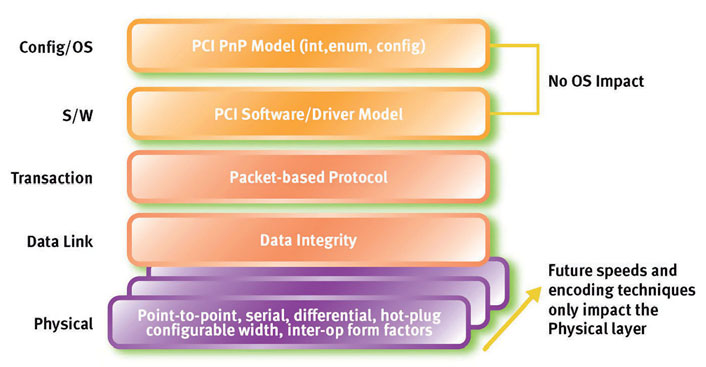

L’architettura PCI Express come si può vedere in figura 8 è organizzata in tre distinti layer:

➤ Fisico

➤ Data Link

➤ Transaction

Figura 8: l’architettura PCI Express è organizzata in tre distinti layer: fisico, data link e transaction

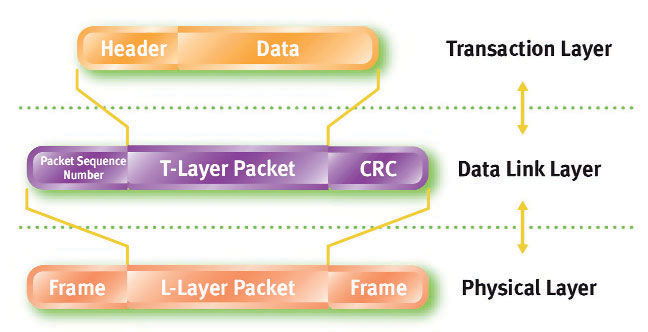

A livello software è generata una richiesta di lettura o scrittura (si ricordi che si tratta di periferiche di I/O) che sono tra sportate dal transaction layer ai dispositivi I/O. Il data link layer ha il compito di aggiungere il numero di sequenza e il CRC a tali pacchetti al fine di garantire l’affidabilità del trasferimento (figura 9).

Figura 9: il data link layer assicura funzioni di integrità

dei dati.

Il layer fisico consiste di due canali di tipo simplex (coppia di trasmissione e ricezione in tecnologie LVDS). E’ proprio a questo livello che è selezionato il numero di lane. I bit sono separati in base al numero di linee, come mostra la figura 10.

Figura 10: lo split dei bit in base al numero di lane

selezionate è effettuato nel layer fisico.

Durante la fase di inizializzazione, ciascun link PCI Express è impostato seguendo un processo di negoziazione del numero di linee e della frequenza operativa. E’ importate evidenziare che l’organizzazione a layer permetterà miglioramenti della velocità, della codifica o del mezzo fisico semplicemente agendo a questo livello e lasciando invariati i layer superiori.