La modulazione FSK (Frequency-Shift Keying) è una delle modulazioni più semplici che possono essere utilizzate sia in ambito hobbistico che in ambito professionale per la trasmissione di un segnale digitale tramite un collegamento analogico.

In elettronica la modulazione è un processo che varia un attributo di un segnale periodico ad alta frequenza, detto portante, in base al valore del segnale modulante. Il modo in cui si realizza la modulazione è paragonabile al metodo con cui un musicista modula un tono (una onda periodica) di uno strumento musicale, variando volume, fase e frequenza.

I tre parametri chiave di un segnale periodico sono infatti quelli appena citati: ampiezza, fase e frequenza. Possono essere modificati in base ad un segnale a bassa frequenza detto segnale modulante. Il segnale portante per eccellenza è un segnale sinusoidale ad alta frequenza, ma anche un segnale rettangolare può essere utilizzato efficacemente. Un dispositivo che realizza la modulazione di segnale è detto “Modulatore”, un dispositivo che realizza il processo inverso, ossia dal segnale modulato ad alta frequenza estrae il segnale modulante a bassa frequenza, è detto “Demodulatore”. Questo tipo di circuiti sono ampiamente utilizzati nell’ambito delle telecomunicazioni e sono l’abc per quelli del settore. L’obiettivo di una modulazione digitale, è di trasferire un flusso di bit attraverso una un canale analogico racchiuso tra una determinata banda passante, per esempio, la rete telefonica (300-3400Hz) o una banda radio limitata. L’obiettivo di una modulazione digitale in banda base, detta anche codifica di linea o line coding, è di trasferire sempre un flusso di bit digitale ma su un canale in banda base, per esempio, attraverso un collegamento tramite bus seriale o tramite una rete locale.

MODULAZIONE FSK

La modulazione FSK ossia FrequencyShift Keying, punta a modificare la frequenza del segnale portante in base al valore del segnale modulante. In particolare l’applicazione in esame realizza una modulazione FSK compatibile con il protocollo Bell-202. Si tratta di un vecchio protocollo sviluppato dalla Bell System per i modem, con una modulazione FSK del segnale audio (AFSK) codifica e trasferisce i dati alla frequenza di 1200 bit per secondo. Il protocollo Bell-202 AFSK utilizza un tono a 1200Hz per trasmettere un 1 binario e un tono a 2200Hz per uno spazio (zero binario). Il protocollo Bell-202 ha permesso di sviluppare tecniche come il multi-dropping di più modem slave, connessi ad un unico master attraverso un unico canale di comunicazione, in più è stato la base per la sovrapposizione di segnali ai cavi di alimentazione per distanze superiori agli 80Km in applicazioni marine.

IL CIRCUITO

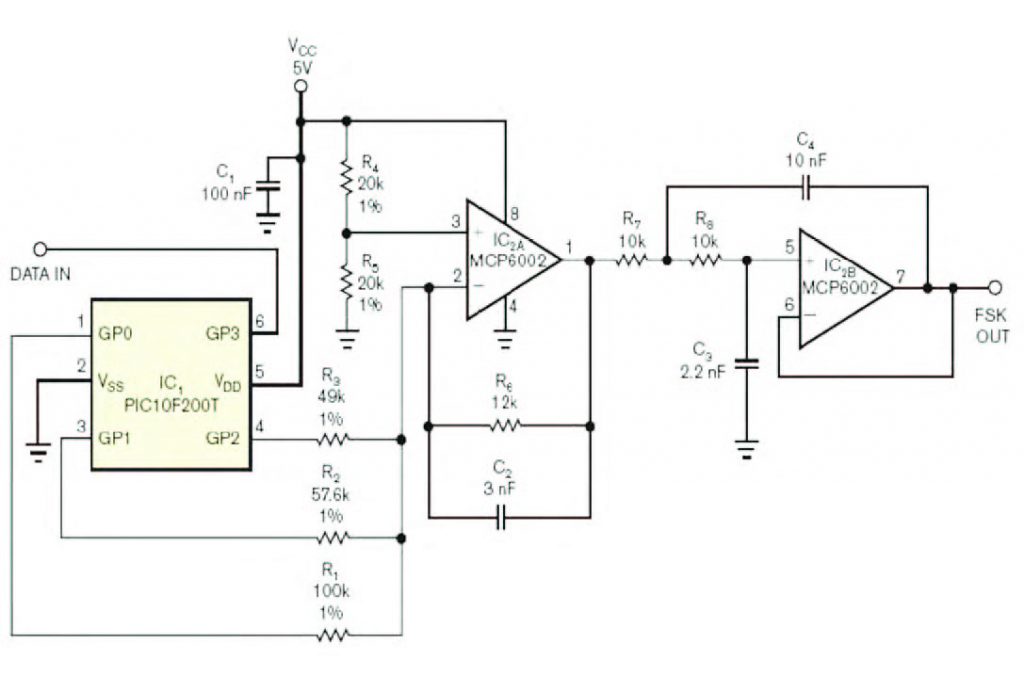

Un modulatore FSK comprende una forma d’onda digitale che oscilla tra due frequenze stabilite in base al livello logico di un segnale digitale. Il circuito in figura 1 genera un’onda sinusoidale campionando continuamente un singolo periodo sinusoidale.

Figura 1 circuito che realizza una modulazione FSK compatibile con il protocollo Bell-202.

L’uscita di IC2A è proporzionale alla corrente attraverso R1, R2 e R3. Queste resistenze sono collegate assieme all’ingresso invertente di IC2A polarizzato a Vcc/2. Le uscite GP0, GP1 e GP2 del microcontrollore IC1 producono un treno d’impulsi non sovrapposti. Quando uno dei tre pin genera un segnale alto o basso, gli altri sono in una situazione di alta impedenza. Quando uno dei tre pin è a livello alto, la tensione ai capi della resistenza collegata è pari a Vcc/2. Quando uno dei tre pin è a livello basso, ai capi della resistenza vi è una tensione di –Vcc/2. Necessario scegliere i valori di R1, R2 e R3 in modo tale che gli impulsi di corrente abbiano ampiezza proporzionale ai campioni della sinusoide rispettivamente a 30°, 60° e 90°. Quando tutte e tre le uscite del microcontrollore sono in alta impedenza, si produce i campione della sinusoide a 0° e non scorre corrente attraverso le resistenze. Quindi, partendo da una situazione di alta im pedenza per tutte e tre le uscite e in base alla sequenza di livelli alti in uscita su GPO, GP1, GP2 e poi nuovamente GP1 e GP0, si ottiene la generazione del primo semiperiodo positivo dell’onda sinusoidale. Ripetendo il processo, ma con le uscite a livello basso, si genera il semiperiodo negativo della forma d’onda. Attraverso questo schema si produce un’onda sinusoidale tramite 12 campioni per periodo. In aggiunta, rispetto alla frequenza base dell’onda generata f0, si possono inserire componenti a frequenza maggiore pari a (12k+1)f0 e (12k-1) f0, con k= 1,2,3 e così via. La seconda parte del circuito realizza un filtro passa basso, composto da IC2B, R7, R8, C3 e C4 in grado di filtrare le componenti ad alta frequenza ma a bassa ampiezza. Di seguito il Listato in assembly del programma ideato su PIC10F200T.

* A SIMPLE FSK MODULATOR * ; THIS CODE IMPLEMENTS A BELL 202 FSK MODULATOR list p=10F200 include ; This file is part of Microchip MPLAB IDE ;——————— PIC10F2xx CONFIGURATION ——————- __CONFIG _MCLRE_OFF & _WDT_OFF & _CP_OFF ; External Reset off ; Watch Dog timer off ; Code Protection off ;——————— VARIABLE DEFINITIONS ———————— UDATA PERIOD RES 1 ; Delay counter (Presets to time between sine samples) #define DATA_IN GPIO,3 ; GP3 is DATA_IN input pin OUT_0 EQU b’00001111’ ; GP0-GP3 configured as High Impedance OUT_1 EQU b’00001110’ ; Only GP0 configured as output OUT_2 EQU b’00001101’ ; Only GP1 configured as output OUT_3 EQU b’00001011’ ; Only GP2 configured as output P1 EQU d’19’ ; Delay constant for 1200 Hz P2 EQU d’9’ ; Delay constant for 2200 Hz ; Start of program RESET CODE 0x000 GOTO init SUBS CODE 0X10 CHK_DATA: ; Checks Data input pin MOVLW P1 ; Load W with 1200 Hz Delay constant BTFSS DATA_IN ; If DATA_IN == High skip next instruction MOVLW P2 ; Load W with 2200 Hz Delay constant MOVWF PERIOD ; Load Delay counter; NOP ; NOP’S added here to fine tune FSK frequencies NOP RETLW 0 init: MOVWF OSCCAL ; Load the factory Internal oscillator calibration ; value MOVLW OUT_0 ; GP0 - GP3 are OFF (High impedance) TRIS GPIO CLRF GPIO ; initialize outputs to Low Level ; initialize OPTION register MOVLW b’11000111’ ; Weak Pull-ups disabled ,Wake-up on pin change OPTION ; disabled LOOP: ; This loop produces the twelve sine samples CALL CHK_DATA ; Check Data DECF PERIOD,F ; decrement delay counter twice to compensate for DECF PERIOD,F ; the 6 added instruction cycles: ; GOTO LOOP(2 cycles) DECF PERIOD,F DECF PERIOD,F ; MOVLW 0xFF and MOVWF GPIO MOVLW OUT_0 TRIS GPIO ; GP0-GP2 are OFF (High impedance) MOVLW 0xFF MOVWF GPIO L1: DECFSZ PERIOD,F GOTO L1 CALL CHK_DATA MOVLW OUT_1 TRIS GPIO ; GP0 is High L2: DECFSZ PERIOD,F GOTO L2 CALL CHK_DATA MOVLW OUT_2 TRIS GPIO ; GP1 is High L3: DECFSZ PERIOD,F GOTO L3 CALL CHK_DATA MOVLW OUT_3 TRIS GPIO ; GP2 is High L4: DECFSZ PERIOD,F GOTO L4 CALL CHK_DATA MOVLW OUT_2 TRIS GPIO ; GP1 is High L5: DECFSZ PERIOD,F GOTO L5 CALL CHK_DATA MOVLW OUT_1 TRIS GPIO ; GP0 is High L6: DECFSZ PERIOD,F GOTO L6 CALL CHK_DATA DECF PERIOD,F ; decrement delay counter to compensate for the ; following 3 added instruction cycles ; (DECF PERIOD,F MOVLW 0x00 and MOVWF GPIO ) MOVLW OUT_0 TRIS GPIO ; GP0-GP2 are OFF (High impedance) MOVLW 0x00 MOVWF GPIO L7: DECFSZ PERIOD,F GOTO L7 CALL CHK_DATA MOVLW OUT_1 TRIS GPIO ; GP0 is Low L8: DECFSZ PERIOD,F GOTO L8 CALL CHK_DATA MOVLW OUT_2 TRIS GPIO ; GP1 is Low L9: DECFSZ PERIOD,F GOTO L9 CALL CHK_DATA MOVLW OUT_3 TRIS GPIO ; GP2 is Low L10: DECFSZ PERIOD,F GOTO L10 CALL CHK_DATA MOVLW OUT_2 TRIS GPIO ; GP1 is Low L11: DECFSZ PERIOD,F GOTO L11 CALL CHK_DATA MOVLW OUT_1 TRIS GPIO ; GP0 is Low L12: DECFSZ PERIOD,F GOTO L12 GOTO LOOP EN

| Listato 1 |

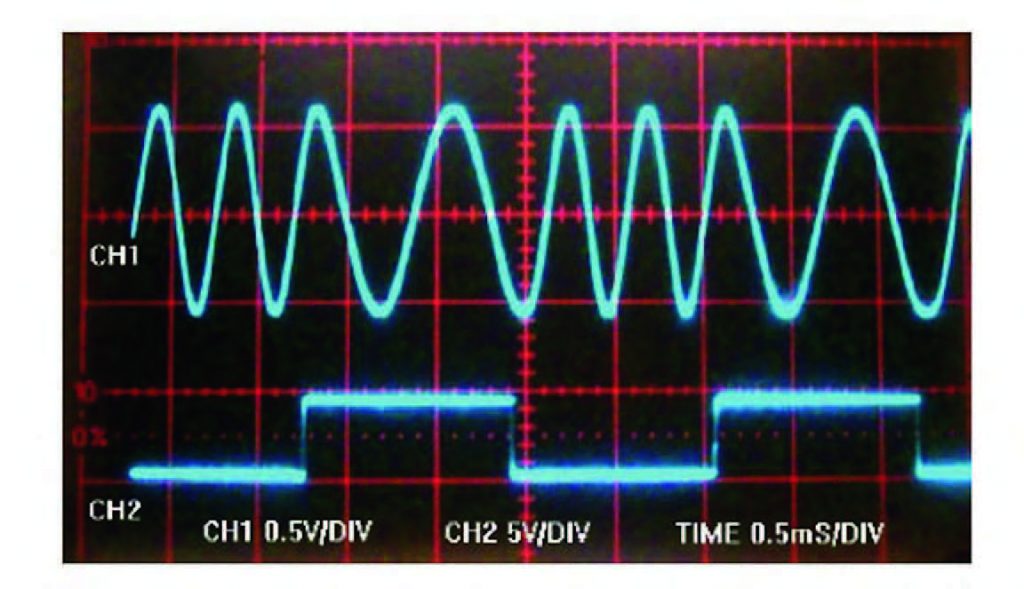

Quando l’ingresso di controllo Data In è a livello alto, la frequenza d’uscita è 1200Hz; quando è a livello basso in uscita si hanno 2200 Hz. Il passaggio da una frequenza all’altra è realizzato in maniera tale da mantenere la continuità di fase. In figura 2 sono visualizzati il segnale FSK modulato (CH1) e il segnale digitale modulante (CH2).

Figura 2: segnale FSK modulato (CH1) e segnale digitale modulante (CH2).