Nella prima parte abbiamo visto come le prestazioni del sistema di alimentazione di una moderna applicazione digitale (Power Distribution Network, PDN nel seguito) si siano fatte più stringenti che in passato.

A questo concorrono principalmente le caratteristiche dei circuiti integrati moderni, con tensioni di alimentazione sempre più basse e frequenze operative sempre maggiori, ma anche esigenze di affidabilità e costo. Le conseguenze di eccessive fluttuazioni nelle tensioni di alimentazione locali ad un circuito integrato, particolarmente CMOS, sono molteplici. Assistiamo a generazione e propagazione di rumore elettrico nel sistema, violazioni delle temporizzazioni, incertezze nelle commutazioni (jitter), rischio di emissioni elettromagnetiche abbastanza elevate da fallire le prove di compatibilità e non ottenere le certificazioni indispensabili alla commercializzazione del prodotto ed infine riduzione dell’affidabilità nel tempo. Osserviamo di conseguenza la crescita di importanza delle tecniche di Power Integrity ed alla sua applicazione in ambiti sempre più ampi. Naturalmente, applicazioni embedded a singolo microcontrollore avranno esigenze ben diverse dalla scheda madre di un server per applicazioni di rete.

Le tecniche e gli strumenti disponibili vanno quindi dosati e proporzionati adeguatamente alla fascia di complessità, costo e affidabilità desiderate. La cassetta degli attrezzi PI comprende sostanzialmente il regolatore di tensione, la distribuzione di massa e alimentazione sul circuito stampato ed i condensatori di disaccoppiamento e filtraggio. Nulla di nuovo, si potrebbe dire. In realtà il primo elemento caratterizzante il paradigma Power Integrity sta nel considerare tutti questi componenti insieme, con i loro effetti del secondo ordine quali le antirisonanze, cooperanti a costituire un sistema, la PDN appunto. In particolare, viene sottolineata la necessità di pensare il pcb come un componente avente funzioni fondamentali nel garantire la qualità di segnali ed alimentazioni, non un mero supporto alle connessioni tra i componenti attivi e passivi della scheda. Il secondo elemento caratterizzante il paradigma PI è la considerazione del dominio della frequenza e non solo o principalmente del dominio del tempo (i classici transitori di tensione e corrente). Vedremo in questa seconda ed ultima parte come far buon uso dei componenti e strumenti a nostra disposizione.

CRITERI DI PROGETTO

Allo stato dell’arte, non esiste ancora una metodologia riconosciuta universalmente valida, per la progettazione di una PDN complessa . Esistono varie scuole e vari approcci, ciascuno influenzato dal campo di applicazione previsto ma anche fondato su culture aziendali diverse. Ogni progetto ha proprie priorità e criticità che spostano l’equilibrio ottimale tra prestazioni, affidabilità e costo a vantaggio di questa o quella soluzione. La maggiore o minore sofisticazione degli ambienti di progettazione e simulazione e della strumentazione a disposizione, determinano inoltre il grado di ottimizzazione raggiungibile. In ogni caso possiamo definire le seguenti fasi di sviluppo della PDN integrate nel progetto complessivo, naturalmente:

- Progettazione

- Verifica

- Collaudo

Entriamo nel dettaglio di ogni fase, analizzando le opzioni disponibili.

PROGETTAZIONE

La progettazione della PDN inizia tradizionalmente con il calcolo della portata in corrente continua richiesta ed il conseguente dimensionamento del rame del pcb, accompagnato da considerazioni termiche per evitare sovrariscaldamenti localizzati. I criteri di Power Integrity vanno qui naturalmente ad aggiungersi ai criteri classici:

- Adeguata portata in corrente e rispetto delle densità di corrente massime

- Dissipazione termica

- Costo

Usando la “cassetta degli attrezzi” introdotta in precedenza, la progettazione consiste nel definire la struttura del pcb (stackup ed assegnazione dell’uso di ogni layer), valore, quantità e tipo dei condensatori, scelta del regolatore di tensione. La capacità totale necessaria può essere determinata ottenendo le raccomandazioni di decoupling dal costruttore per ogni circuito integrato impiegato o stimata dai transitori di corrente previsti. È saggio combinare i due metodi in modo che un criterio di progetto verifichi l’altro. Stenderemo quindi lo schema elettrico associando ad ogni componente attivo il decoupling tipico raccomandato da datasheet o Application Notes. Occorre ora stimare o ottenere da datasheets i transitori di corrente e verificheremo che la capacità prevista a schema sia in grado di farvi fronte, restando all’interno della fascia di tolleranza delle alimentazioni. Utilizziamo la formula seguente:

Di=CDv/tr

Dove I è il valore del transitorio di corrente, v è la massima variazione di tensione tollerata, C la capacità totale e tr la durata del transitorio. Notare che potremmo dover considerare diversi tipi di transitorio, con differenti tr. Una volta rifinita la capacità totale, occorre decidere con quanti condensatori implementarla, di quale tipo e valore, applicando anche le considerazioni svolte nella prima parte di questa serie. Fermo restando il Bulk Decoupling, concentrato in pochi grossi elettrolitici, sostanzialmente dobbiamo decidere tra:

- Decoupling locale o distribuito

- Molti condensatori di identico valore o combinazioni di valori diversi (almeno un valore per decade nelle implementazioni più semplici, tipicamente in rapporto 4-4-2 per applicazioni high-end). I condensatori che realizzano il Bulk decoupling sono scelti in modo da avere valore complessivo da una a dieci volte il totale del decoupling locale. Uno o due bulk capacitors sono montati all’ingresso di alimentazione della board, o nelle immediate vicinanze del regolatore qualora questo sia montato sulla board stessa.

Lo scopo finale della nostra progettazione è “scolpire” l’andamento in frequenza dell’impedenza della nostra PDN, in modo che sia in grado di erogare la corrente richiesta ad ogni frequenza di interesse, evitando di uscire dalle tolleranze di tensione a specifica per ogni valore di frequenza. Il decoupling locale vede sostanzialmente un condensatore per ogni pin di alimentazione, montato il più vicino possibile ad esso. Questa soluzione è indispensabile quando non si hanno piani continui dedicati alla PDN ed è spesso soddisfacente per componenti in package QFP e/o frequenze di lavoro contenute. Nel decoupling distribuito, detto anche “area decoupling”, tale associazione pin/condensatore si perde, avendo una griglia di condensatori sparsa su tutta la superficie della board. La distanza tra condensatore e la sorgente dei transitori di corrente (pin alimentazione dei CI) deve comunque essere contenuta, ma non è necessaria una stretta contiguità, possiamo considerare sufficiente un condensatore nel raggio di 1 cm dal pin di alimentazione. Questa topologia è indicata per componenti in package Ball Grid Array (BGA nel seguito), schede dense ed elevate frequenze di funzionamento. In ogni caso, come visto nella prima parte, occorre minimizzare l’induttanza di collegamento. Per quanto riguarda invece il valore da assegnare ai componenti, il grande vantaggio del metodo chiamato “Big - V”, tanti valori uguali in parallelo, è la relativamente minore presenza di antirisonanze. Il nome “Big - V” viene dalla forma del profilo di impedenza in frequenza visto nella figura 8 della prima parte. A frequenze medio - basse è più semplice ottenere basse impedenze complessive con questo metodo. Combinazioni di valori diversi possono essere usati per ottenere un basso profilo in una ampia gamma di frequenze. Possiamo coprire il valore totale distribuendo la capacità su tre o quattro decadi, con un valore per decade e quantità di condensatori decrescenti al crescere del valore. Ad esempio, usando componenti da 1 uF, 100 nF, 10 nF, potremmo avere due condensatori da 1 uF, quattro da 100 nF ed otto da 10 nF. L’autore utilizza il decoupling locale & big-V per applicazioni con microcontrollori senza memoria esterna e frequenze ai pin dell’ordine di poche decine di MHz, prevedendo comunque alcuni siti per condensatori opzionali distribuiti sulla superficie in modo da poter intervenire facilmente ed espandere il decoupling in caso di problemi senza rifacimenti di pcb, dispendiosi in tempo e denaro. L’autore, in linea di massima, privilegia invece il decoupling di area associato alla scala di condensatori, per applicazioni con molti integrati logici, CPU con memoria esterna veloce, FPGA, package Ball Grid Array. Tende comunque ad usare pochi valori diversi e minimizzare l’induttanza parassita di collegamento.

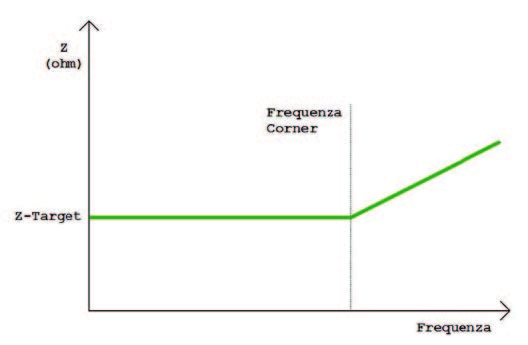

Il vantaggio del metodo “decoupling da datasheet”, basato sulle sole raccomandazioni del produttore di IC, consiste nella semplicità ma lo svantaggio è ben evidenziato nella Figura 3, dove si nota come la risposta in frequenza della PDN non sia ‘piatta’ ma presenti gamme in cui presenta valori di impedenza relativamente elevati, con il rischio di non essere in grado di fornire la corrente richiesta senza eccessive riduzioni di tensione in corrispondenza a tali frequenze. Discuteremo nel prossimo capitolo come capire se questo comportamento sia o meno un problema. Un metodo di progettazione della PDN più sofisticato è rappresentato dal calcolo della “Target Impedance”, cioè l’impedenza massima che deve essere presentata in tutta la gamma di frequenze di lavoro prevista, senza generare un ripple maggiore del limite prefissato “ripple” nella formula seguente:

ZT=(Vdd x ripple)/(50% x Imax)

Notare l’assunzione del 50% della corrente assorbita massima, come corrente dinamica associata alla commutazione della circuiteria logica. Il principio su cui si basa il concetto di Target Impedance è semplice, diretta applicazione della legge di Ohm (in ac). Per ogni frequenza, l’impedenza deve essere tale da mantenere la tensione di alimentazione nei limiti di specifica, possibilmente con un certo margine. I problemi iniziano nell’applicazione pratica del metodo. Per poter dimensionare l’impedenza target dobbiamo avere una stima del consumo di corrente complessivo del nostro sistema e un’idea precisa della banda passante che dobbiamo garantire, quindi servirebbe anche un profilo corrente/frequenza o quantomeno le forme d’onda dei transitori di corrente cui dobbiamo far fronte, da cui poi ricavare eventualmente lo spettro corrispondente. Oltre al valore di Impedenza Target, dobbiamo quindi anche definire fino a quale frequenza dobbiamo garantirlo (corner frequency). Queste informazioni non sono facili da ottenere e questo porta a sostituirle con stime che inevitabilmente portano a definire una PDN sovradimensionata, cioè con un valore di impedenza inferiore al richiesto o estesa a bande di frequenza dove non sarebbe strettamente necessaria. Il metodo è quindi più adatto per applicazioni sofisticate e costose dove, da un lato non se ne può fare a meno pena rischi sull’affidabilità del sistema e dall’altro l’aggravio di costo è poco avvertibile sul totale del sistema (per approfondire, vedi Rif. 1 e 2) Applicazioni sofisticate quali dense FPGA vedono un supporto notevole da parte del fornitore di chip anche per la progettazione della PDN. Le maggiori case costruttrici offrono oltre ad accurate Application Notes, anche tools di calcolo per determinare il consumo della circuiteria implementata nei propri componenti (vedi ad esempio Rif. 3), risolvendo cosi il problema reperibilità informazione. è interessante notare come in applicazioni a microprocessore, ogni attività periodica crea assorbimenti a frequenza sottomultipla del clock di sistema. Non è a priori possibile definire a quali frequenza si avranno domande di correnti transitorie da soddisfare. L’impedenza della PDN in questo caso dovrebbe essere piatta praticamente dalla cc fino ad almeno il doppio della frequenza di clock. La scelta della corner frequency ha un peso notevole nel determinare il costo finale della PDN. Il concetto di “Impedenza Target” È comunque un utile strumento da usarsi anche come criterio di verifica della PDN comunque progettata.

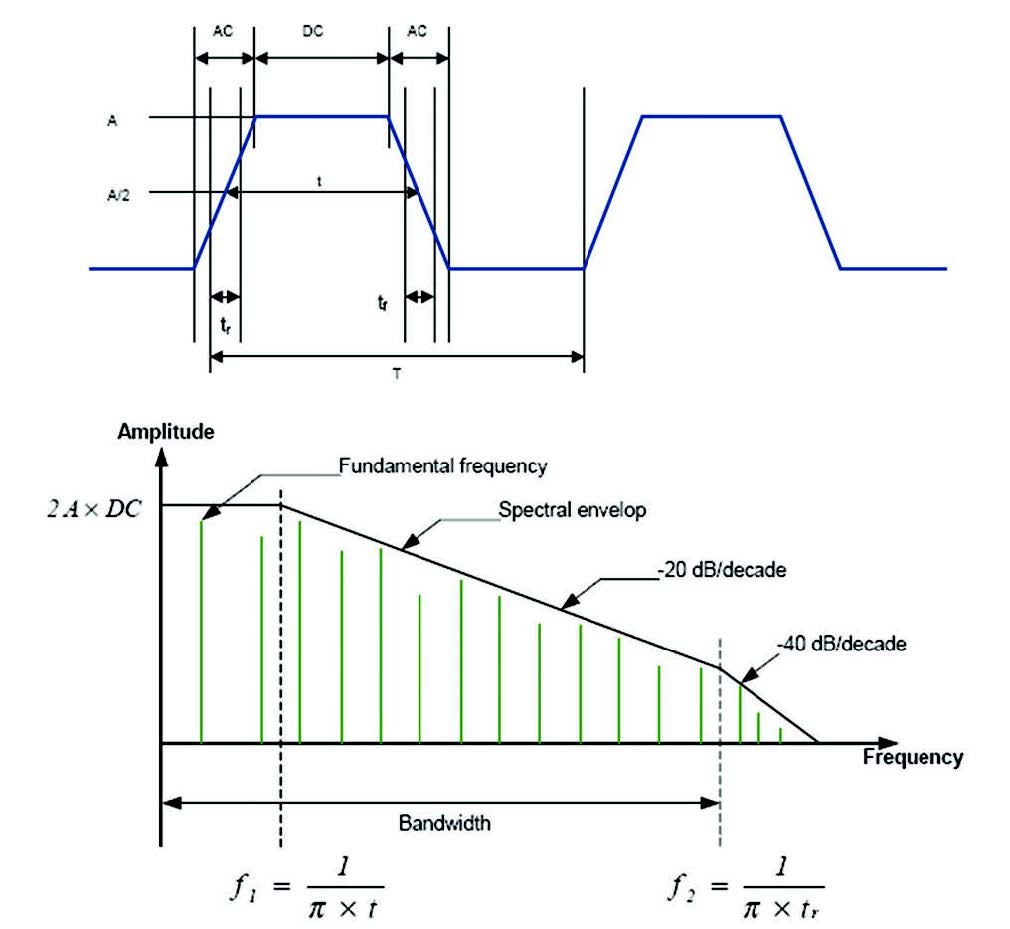

Figura 1: segnale digitale e suo inviluppo

in frequenza.

VERIFICA

In generale, quanto più siamo in grado di verificare per mezzo di simulazioni il funzionamento della nostra applicazione, prima della costruzione del prototipo, migliori saranno le probabilità di successo al primo passaggio. Oggi vari strumenti sono disponibili e stanno evolvendo per operare sulla PDN. Naturalmente la verifica non è gratis, richiedendo tempo e costosi software, oltre a persone con l’esperienza necessaria. Il bilancio rischi/benefici va quindi accuratamente ponderato, progetto per progetto. Possiamo distinguere almeno tre livelli di simulazione sono applicabili alla verifica della PDN:

- Unidimensionali o simulazione elettrica SPICE-like

- 2D o Pseudo-2D

- 3D

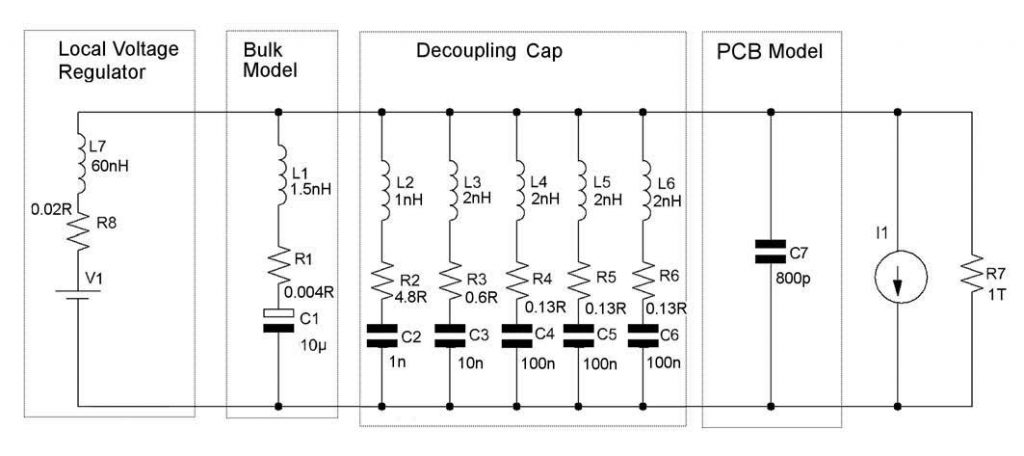

Il punto di partenza per tutti i simulatori è la disponibilità di un database (uno o più files) che descrive completamente schema elettrico, pcb, componenti passivi e, possibilmente, componenti attivi rappresentati da qualche forma di modello elettrico. La simulazione SPICE, è puramente elettrica, non rende conto dei fenomeni dovuti ai parametri parassiti distribuiti, a meno che siano modellati con componenti discreti, come abbiamo fatto per i condensatori dei vari schemi presentati. Ad esempio, la massa è un singolo nodo ideale, equipotenziale, quando abbiamo visto nella prima parte di questa serie che le cose non stanno affatto cosi nella realtà. Una simulazione dell’insieme dei componenti la PDN, di cui vediamo un semplice esempio in figura 2, è comunque utile per una preliminare verifica dell’adeguatezza della capacità complessiva a mantenere la fluttuazione di tensione entro i limiti di specifica.

Figura 2: schema semplice PDN

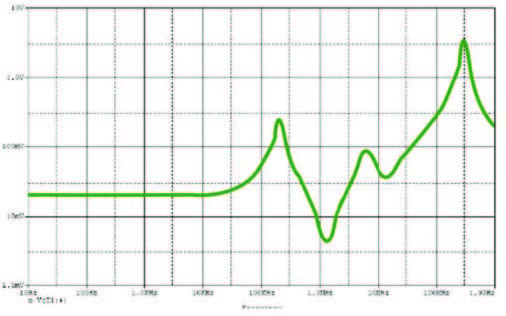

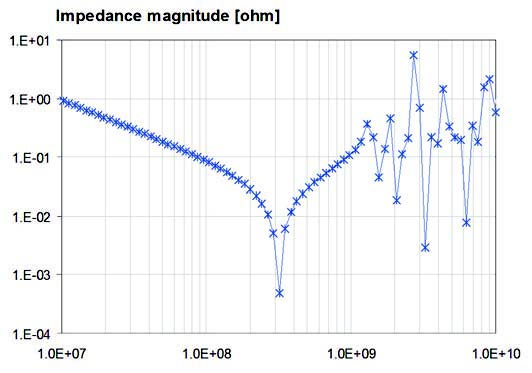

La figura 3, già richiamata, mostra l’andamento in frequenza della impedenza su grafico con entrambi gli assi in scala logaritmica per evidenziare le ampie variazioni delle grandezze presentate. Queste simulazioni sono eseguite con SPICE in modo AC, per avere la risposta in frequenza del sistema. è conveniente usare come stimolo un generatore di corrente sinusoidale con corrente di 1 A. In questo modo la scala verticale consente di leggere direttamente l’impedenza in ohm ad ogni frequenza, in quanto numericamente coincidente con la tensione calcolata dal simulatore.

Figura 3: simulazione SPICE AC della PDN in figura 2.

La resistenza da 1 Teraohm serve unicamente a fornire a SPICE il ritorno a massa in dc di cui ha bisogno. Il regolatore di tensione è stato modellizzato manualmente in modo abbastanza grossolano, ma sufficiente per lo scopo. I valori di resistenza ed induttanza, peraltro sufficientemente generali, rendono conto della regolazione del carico e della risposta ai transienti di carico del componente usato (qui un regolatore lineare L1117). Stimoli più sofisticati di un’onda sinusoidale sono ovviamente possibili, qualora siano disponibili le forme d’onda della corrente o sue approssimazioni avremmo una migliore rappresentazione del comportamento del nostro sistema. La simulazione generalmente avrà uno o più picchi di antirisonanza. In generale, per farsi un’idea della criticità o meno dei picchi di impedenza ad una determinata frequenza, occorre confrontare questa con la banda passante prevista per il nostro sistema. Sovrapposizioni tra banda passante e frequenze operative dovrebbero portare a verificare se l’entità della discontinuità sia tale da poter causare violazioni delle specifiche sulla tolleranza dell’alimentazione. Ad esempio potremmo cercare variazioni maggiori del 5%, considerando - 10% VDD la massima variazione di tensione tollerata da specifica dei componenti, 2% la tolleranza del regolatore e 3% di margine. Particolarmente critiche sono sovrapposizioni o contiguità con le frequenze di oscillatori della base dei tempi, con le principali armoniche del clock di CPU o reti logiche sincrone, con i clock di linee di trasmissione dati e con segnali ciclici in genere. Qualora si ritenga che un picco sia inaccettabile, ad esempio in base a considerazioni basate sul concetto di Impedenza Target, occorrerà smussarlo introducendo un condensatore con frequenza di risonanza serie uguale o molto prossima alla frequenza propria del picco. Questo creerà verosimilmente altri picchi di antirisonanza, il processo prosegue quindi in modo interattivo, fino ad essere soddisfatti del profilo in frequenza ottenuto. Il profilo ideale che vorremmo ottenere è schematizzato in figura 4, piatto da frequenze prossime alla dc fino alla corner frequency e poi gradualmente crescente con l’inevitabile comportamento sostanzialmente induttivo.

Figura 4: profilo impedenza ideale.

Per intervenire in modo efficace sul profilo di impedenza in una banda maggiore estesa oltre i 100 MHz, la simulazione circuitale vista non è in genere sufficiente, come vedremo tra poco. Osserviamo inoltre la figura 5. I numerosi picchi nella regione ad alta frequenza non sono dovuti ad antirisonanze di componenti fisici ma ai vari modi di risonanza della cavità formata da piani di alimentazione e massa. Questi effetti non sono catturati da una pura simulazione SPICE.

Figura 5: profilo di impedenza con risonanze di cavità di una board 10x10cm (calcolato con Plane-Self-Z, free download da http://www.electrical-integrity.com, Tool Download).

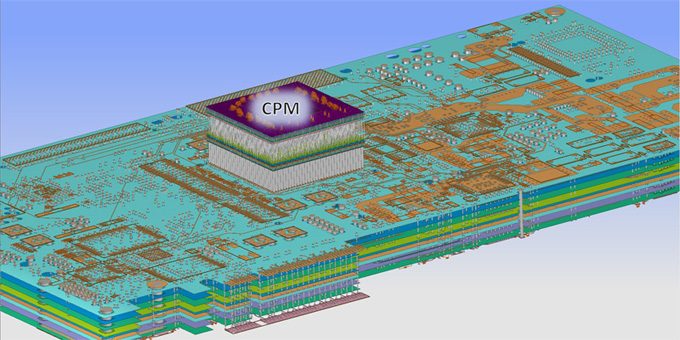

Non esiste descrizione delle basi fisiche del fenomeno ‘risonanza di cavità’ in uno schema elettrico, come non esiste rappresentazione delle dimensioni fisiche degli oggetti. Per valutarne l’effetto, occorre passare a strumenti più sofisticati. Il passo successivo in accuratezza, complessità e costo, è quindi una simulazione 2D o Pseudo-2D, eseguita in ambiente SPICE, in cui sia anche modellizzato il circuito stampato con le sue dimensioni ed il posizionamento fisico dei componenti attivi e passivi. Passiamo sostanzialmente da una descrizione del nostro sistema a parametri concentrati a descrizioni in cui introduciamo in misura crescente i parametri distribuiti, associati alle proprietà parassite ed alle dimensioni fisiche. Questo si ottiene nella metodologia Pseudo-2D definendo un quadratino di pcb con associata la propria resistenza, induttanza e capacità e combinandone un numero sufficiente a rappresentare l’intero pcb (vedi Rif. 4, Appendice A, notate che si tratta di un testo di autori italiani). Realizziamo quindi manualmente l’operazione di ‘mesh’, svolta automaticamente per noi da tool più sofisticati. L’approccio Pseudo-2D è stato convalidato fino ad oltre 1 GHz (vedi Rif. 6), dimostrando che un modello SPICE di pcb costruito come qui brevemente descritto, fornisce risultati congruenti con misure e simulazioni Full-Wave. E’ possibile usare i risultati ottenuti da questo genere di simulazione per smussare il profilo di impedenze, la rappresentazione fisica della nostra applicazione inizia ad essere abbastanza accurata da rendere l’operazione significativa. Possiamo notare come il metodo richieda parecchio lavoro manuale, quindi sia esposto a rischi di errore umano, errori che sono poi difficili da localizzare a posteriori. La costruzione del modello è agevole per geometrie semplici, diventa certamente più complessa in presenza di profili non rettangolari, con dettagli fini presentati ad esempio dal partizionamento dei piani di alimentazione. Come spesso accade, usiamo tempo e lavoro umano a compensazione dell’assenza di tool automatici di modellizzazione e calcolo. Il metodo presenta inoltre problemi pratici qualora si vogliano rappresentare geometrie fini quali gli interassi dei pin di densi circuiti integrati ed il piazzamento dei corrispondenti condensatori di decoupling. Il numero di componenti necessari a modellizzare anche un piccolo pcb diventa molto elevato, superando certamente presto i limiti massimi consentiti dalle versioni demo di SPICE. Tutte queste ragioni, aggiunte all’esigenza di svincolarsi da limiti in frequenza e ridurre la dipendenza dall’esperienza dell’utente medio, suggeriscono che diventi ad un certo punto tecnicamente conveniente fare un ulteriore salto nella scala delle tecnologie di simulazione per passare a simulatori commerciali 3D o Full Wave. Questi simulatori dividono le strutture fisiche e lo spazio immediatamente circostante in cubetti elementari di materiale uniforme, risolvono poi le equazioni di Maxwell localmente per ogni cubetto calcolando tutti i parametri elettrici elementari ad esso corrispondenti nelle tre dimensioni spaziali. È possibile visualizzare a partire dai risultati numerici la distribuzione nello spazio di campi elettrici, magnetici, impedenze e sue componenti, consentendo di identificare zone critiche. Come si può immaginare, la quantità di calcoli eseguita è notevole. L’approccio appena descritto è relativo ai simulatori detti ‘Full Wave’ in quanto operano direttamente su rappresentazioni fisiche del comportamento dei materiali e le loro proprietà elettromagnetiche, senza semplificazioni. Al fine soprattutto di contenere i tempi di simulazione, molti programmi introducono semplificazioni basati su proprietà geometriche e conseguentemente limitazioni nei modi di propagazione della struttura fisica considerata (tipicamente, un pcb visto come una “pila” di strati di materiale omogeneo, ipotesi ragionevole per molte applicazioni). Riferimenti ai produttori di alcuni tool software, senza pretesa di completezza, sono riportati in Rif. 5. L’uso di questi programmi CAD evoluti permette l’estrazione automatica dei profili di impedenza della PDN di complessità e forma qualsiasi, trovando un limite nelle quantità di memoria necessaria e nel tempo di elaborazione.

I programmi sono in grado di leggere direttamente il file descrittivo del pcb, come generato dai più diffusi programmi di sbroglio. Vanno poi associate le informazioni dei materiali usati nella composizione del pcb (spessori del rame e costanti dielettriche) ed i parametri parassiti dei componenti passivi della PDN. I CAD più sofisticati leggono direttamente le liste di componenti generate dai programmi di sbroglio (Bill of Material), associando a partire da un opportuno database i corretti valori di ESR ed ESL alla sigla del componente. Naturalmente l’intervento umano è necessario nell’impostazione della simulazione e nell’interpretazione dei risultati ma tutte le fasi possono normalmente essere gestite da flussi di lavoro distribuibili ai team di progetto, una volta messi a punto da un team di esperti. CAD cosi potenti non sono ovviamente limitati all’analisi della PDN, ma normalmente sono parte di ambienti di simulazione usabili anche in analisi integrate di Signal Integrity, Power Integrity ed Emissioni Elttromagnetiche, verificando forme d’onda propagate sulla board e cablaggi, crosstalk, riflessioni, emissioni elettromagnetiche. Il tipico formato di uscita di questi programmi è una serie di file dati e grafici che riproducono la risposta in frequenza delle strutture analizzate in termini di parametri S, in qualche caso direttamente convertibili in impedenze e confrontabili quindi con i target definiti. Ci sono varie buone ragioni per preferire questa rappresentazione, certamente familiare per ingegneri RF e microonde ma poco familiare ai progettisti digitali, di primo acchito. Detto in due parole, i parametri S (S sta per scattering, diffusione) descrivono il comportamento in frequenza dell’oggetto cui si riferiscono. Una buona e sintetica introduzione ai parametri S per progettisti digitali è richiamata in Rif. 9. Molti tools sw permettono anche di impostare studi per ottimizzare il costo dell’applicazione, verificando il contributo dei singoli condensatori ed aiutando a determinarne il numero minimo e la posizione ottimale. È anche possibile generare viste grafiche, eventualmente animate, dei campi elettromagnetici emessi, visualizzando i punti critici per l’emissione con mappe graduate. Il limite maggiore alla diffusione di questi strumenti è certamente il notevole costo degli ambienti di simulazione, unito alla necessaria supervisione di almeno alcuni utenti esperti. Sono tipicamente tools disponibili in grandi organizzazioni o aziende specializzate nella progettazione/verifica di sofisticate schede elettroniche.

MISURE

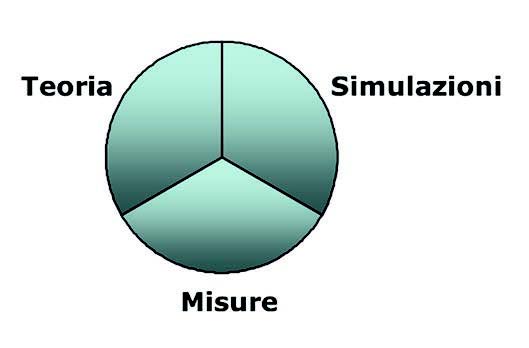

Si è persa memoria del nome della persona che ha per prima proposto la significativa relazione presentata graficamente in figura 6, l’autore sarebbe ben lieto di rendergli pubblicamente merito. In molti complessi settori delle moderne tecnologie elettroniche deve esserci sempre una stretta correlazione e coerenza tra teoria, simulazioni e misure, ciascuna a conferma e rafforzamento delle altre due.

Figura 6: relazione tra Teoria, Simulazioni, Misure.

Eliminare uno dei tre elementi porta a situazioni non totalmente sotto controllo, con possibili rischi di mancanza di robustezza del progetto e possibili brutte sorprese in stadi molto avanzati dello sviluppo, magari direttamente in produzione. Anche il nostro caso, Power Integrity, non fa eccezione e, per quanto sofisticati siano i tools di simulazione ed accurata la metodologia di progettazione, la conferma finale sui prototipi attraverso misure è fondamentale. Auspicabilmente, se il lavoro precedente è stato svolto correttamente, le misure si limiteranno a confermare la validità del progetto. Le misure e verifiche opportune sul prototipo sono molteplici:

- Misura diretta dell’impedenza della PDN

- Misura del rumore totale sulle alimentazioni.

VERIFICHE FUNZIONALI

La misura dell’impedenza non è di norma necessaria su tutti i singoli prototipi, ma è bene sia disponibile come tool di debug in caso di problemi. è inoltre fondamentale disporne per scopi di ricerca e sviluppo, nella messa a punto e verifica delle regole di progetto da ap plicare poi sistematicamente (generazione di Guidelines). Anche in questo caso incontriamo uno strumento proveniente dal mondo RF/Microonde, l’Analizzatore Vettoriale di Reti (VNA Vector Network Analyzer). Il VNA è uno strumento usabile per determinare la risposta in frequenza del dispositivo sotto test. Lavora applicando uno sweep di onde sinusoidali, acquisendo ed analizzando le onde riflesse e trasmesse attraverso il dispositivo. È in grado di fornire modulo e fase dei parametri di diffusione (Parametri S), permettendo di ricavare impedenze, guadagni, induttanze, capacità, attenuazione. Un ottimo tutorial su questo tipo di strumenti è indicato in Rif. 8. L’uso del VNA nella verifica di PDN non è privo di problemi purtroppo, vedi Rif 7 per una trattazione molto accurata dell’argomento. La prima difficoltà consiste nel fatto che lo strumento ha impedenza d’ingresso/uscita di 50 ohm, mentre l’impedenza presentata da molte PDN è solo una frazione di ohm. La connessione dello strumento va inoltre accuratamente progettata. Certamente questo strumento non è accessibile in tutti i laboratori, possiamo quindi anche in questo caso cercare di supplire con fatica e lavoro alla mancanza utilizzando un generatore di segnali a larga banda ed un oscilloscopio adeguato, per eccitare la PDN e ricavarne la risposta in frequenza, anche se in modo grossolano. La verifica del livello di rumore sulle alimentazioni è il criterio principe che ci dice se la nostra apparecchiatura è in specifica o meno. Il rumore viene misurato con un oscilloscopio a larga banda e possibilmente persistenza digitale, lasciato connesso a lungo all’applicazione funzionante. L’idea è catturare il rumore durante l’esecuzione di tutte le funzioni dell’apparato, accumulando sullo schermo una banda luminosa rappresentante il rumore picco-picco, banda che non deve eccedere i limiti di tensione definiti a specifica. La misura è descritta in dettaglio in Rif. 6. Notare il suggerimento di rimuovere un condensatore per prelevare il segnale senza che questo venga cortocircuitato in ac dal componente. Verifiche funzionali quali l’analisi dell’ “eye diagram” su linee di trasmissione dati completano la verifica, dimostrando l’assenza di jitter che provoca “chiusure” e deformazioni dell’occhio, rappresentante l’area di lavoro tempo/livelli di tensione.

CONCLUSIONE

Questa miniserie ha voluto costituire una introduzione al tema Power Integrity ed alle sue problematiche, dimostrandone l’importanza per il successo di un moderno progetto e fornendo spunti per approfondire e adattare tecniche e soluzioni al proprio campo di applicazione. L’accurata progettazione elettrica della PDN si somma alla considerazione di parametri di potenza, termici, meccanici, compatibilità elettromagnetica, costo ed affidabilità nella mo derna concezione di progettazione di sistema, attenta a priori ad ogni aspetto potenzialmente critico. Abbiamo visto come la cultura di progettazione digitale sia sfidata a confrontarsi con il dominio della frequenza e le sue, apparentemente, esotiche tecniche e strumenti, arricchendo il nostro bagaglio in modo certo inatteso fino a poco tempo fa.

Il Power Integrity si presta bene all’ottimizzazione della progettazione dei sistemi. Il processo di progettazione non è sempre lineare, prevedendo molto spesso un vero e proprio loop per ricercare i parametri ottimali di un’applicazione o di un sistema.

Articolo davvero interessante, a completamento del prima parte che per chi fosse interessato all’argomento e non l’avesse ancora fatto, ne consiglio vivamente la lettura.

Come giustamente è stato ben evidenziato in entrambi gli articoli, la PCB non va vista solo come un mero supporto fisico ai componenti messi tra loro in collegamento, ma è essa stessa un componente e quindi va progettata come tale. La progettazione della PCB, dopo lo schema elettrico e la scelta dei componenti, rappresenta la vera linea di confine che divide il mondo dei professionisti di settore da quello degli appassionati / maker. Gli aspetti tecnici portati alla luce dall’articolo coprono una grossa fetta delle competenze tecnico-progettuali necessarie per la progettazione di una PCB secondo le specifiche date.

Io sono un progettista elettronico, e in quanto tale ho letto l’articolo con estremo gusto rinfrescando tutte le considerazioni alla base dei vari metodi spesso utilizzati per avere uno sbrogliato di PCB che accoglie i requisiti di affidabilità anche per quanto riguarda la distribuzione delle alimentazioni e quindi la PDN. Quando si sale su con la frequenza o si hanno circuiti in parte o totalmente digitali governati da un segnale di clock a fronti sufficientemente rapidi e ripidi, la distribuzione delle alimentazioni diventa il primo aspetto progettuale a cui prestare la massima attenzione, a seguire il bilanciamento delle track per la distribuzione dei segnali di sincronismo e la separazione delle masse.

Al di là del taglio altamente tecnico conferito all’articolo, che ribadisco ritengo ben elaborato e strutturato, mi verrebbe da consigliarne la lettura anche per chi all’elettronica si è approcciato tramite le schede simil-Arduino e la prototipazione tramite breadboard, almeno per avere l’idea di cosa ci sia dietro questo mondo e del perché molto spesso circuiti particolarmente spinti in frequenza non siano adatti ad una prototipazione fatta con componenti a reofori e cavetti jumpers.