Un Digital Signal Processor in sigla DSP, è un microprocessore ottimizzato per eseguire efficientemente sequenze di istruzioni ricorrenti nel condizionamento di segnali digitali. in questo articolo ne scopriremo l’architettura.

DSP utilizzano un insieme di tecniche e algoritmi che permettono di trattare un segnale continuo dopo che è stato campionato. L’elaborazione dei segnali digitali è definita come la scienza che rappresenta i segnali con una sequenza di numeri ed elabora tali numeri per estrarre informazioni o modificare, in modo opportuno, i segnali in questione. I processori che caratterizzano tali operazioni sono noti come DSP (Digital Signal Processors). In generale, si possono distinguere fondamentalmente due approcci all’elaborazione digitale dei segnali: l’approccio mediante programmazione e l’approccio mediante realizzazione hardware.

» L’approccio mediante programmazione

In questo caso le caratteristiche di sistemi che trasformano segnali vengono simulate da programmi che vengono eseguiti da un elaboratore digitale. La velocità di esecuzione del programma dipende dal tipo di elaboratore ed in particolare dal livello di parallelismo e dalla velocità con cui vengono eseguite le istruzioni. Questo tipo di approccio risulta di grande flessibilità: sistemi totalmente diversi vengono simulati sulla stessa macchina, semplicemente eseguendo algoritmi diversi.

» L’approccio mediante realizzazione hardware

In questo caso gli algoritmi che simulano i sistemi vengono realizzati in h/w con circuiti dedicati ad applicazioni specifiche (ASIC) o mediante circuiti programmabili (PLD). La velocità di elaborazione dipende dalla frequenza di clock e dalla propagazione dei ritardi nei circuiti logici. Questo approccio permette realizzazioni più efficienti delle soluzioni software, con velocità di elaborazione maggiore di un fattore 102, risultando tuttavia molto meno flessibile, in quanto la simulazione di un nuovo sistema costringe a ridisegnare e rimpiazzare gran parte del circuito.

I sistemi di elaborazione

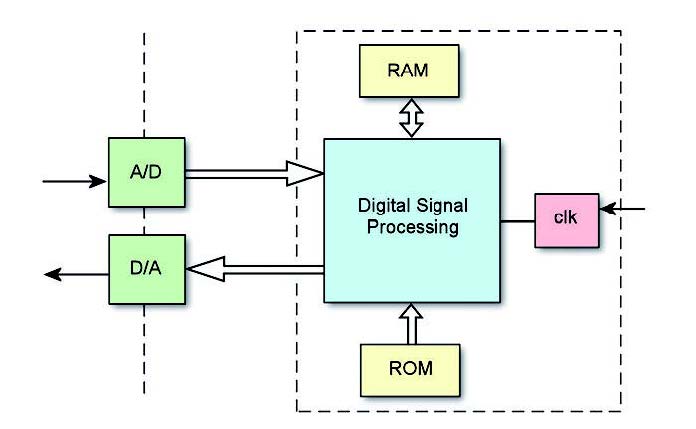

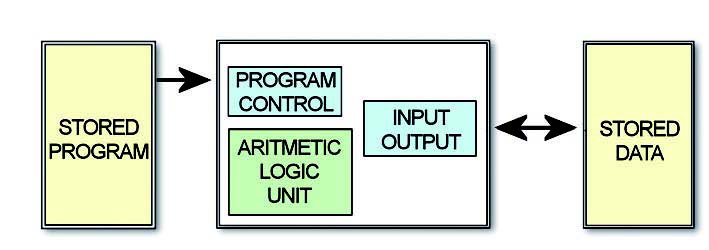

Un sistema d’elaborazione si comporta in modo analogo, acquisisce i segnali ed elabora questi ultimi estraendone le informazioni volute. La natura dei segnali reali è di tipo analogico e per poterli trattare, nella loro forma originale, dobbiamo impiegare sistemi analogici. Purtroppo questi sistemi hanno delle limitazioni piuttosto rilevanti rispetto ai moderni sistemi digitali, ed è per questo motivo che i segnali vengono preventivamente digitalizzati e successivamente trattati con processori digitali. I sistemi digitali sono insensibili al cambiamento dei parametri ambientali (temperatura ed umidità) ed inoltre sono indipendenti dalla durata dei componenti che costituiscono il sistema. Il vantaggio diretto che ne deriva è rappresentato dalla ripetitività e predicibilità dei risultati che i sistemi digitali danno in ambienti diversi. Altri vantaggi, di non minore importanza, riguardano la riprogrammabilità dei processori e quindi di un sistema digitale, infatti, riconfigurare il sistema per un’altra funzione comporta una semplice riprogrammazione software. Un tipico sistema di elaborazione digitale è rappresentato dalla figura 1.

Figura 1: sistema di elaborazione digitale.

I principali componenti sono:

» Convertitori analogici digitali A/D.

» Convertitori digitali analogici D/A.

» Memoria RAM.

» Processore dei segnali digitali DSP.

» Memoria ROM.

I microprocessori programmabili per l’elaborazione digitali dei segnali possono essere raggruppati nelle seguenti categorie: microprocessori general-purpose, microcontrollori, processori specializzati all’elaborazione dei segnali (DSP).

» Microprocessori general-purpose. Questi microprocessori devono supportare le più disparate applicazioni, quindi la loro architettura viene progettata per l’ottimizzazione della gestione della memoria; le loro prestazioni nell’elaborazione digitale dei segnali risultano tuttavia mediocri.

» Microcontrollori. Questi strumenti implementano singole parti di un elaboratore, ad esempio apparecchi per l’input-output, memorie RAM e ROM; l’architettura è generalmente funzionale all’ottimizzazione delle caratteristiche input-output.

» Processori specializzati all’elaborazione dei segnali (DSP). Questi microprocessori sono appositamente studiati per ottimizzare le prestazioni nell’elaborazione dei segnali. Poiché gli algoritmi per la simulazione di sistemi per segnali consistono spesso nella iterazione di sequenze di semplici operazioni aritmetiche, grande attenzione è posta nell’ottimizzazione dell’unità aritmetico-logica (ALU): i primi DSP sono addirittura stati motivati dalla necessità di accelerare l’esecuzione dell’operazione di moltiplicazione, rispetto agli usuali microprocessori. La necessità di grande velocità di elaborazione imposte dalle applicazioni in tempo-reale richiede inoltre l’introduzione di architetture che sfruttino l’inerente parallelismo di alcune funzionalità, pur sacrificando la semplicità realizzativi e la flessibilità rispetto alle applicazioni.

I DSP

Il DSP rappresenta il cuore del sistema di elaborazione digitale; vediamo quali requisiti deve soddisfare:

» Processori Real Time: sul mercato esistono svariati tipi di processori ognuno dei quali presenta diverse caratteristiche e quindi diversi livelli di prestazioni. Nell’elaborazione digitale “real-time” di segnali,

l’attenzione maggiore viene posta sull’ammontare delle elaborazioni completate in un tempo limitato, rappresentando, dunque, un vincolo stringente per i DSP. Sebbene con i processori dell’ultima generazione si sono fatti passi da gigante (processori con clock ad oltre 1.000 MHz), trattare segnali come suoni o immagini in movimento, resta pur sempre un compito non adatto a tali dispositivi. Il motivo principale sta nella diversa architettura indipendentemente dalla frequenza del clock.

» Architettura DSP: i DSP costituiscono un punto di unione tra i microprocessori ASIC ed i microprocessori general purpose; combinando la velocità dei circuiti specializzati ASIC con la convenienza dei processori riprogrammabili general purpose. La potenza di calcolo e la flessibilità dei DSP consente il loro impiego per un vasto intervallo di applicazioni (industriali e telecomunicazioni). Tutti i processori digitali consistono di alcuni moduli fondamentali:

» Unità di elaborazione per operazioni aritmetiche e logiche (ALU).

» Memoria per memorizzare i dati e le istruzioni del programma.

» Un bus per trasferire efficientemente dati e istruzioni tra la memoria e l’unità aritmetico logica.

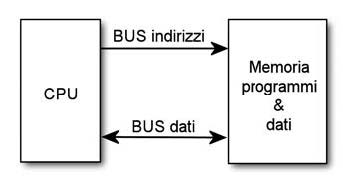

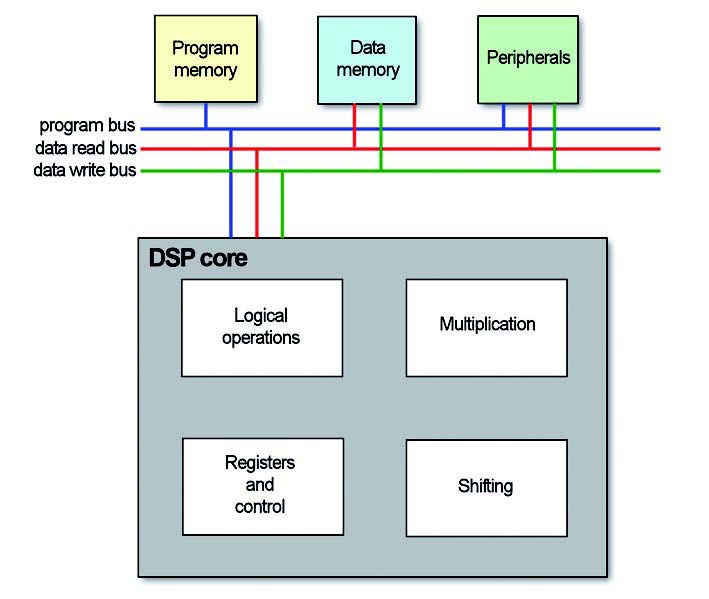

Per quanto detto, i DSP richiedono architetture di calcolo piuttosto differenti rispetto agli usuali microprocessori general-purpose. Un elaboratore programmabile riceve in ingresso dati di due diversi tipi: istruzioni per il programma e dati veri e propri. La maggior parte dei microprocessori general-purpose è basata sull’architettura proposta da Von Neumann e realizzata per la prima volta nel 1951 in cui dati e programmi vengono memorizzati nella stessa area di memoria (figura 2).

Figura 2: architettura Von Neuman.

Esiste un’unica area di memoria per dati e programmi, ed il processore usa gli stessi bus dati e indirizzi per accedervi. Le unità basilari sono l’unità aritmetico-logica (ALU) e l’unità di input-output (IO). La ALU permette l’esecuzione di operazioni aritmetiche, mentre l’unità di input-output gestisce il flusso di dati esterni alla macchina. Per questo tipo di macchina, i programmi sono sequenze di istruzioni e la singola istruzione generalmente contiene un comando di operazione e l’indirizzo del dato su cui il comando deve essere eseguito. Lo svantaggio di questa architettura è causato dal possedere un unico canale di comunicazione tra memoria ed ALU, quindi per effettuare un’operazione bisogna prima prelevare l’istruzione e poi prelevare i dati, il tutto comporta un doppio accesso in memoria e di conseguenza un minimo di due cicli macchina (due impulsi di clock). Nonostante questa limitazione, i processori costruiti secondo l’architettura di Von Neumann, trovano un largo impiego nella costruzione di processori general purpose. Un’architettura alternativa che permette un aumento di velocità, è l’architettura di Harvard, proposta negli anni trenta (figura 3).

Figura 3: architettura Hardward

Questa architettura prevede due spazi di memoria, uno per i dati, l’altro per i programmi, e corrispondentemente diversi bus dati e bus indirizzi per accedervi. Questa architettura permette di accedere contemporaneamente sia ai dati che alle istruzioni, ottenendo migliori prestazioni in velocità. L’architettura Harvard aumenta la velocità di esecuzione, ma introduce alcuni svantaggi:

» Le componenti hardware sono più complesse rispetto a quella di Von Neuman.

» Per ottimizzare le istruzione le istruzioni devono essere prelevati ed eseguito in uno stesso ciclo macchina.

I processori DSP possono essere raggruppati in due distinte categorie:

» virgola mobile (floating-point)

» virgola fissa (fixed-point).

I DSP in virgola fissa (figura 4) sono caratterizzati dal rappresentare un numero in un intervallo fissato con precisione finita. Il principale vantaggio offerto da questi processori è il relativo costo di produzione e, per tale motivo, viene molto impiegato per applicazioni industriali.

Figura 4: DSP virgola fissa

I DSP in virgola mobile sono più recenti di quelli in virgola fissa ed esprimono i numeri impiegando una mantissa combinata con un esponente. Questo metodo di rappresentazione comporta una serie di vantaggi quali un intervallo di rappresentazione dinamico, un errore relativamente piccolo ed una bassa probabilità che occorra overflow. D’altro canto, questi processori, sono piu’ lenti e costosi rispetto alla controparte in virgola fissa.

Istruzioni base di un DSP

Per ottenere alta velocità di esecuzione è necessario prelevare, decodificare ed eseguire ogni istruzione nel più breve tempo possibile. Gli approcci-limite tradizionali che vengono seguiti nella progettazione di un microprocessore a questo riguardo sono:

Approccio VLIW (Very Long Instruction Word). Viene previsto un insieme di istruzioni di base molto grande, in modo che risolvere un problema richieda programmi con poche istruzioni (più cicli di clock) Approccio RISC (Reduced Instruction Set). Si sceglie di implementare in questo caso solo un piccolo insieme di istruzioni di base. In questo modo la scrittura di un programma richiede più istruzioni, ma ogni istruzione può essere codificata con una sola parola dell’area programmi (un solo ciclo di clock).

La richiesta di poter prelevare ed eseguire una istruzione in un singolo ciclo di clock comporta che la lunghezza della parola che codifica l’istruzione non superi la dimensione del bus di programma. Tale parola contiene due parti: la codifica dell’operazione che deve essere applicata (parte operazione) e l’indirizzo della locazione di memoria cui l’operazione va applicata (parte operando). I bit della parte operazione limitano il numero di istruzioni possibili; la parte operando può essere definita usando differenti modi di indirizzamento, ognuno dei quali consuma diversi bit nella parola che codifica l’istruzione. A causa dei limiti alla lunghezza di tale parola, non tutti i modi risultano disponibili nei processori specializzati per l’elaborazione dei segnali; vediamone alcuni:

» Indirizzamento diretto: In questo caso l’operando specifica direttamente l’indirizzo della locazione di memoria cui applicare l’operazione.

» Indirizzamento indiretto: In questo caso l’operando specifica quale registro-indirizzi dell’unità centrale punta alla locazione di memoria cui applicare l’operazione .

» Indirizzamento indiciato: In questo caso l’operando specifica un valore di riferimento v e un registro-indice dell’unità centrale.

» Indirizzamento circolare: Algoritmi per l’elaborazione dei segnali fanno spesso uso di buffer first-in first-out (code FIFO). Per semplificare l’uso di tali strutture dati, molti DSP contengono un registropuntatore che supporta il modo di indirizzamento modulo: il contenuto di tale registro è un intero modulo m, cioè resto della divisione di tale intero con m, in modo tale che il registro punti sempre a uno di m indirizzi consecutivi.

» Altri modi di indirizzamento: Nell’elaborazione dei segnali ci sono algoritmi di base che vengono richiamati frequentemente: può essere allora utile prevedere modi di indirizzamento orientati all’esecuzione efficiente di tali algoritmi.

Integrazione dei componenti DSP

La richiesta di eseguire ogni istruzione in un singolo ciclo di clock comporta la necessità di realizzare su un singolo chip di silicio il processore, l’area di memoria per i dati, l’area di memoria per i programmi e i rispettivi bus. Nei DSP vengono così integrate su un singolo chip molte delle componenti di un tradizionale computer. Questo pone severe limitazioni alla capacità di memoria dei DSP; fortunatamente, un gran numero di applicazioni richiede programmi con solo poche migliaia di istruzioni e dati per poche migliaia di parole. Tra le apparecchiature fondamentali che rendono possibile l’elaborazione digitale vanno ricordati i convertitori analogico-digitale (ADC) e digitale-analogico (DAC): interfacciare in modo efficiente il processore digitale con i convertitori ADC e DAC è di grande importanza per una efficiente elaborazione. Sono proposte due soluzioni hardware:

» integrazione dei convertitori ADC e DCA nello stesso chip del DSP: limitazioni nelle prestazioni;

» presenza di hardware speciale per interfacciare efficientemente convertitori e DSP: include una porta seriale per trasferimento dati, numero ridotti di pin e possibilità di realizzare convertitori a 24 bit e oltre.

Un esempio di DSP

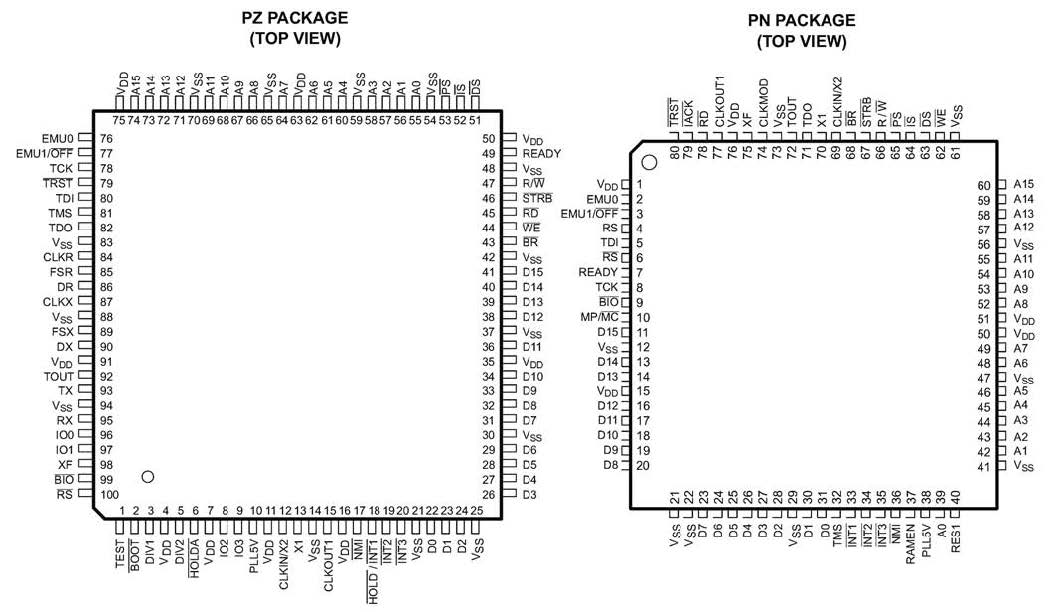

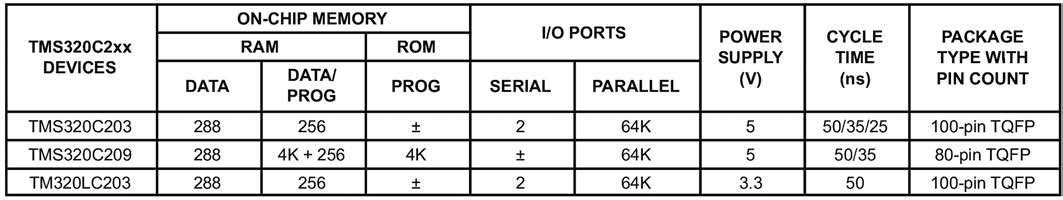

In commercio ci sono tantissimi tipi di DSP, vediamone in dettagli. Un DSP molto comune è quello della Texas TMS320C2xx (figura 5 e 6) con architettura Hardward ottimizzato per alte velocità.

Figura 5: il TMS320C2xx.

Figura 6: il TMS320C2xx

Caratteristiche principali sono le seguenti:

» 16 bit Fixed point DSP

» PLL con clock variabile

» 32 bit ALU

» 4 External Interrupt

» Memory Space: 64K programmi, 64K data, 64K I/O, 32K Global.

Include una porta seriale per comunicazioni con dispositivi esterni. In figura 7 le principali caratteristiche elettriche del DSP in questione.

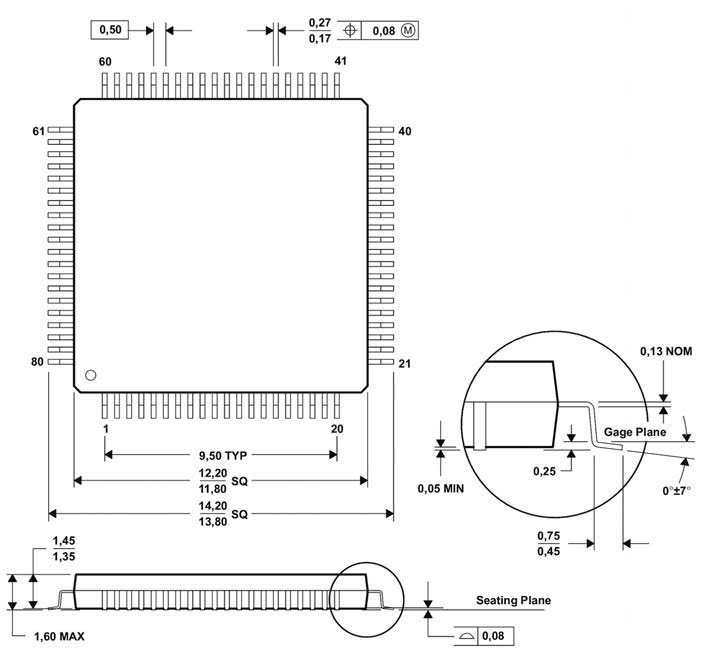

Figura 7: caratteristiche elettriche principali del TMS320C2xx.

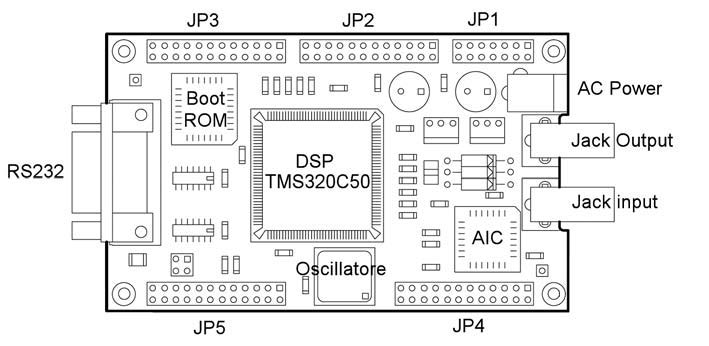

Un altro DSP della Famiglia Texas è il DSK TMS320C50 a virgola fissa (figura 8):

» Processore DSP TMS320C50 a 40 MHz con 10K Words di RAM e 2K Words di ROM integrate su chip.

» TLC320C40 circuiteria di interfaccia analogica (AIC) con una risoluzione di 14 bit (un solo chip per A/D e D/A).

» Porta seriale RS232 per la connessione al PC.

» Due jack standard RCA per la comunicazione diretta con dispositivi analogici.

» Eprom (32K words) su scheda per inizializzare la comunicazione tra DSP e PC.

Figura 8: DSP TMS320C50.