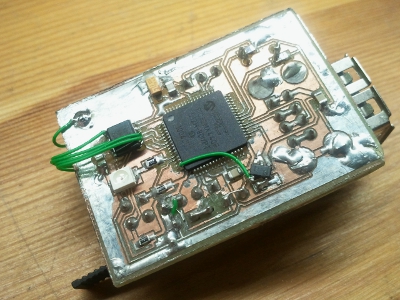

Questa recensione nasce dalla possibilità e dallo spunto datoci dall'Elettronica Open Source. I processori ARM (Advanced RISC Machine) come quelli MIPS (Microprocessor without Interlocked Pipeline Stages ) sono moltissimi e non ci è possibile effettuare una comparazione per tutti i modelli; in questa recensione troverete la comparazione tra 2 microcontrollori che stanno nella stessa fascia di costo e frequenza di lavoro. Per la prova in esame abbiamo a disposizione lo starter kit di iSystems composto da debugger (nome) + ARM LPC2138 che dispone di un core ARM7TDMI-S e di una nostra scheda con a bordo un PIC 32MX440F512H che invece ha un core MIPS32 M4K.

Analizziamo le caratteristiche tecniche dei due microcontrollori per capire meglio ciò che stiamo per andare ad analizzare.

Architettura – Introduzione

Di seguito faremo riferimento alle due architetture in base a come sono state integrate all’intero dei due microcontrollori; il clock di un core MIPS32M4K (Relase 2) per esempio, può arrivare fino a 400MHz ma in questo PIC è operante al massimo a 80MHz.

Entrambi i micro supportano un set istruzioni di 16 bit e si basano su un architettura RISC.

PIC32MX differisce dai precedenti modelli di PIC perchè offre un modello di programmazione Von Neumann anziché Harvard. I PIC32 però sono basati sul core MIPS32 che è basato sul modello dell’architettura Harvard... il dilemma è presto risolto.

Di fatto sappiamo che cè un modello per il core e un modello per il sistema di programmazione dei PIC32.

Il core M4K è basato sull’architettura Harvard e ha due bus paralleli per istruzioni e dati (I e D). Questo permette di eseguire contemporaneamente operazioni di fetch mentre legge o scrive dati verso la ram. Contrariamente a tutti gli altri modelli precedenti la separazione tra i due bus cambia completamente e il PIC ci si presenta come un microcontrollore con architettura Von Neumann. Infatti, c’è un singolo spazio degli indirizzi dove dati e programma risiedono.. dati e programma sembrano provenire dallo stesso bus.. Il “bus matrix” si occupa di questo aspetto ! Il bus Matrix risiede tra il bus di sistema che è collegato con le memorie e le periferiche (è un singolo bus Von Neumann) e il core tramite la cache (core e cache sono connessi da due bus separati (I e D) quindi con tecnologia Harvard.)

Oltre al core, dispone di : Execution Unit, Multiply/Divide Unit (MDU), System Control Coprocessor (CP0), Fixed Mapping Translation (FMT), Dual Internal Bus interfaces, Power Management, MIPS16e Support, Enhanced JTAG (EJTAG) Controller.

Multiply/Divide Unit (MDU): Contiene una pipeline separata per effettuare divisioni e moltiplicazioni. Questa pipeline opera in parallelo alla integer unit(IU) pipeline e non va in stallo quando ci và la IU. Questo permette operazioni MDU di essere parzialmente mascherate dagli stalli di sistema e/o altre istruzioni IU. Questa MDU effettua moltiplicazioni 16x16 e 32x16 con un singolo passaggio, mentre necessita di due passaggi per eseguire moltiplicazioni da 32x32 bit.

Le operazioni di divisione sono implementate con un semplice algoritmo iterativo che processa 1 bit per clock.

System Control Coprocessor (CP0): Nell’architettura MIPS, CP0 è responsabile della traslazione degli indirizzi da virtuali a fisici, il controllo delle eccezioni (errori di allineamento, nei dati, eventi esterni o errori del programma), il livello di esecuzione(kernel, user, debug) e anche degli interrupt. L e informazioni di configurazione come MIPS16e, sono disponibili accedendo ai registri di CP0.

ARM7TDMI-S Hanno un architettura Von Neumann con un singolo bus a 32 bit per i dati e per le istruzioni.

LPC2138 si basa su core di tipo ARMv4T in cui il set istruzioni e il relativo meccanismo di decodifica permettono un alto livello di throughput e un impressionante risposta degli interrupt in real-time. A fianco del core, troviamo il blocco MAM(Memory Accelerator Module) che maximiza le performance dei processori ARM quando il codice viene eseguito nella flash. In sostanza, il MAM attende di avere la prossima istruzione ARM che sarà necessaria nei suoi latch in tempo per prevenire stalli nel fetch da parte della CPU. Include 3 buffer da 128 bit chiamati Prefetch Buffer, Branch Trail Buffer e data buffer. Il prefetch e il Branch Trail buffer e includono, ognuno, 4 istruzioni da 32 bit o 8 da 16 in Thumb mode. Durante l’esecuzione sequenziale tipicamente, il prefetch buffer contiene l’istruzione corrente e l’intera linea della flash che la contiene. Il MAM differisce se si sta facendo un accesso a dati o ad istruzioni. l’accesso ai dati e alle istruzioni usano buffer da 128 bit separati.

I Branch o altre operazioni che causano un cambiamento nell’esecuzione del codice, interrompono il funzionamento del fetch appena descritto. Il Branch Trail Buffet cattura la linea alla quale si verifica l’interruzione e se la stessa istruzione di interruzione viene eseguita ancora, la prossima istruzione viene presa dal Branch Trail Buffer. Quando un branch fuoriesce dal contenuto del Prefetch e del Branch Trail Buffer, è necessario uno stall di vari clock per caricare il Branch Trail Buffer.

In questo chip non è stato implementato nessun coprocessore.

Architettura – Pipeline

Incrementando il numero di stadi della pipeline, incrementa il parallelismo nel design e riduce la quantità di logica che deve essere valutata con un singolo periodo di clock. Una pipeline con pochi stadi semplifica il design, mantiene i consumi ridotti, implica un minore uso di transistor e riduce la dimensione del die. Questo però, limita anche la massima frequenza di clock.

PIC32MX3/4XX ha una pipeline a 5 stadi. Essi sono : Instruction (I) Execution (E), Memory (M), Align (A), Writeback (W).

Stadio I: Durante questo stadio, le istruzioni sono fetchate from SRAM. Le istruzioni MIPS16e sono convertite in istruzioni compatibili MIPS32.

Stadio E: Durante questo stadio gli operandi sono fetchati dal file register, gli operandi dallo stadio A e M sono bypassati a questo stadio, La ALU comincia le operazioni logiche o aritmetiche per le operazioni register-to-register; la ALU calcola gli indirizzi virtuali della memoria dati per le istruzioni di load e store e la MMU provvede alla traslazioni degli indirizzi da virtuali a fisici; La ALU determina se la condizione di branch è vera e calcola il branch virtuale per l’istruzione di branch; La logica delle istruzioni seleziona un indirizzo delle istruzioni e la MMU effettua la traslazioni degli indirizzi da virtuali a fisici;

Tutte le istruzioni di moltiplicazione e divisione cominciano in questo stadio.

Stadio M: Si completano le operazioni aritmetiche o logiche; l’accesso ai dati della SRAM sono performed per le istruzioni di load e store; le operazioni MUL 16 x 16 o 32 x 16 vanno in stallo per un clock nello stadio M per completare il “carry-propagate-add” in questo stadio; Le operazioni di moltiplicazione e divisione procedono nella MDU memorizzando il risultato in un registro temporaneo finché IU muove le istruzioni nello stadio A .

Stadio A: Il registro separato di allineamento carica i dati; le operazioni MUL creano il risultato per lo stadio W. L’attuale registro W, è performed nello stadio W.

Da questo stadio, i dati caricati o i risultati from MDU, sono disponibili nello stadio E per bypassaggio.

Stadio W: Per il “register-to-register” o per le istruzioni di load, il risultato è scritto nel registro appropriato. I core M4K implementano il meccanismo di Bypass che permette al risultato di un operazione di essere diretto all’istruzione che lo necessita senza dover scrivere il risultato in un registro per poi doverlo leggere.

LPC2138 ha una pipeline a 3 stadi che si chiamano Fetch, Decode ed Execute.

Nella fase di Fetch le istruzioni vengono fetchate. Nello stadio di Decode, le istruzioni Thumb vengono decompresse in istruzioni ARM, vengono decodificate le istruzioni ARM e vengono selezionati i vari registri. Nell’ultimo stadio, l’Execute,in un unico ciclo vengono letti gli operandi dai registri e passati tramite lo shift register alla ALU per poi venire scritti nei registri.

Tipicamente, mentre un operazione sta per essere eseguita, l’istruzione successiva sta per essere decodificata e la terza istruzione sta per essere fetchata dalla memoria. I processori ARM7TDMI-S implementano anche un’ esclusiva strategia d’architettura conosciuta come Thumb che permette di convertire le istruzioni in lunghezze da 16 bit anziché 32. Il Program Counter (PC) punta all’istruzione che è stata fetchata anziché a quella che verrà eseguita.

Architettura – Memory layout & organization

I PIC 32M3xx/4XX possono indirizzare 4GB di memoria virtuale unificata. La regione di memoria include memoria programma, memoria di boot (12k), dati, SFRs e i registri di configurazione. La memoria programma può essere partizionata in area kernel e area utente. In aggiunta, la memoria dati può essere resa eseguibile permettendo ai PIC32MX3/4XXX di eseguire il programma dalla memoria dati.

Sono implementati 2 spazi di indirizzi, virtuali e fisici. Tutte le risorse hardware come memoria programma, memoria dati e periferiche sono localizzati al loro rispettivo indirizzo fisico. Gli indirizzi virtuali sono usati esclusivamente dalla CPU per eseguire operazioni di fetch ed eseguire istruzioni come l’accesso alle periferiche. Gli indirizzi fisici sono usati delle periferiche come il DMA e il controller della Flash che accede alla memoria indipendentemente dalla CPU.

Internamente è presente una memoria flash per il programma per eseguire il codice utente che può essere programmata con : In-Circuit Serial Programming, Run-Time Self Programming e con EJTAG. La memoria flash è organizzata in 4 banchi di memoria.

LPC2138: Può indirizzare uno spazio di memoria lineare fino a 4GB. La regione di memoria di questo micro comprende vari sezioni, la memoria programma, interrupt (che può essere rimappata), la memoria di boot (12k), ram, e memoria APB e AHB per le periferiche. La memoria flash appare all’utente come un unico blocco ma in realtà è composta da due banchi.

Architettura – Frequenze di lavoro

PIC32MX440 La massima frequenza di lavoro per il core e per gli I/0 è di 80MHz. Sono disponibili varie sorgenti per il clock tra cui un clock interno di cui è possibile scegliere varie frequenze di lavoro fino a 8MHz. Internamente sono presenti 2 PLL, uno dei quali è dedicato esclusivamente all’ USB.

Il core esegue un ciclo macchina ogni 4 clock. Questi PIC, permettono di adottare un clock per le periferiche interne minore di quello usato dalla CPU per ridurre i consumi, in frazioni di 2,4 e 8 volte il clock di sistema. Alcune periferiche interne al micro possono continuare ad operare con un loro specifico clock mentre la cpu è in sleep.

Questi microcontrollori eseguono un’ istruzione ogni 4 colpi di clock.

La sorgente di clock può essere esterna ad esempio con quarzo, con rete rc, generatore di clock. Internamente sono presenti 2 oscillatori, uno da 8 MHz e l’altro da 32KHz.

LPC2138 ha un clock Massimo di 60MHz grazie al PLL che ha un tempo di setup di 100 uS. Anche per questo micro è possibile adottare tecniche di frequency scaling per le periferiche ed applicare un clock con frazioni che vanno da ½ a ¼ di quella del core.

La versione /01 è più performante in velocità, per esempio di 3.5 volte per quanto riguarda il toggle degli i/o.

I micro ARM, ad eccezioni di poche istruzioni, eseguono un’ istruzione ogni colpo di clock. Le sorgenti di clock possono essere con quarzo o con generatore di clock. Il quarzo può essere scelto nel range 1-30MHz, mentre il generatore di clock da 1 a 50MHz.

Le modalità RC esterna non è supportata e non è nemmeno presente un oscillatore interno che funzioni senza componenti esterni.

Il vantaggio della velocità di esecuzione nei micro ARM è che sono agevolati nell’eseguire certe operazioni come l’esecuzione condizionata(1) e il barrel shifter(2). Ecco la spiegazione:

(1) Quasi tutte le istruzioni dei processori ARM possono essere accompagnate da un codice di controllo, chiamato condition code, che modifica l'esecuzione dell'istruzione alla quale viene applicato. L'utilità dell'esecuzione condizionata si nota immediatamente esaminando questo frammento di codice:

// Codice C

if (a < b)a = a + b;

else a = a - b;

che in Assembly diventa:

cmp Ra, Rb ; confronta le due variabili settando dei flags interni in base al risultato

addlt Ra, Ra, Rb ; esegue la somma se LT (Less than)

subge Ra, Ra, Rb ; esegue la sottrazione se GE (greater or equal)

Da notare come in questo pezzo di codice non siano presenti salti, che invece sarebbero necessari per indirizzare il flusso di programma verso i rami di codice corretti, nel caso in cui mancasse la possibilità di effettuare istruzioni condizionate. In questo esempio si mostra come in soli 3 cicli di clock l'architettura sia in grado di eseguire un confronto, un'operazione di somma e un'assegnazione.

(2) Supponiamo di dover scrivere un pezzo di codice che esegua questa operazione:

a = b + c / 32;

In questo caso dobbiamo effettuare una divisione per 32 (che corrisponde ad uno shift aritmetico a destra di 5 bit), una somma e un'assegnazione. In teoria sarebbero 3 istruzioni separate, ma grazie alla potenza dell'architettura ARM riusciamo a scrivere tutto questo in una sola istruzione, che viene eseguita in 1 singolo ciclo di clock, vediamo come:

add Ra, Rb, Rc ASR#5 ; ASR sta per Arithmetic Shift Right, #5 è il numero di bit per lo shift

Architettura – Prefetch cache

PIC32MX La cache di prefetch incrementa le performance per l’esecuzione di applicazioni al di fuori delle regioni di memoria programma grazie all’implementazione di istruzioni di cache per le istruzioni, per costanti dati e prefech delle istruzioni.

Quando la CPU funziona ad alti valori di clock, gli stati di Wait posso no essere nascosti al core effettuando istruzioni di prefetch e store in un area temporanea in cui la CPU può accederci velocemente. Ci sono 2 funzioni principali a cui provvede la la cache di prefetch: mettere in cache le istruzioni quando non si ha a loro accesso e fare il prefetch delle istruzioni dalla PFM appena prima che serva. I dati che vengono richiesti dalla CPU possono essere o meno presenti nella cache.. in questo caso, la lettura è effettuata alla PFM al corretto indirizzo, i dati vengono spediti alla cache e alla CPU. La cache hit avviene se la cache contiene i dati che richiede la CPU. In questo caso, le informazioni vengono inviate alla CPU con un Wait stat pari a 0.

La seconda cosa più importante è il prefetch delle istruzioni. Il modulo calcola l’indirizzo dell’istruzione successiva ed effettua una lettura della PFM per ottenere i prossimi 16 byte da inserire nella cache.

ARM7TDMI-S Le istruzioni di prefetch delle istruzioni sono eseguite nel primo ciclo della pipeline.

Architettura – DMA

Il controller DMA nei PIC32MX è un modulo bus master usabile per il trasferimento dati tra diversi dispositivi senza l’intervento della CPU. Sorgente e destinazione del modulo DMA possono essere scelti tra i vari dispositivi mappati.

LPC2138 non dispone di controller DMA.

Architettura – Load and Stores

PIC32MX3xx/4xx Questa famiglia di core implementa un architettura con caricamenti e salvataggi in un singolo ciclo macchina e un autonoma unità di moltiplicazione/divisione. Il core contiene 32 registri da 32 bit usati per le operazioni con numeri integer e di calcolo degli indirizzi. Un addizionale registro condiviso è stato inserito per minimizzare l’overhead durante il processamento di interrupt ed eccezioni. Questo registro consiste in due porte di lettura e una di scrittura ed è completamente bypassato per minimizzare la latenza delle operazione nella pipeline.

ARM

Gli operandi sono sempre contenuti nei GPRs e le operazioni di load e store sono le uniche che coinvolgono la memoria.

Load Register: Questa istruzione può necessitare di un numero di cicli variabile:

Durante il primo ciclo, il processore calcola l’indirizzo da calcolare.

Durante il secondo ciclo il processore fetcha i dati dalla memoria e se richiesto esegue la modifica di base.

Durante il terzo ciclo, il processore trasferisce i dati nel registro di destinazione.

Load multipli:

Durante il primo ciclo, il core calcola l’indirizzo della prima word da trasferire mentre esegue un prefetch dalla memoria

Durante il secondo ciclo, il core fetcha la prima word ed esegue le modifiche di base se richieste.

Durante il terzo ciclo, il core sposta la prima word nell’appropriato registro di destinazione e fetcha la seconda word dalla memoria. Il terzo ciclo è ripetuto per i successivi fetch finche è stato fatto accesso all’ultima word.

Durante il quarto e ultimo ciclo interno, il core muove l’ultima word al suo registro di destinazione.

Store:

Durante il primo ciclo, il core calcola l’indirizzo di store.

Durante il secondo ciclo, il core esegue la modifica di base e scrive se richiesto, i dati nella memoria.

Store multipli:

Durante il primo ciclo, il core calcola l’indirizzo della prima word di cui deve effettuare lo store.

Durante il secondo ciclo, il core esegue la modifica id base e scrive i dati nella memoria.

Il core ha 32 registri da 32 bit. In ogni momento, sono visibili solo 16 di questi registri. Gli altri sono usati per velocizzare il processa mento delle exception. Qualsiasi istruzione ARM può indirizzare uno dei qualsiasi registri visibili.

Il banco principale con i 16 registri, è usato dal codice senza necessità di privilegi (User Mode).

Tre di questi sedici registri hanno una funzione speciale:

Stack pointer:Il software normalmente usa il registro 13 (R13) come stack pointer (SP).

Link Register: Il registro R14 è il Link Register. Questo registro memorizza l’indirizzo dell’istruzione successiva dopo un Branch o un Link (istruzioni assembler BL e BLX) che sono le istruzioni usate per chiamare una subroutine. In tutti gli altri casi, R14 può essere usato come un registro generico.

Program Counter: Il registro R15 è il Program Counter.

Architettura – Branches

PIC32MX3/4XX dispone di una logica per determinare i branch e per calcolarne i relativi indirizzi.

ARM7TDMI-S non implementano una logica per determinare i branch perchè su queste cpu è ragionevolmente economico in termini di opportunità perse di eseguire altre istruzioni. Questo significa che il costo della logica e l’incremento del die non è giustificato dalle performance che si otterrebbero facendolo.

Architettura – Interlocks

Il flusso regolare della pipeline è interrotto quando un’ istruzione nello stadio della pipeline non avanza perché dipende da altri dati o da altre simili condizioni esterne. Le interruzioni della pipeline sono gestite interamente in hardware. Queste dipendenze sono chiamate Interlocks. I compilatori e i pezzi di codice scritti in assembler, possono ridurre il numero di interlocks riordinando le istruzioni e le sequenze di codice.

Processori MIPS:

In generale supportano due tipi di interlocks hardware:

Stalli

Gli stalli sono risolti fermando l’intera pipeline. Tutte le istruzioni eseguite in questa situazione in ogni stadio della pipeline sono affetti da stallo.

Slips

Gli slpis permettono ad una parte della pipeline di avanzare quando un’ altra parte della pipeline è mantenuta statica.

Nei core PIC32MX, tutti gli interlocks sono gestiti come pause. Le pause sono minimizzate prendendo i risultati degli alti stadi della pipeline usando una tecnica conosciuta col nome id “register bypassing”

Degli Interlocks appropriati vengono implementati come stalli nel problema del back-to-back nelle moltiplicazioni 32 x 32 bit.

I compilatori ARM implementano ottimizazioni di scheduling per ridurre il numero dei cicli di interlock.

Architettura – Interrupt

Per entrambi i micro, gli interrupt possono essere abilitati o disabilitati singolarmente ad ogni periferica che li supporta. Possono anche essere impostati a diverse priorità.

PIC32MX Questa famiglia di microcontrollori implementa un efficiente e flessibile meccanismo di gestione dell’interrupt. Gli interrupt e le eccezioni sono simili in quello che riguarda il flusso di istruzioni eseguite per gestire interrupt o eccezioni. La differenza tra i due è che gli interrupt sono in generale un risultato di una normale operazione mentre le eccezioni accadono in condizioni di errore come per esempio errori sul bus interno al micro.

Permette di avere interrupt sul cambiamento di stato di alcuni pin, dalle periferiche ecc. Questa famiglia arriva a gestire fino a 95 richieste di interrupt (IRQ). Per ogni vettore d’interrupt è possibile impostare più priorità e sottopriorità.

Supporta l’interrupt vector singolo e multiplo.

ARM7 permette di avere una richiesta di interrupt da varie sorgenti che vengono classificate come FIQ se sono Fast Interrupt Request, IRQ se si tratta di vectored interrupt request e non-vectored IRQ se sono definiti dall’utente. E’ permesso di rimappare gli interrupt in RAM

Dispone del controller VIC (Vector Interrupt Controller) che provvede ad un addizionale supporto hardware. Senza questo controller, il tempo di risposta agli interrupt sarebbe veramente elevato.

Dispone di 2 linee esterne per gli interrupt FIQ e varie per interrupt IRQ. In genere, in un sistema ARM7 ideale, ci dovrebbe essere solo un interrupt FIQ per permettere al processore di entrare in interrupt ed eseguire il codice il più in fretta possibile. Questo significa che tutti gli altri interrupt devono essere connessi come IRQ.

Li interrupt IRQ si suddividono in Vectored e non vectored. Quelli Vectored (16 assegnabili), quando vengono generati, fanno saltare la cpu in una precisa locazione di memoria. Gli altri IRQ invece devono essere testati uno ad uno per vedere quale di essi si è generato ed eseguire il relativo codice.

Architettura – Operating Mode

PIC32MX dispone di 9 metodi e modi per bilanciare il consumo di energia e le performance del dispositivo. Sono raggruppabili in due categorie. In tutti questi metodi e modi, il risparmio di energia è controllato dal software.

Quando la CPU sta lavorando, il consumo di energia può essere ridotto riducendo la frequenza di clock e disabilitando individualmente i moduli non necessari.

Quando la CPU è ferma, il microcontrollore può adottare due modi per risparmiare energia: sleep e idle mode. In sleep mode il clock principale viene arrestato; alcune periferiche possono funzionare con un clock specifico. In idle mode, il clock è funzionante ma a frequenza più basse.

Per ridurre i consumi, ogni periferica può essere fermata o disabilitata.

ARM7 ha 7 differenti modalità operative. L’applicazione viene eseguita normalmente in user mode con accesso ai registri R0-R15 e al registro CPSR. In risposta ad un eccezione come per esempio ad un interrupt, memory error o altro, il processore può cambiare modalità di funzionamento. Quando questo accade, i registri da R0 a R12 e r15 rimangono gli stessi ma R1 e R14 vengono rimpiazzati da una nuova coppia unica in ogni modalità. Questo significa che ogni modalità ha il suo stack e link register. In aggiunta, la modalità fast interrupt (FIQ) ha i registri R7-R12 uplicati. Questo permette di entrare in interrupt senza preservare il contenuto dei registri nello stack.

Benchmark – Whetstone

Il Whetstone invece è nato nel 1972 per misurare la velocità e l’efficienza con cui un calcolatore esegue operazioni in virgola mobile.

Il valore di FLOPS esprime il numero di operazioni in virgola mobile al secondo.

Benchmark – Dhrystone 2.1

Il Dhrystone è un benchmark ideato nel 1984 per misurare e confrontare le prestazioni dei calcolatori. È composto da un codice standard, non impiega operazioni in virgola mobile e lavora sulle stringhe. Il risultato di questo benchmark è il numero di Dhrystone al secondo, cioè il numero di iterazioni del codice presente nel main al secondo. Il Dhrystone cerca di rappresentare il risultato meglio di quanto possa esprimere il risultato dei MIPS (milioni di istruzioni al secondo) di un processore perché non è possibile comparare il numero di istruzioni eseguite al secondo in architetture differenti (RISC e CISC per esempio).

Un’ altra rappresentazione comune è il valore espresso in DMIPS (Dhrystone MIPS) ottenute dividendo il valore Dhrystone per 1757.

Il punteggio ottenuto conta solamente il numero di iterazioni del programma permettendo ai processori in test di eseguire del codice ottimizzato; in questo benchmark influisce enormemente la qualità del compilatore utilizzato.

PIC32MX3XX/4XX: come da datasheet è dichiarato 1.56 DMIPS/MHz

ARM7TDMI-S: In rete abbiamo trovato documentazione che attesta per il LPC2103 che si basa su questo core, che a 70MHz ottiene un punteggio di 63DMIPS quindi 0.9DMIPS/MHz.

Benchmark – CoreMark

Introduzione

Questo benchmark testa la pipeline del processore, memoria e cache se presente e operazioni su numeri interi. Il CoreMark non è basato una reale applicazione, ma le operazioni eseguite durante il benchmark riguardano algoritmi tipicamente usati nelle applicazioni reali come la manipolazione di liste ( per testare l’uso di puntatori), operazioni su macchina a stati (per testare i branch) e il calcolo di CRC che è una tipica funzione richiesta nei sistemi embedded.

Abbiamo scelto di misurare le performance tra questi due micro con questo benchmark perchè:

la maggior parte del codice del Dhrystone è suscettibile a ottimizazzioni da parte del compilatore. Questo rende molto difficle comparare diversi micro compilano il codice con differenti compilatori e diversi flag per il compilatore.

Le chiamate di libreria nel Dhrystone consumano la magigor parte del tempo di questo benchmark. Se le libbrerie usate non fanno parte dle benchmark, è difficile comparare i risultati.

Il codice Dhrystone è sintetico e non corrisponde ad un’ applicaizone tipica reale.

La descrizione è veramente vaga e ambigua riguardo a come il codice Dhrystone debba essere eseguito e riguardo a come debbano essere riportati i risultati

Non cè un sorgente ufficiale e cè chi usa la versione 1.1, 2.0, 2.1 senza dichiarare quale ha usato per ottenere quei risultati.

Ci sono delel guidelinea su come eseguire il Dhrystone ma ai più non sono conosciute.

Non cè una standarizazzione di copme riportare i risultati del Dhrystone (DMIPS, DMIPS/MHz, Dhrystone al secondo)

Anche se il compilatore può trovare la via più efficiente per processare il codice di questo benchmark, il codice in sé esegue istruzioni che non possano essere ottimizzate.

Include la documentazione completa per il supporto e le guide linea per essere eseguito.

Setup

Per poter eseguire il benchmark è necessario registrarsi su http://www.coremark.org/. Dopo la conferma arrivata per email si può scaricare il file “coremark_v1.0.tgz” che include i file base del benchmark. Son disponibili online dei porting come quello per la serie LPC17xx e PIC32.

Ci siamo accorti però che il porting presente per PIC32 era stato scritto per funzionare con il PIC32MX KIT che precvedera di riportare i risultati tramite la porta usb presente a bordo scheda. Noi lo abbiamo riadattato per scrivere i risultati sulla porta seriale.

Per il porting per il LPC17XX, per essere portato per il LPC21XX, bisogna modificare i registri del timer 0, infatti in questa nuova serie, nel file include sono chiamati e strutturati diversamente.

Per ogni porting bisogna controllare come è stato portato il codice, per esempio per quello relativo alll’ARM, veniva calcolato il valore di un registro basandosi su una frequenza di lavoro di 72MHz.

Questi sono i risultati ottenuti dal nostro benchmark:

PIC32MX3XX/4XX:

Processor Operating Frequency: 80MHz

Memory configuration: Code in FLASH (0 wait-state), data in RAM (Stack)

Compiler name and version : GCC3.4.4 Microchip MPLAB C Compiler for PIC32 MCUs v1.10(b)-20091015

Compile Flags -DITERATIONS=1600 -DFOSC=80000000UL -DUSE_UART1 -O3

CoreMark/MHz : 1.745

LPC2138:

Processor Operating Frequency: 10MHz

Memory configuration: Code in FLASH (0 waitstate), MAM DISABLE

Compiler name and version : Keil ARMCC4.0.0.728

Compile Flags --feedback "Measure.fed" -c --cpu ARM7TDMI -O3 -Otime -I "C:\Keil\\ARM\INC" -I "C:\Keil\\ARM\INC\Philips" -DITERATIONS="200" -o "*.o" --omf_browse "*.crf" --depend "*.d"

CoreMark/MHz : 1.706

Da questo si evince che per il PIC abbiamo un punteggio appena più alto del 2,2% circa

Corredo di esempi

Ogni compilatore, come per la maggior parte dei microcontrollori, dispone di esempi pratici e un manuale per permettere all’utente di imparare ad usarlo. Sia per il PIC che per L’ARM, abbiamo trovato soddisfacente il corredo di esempi. Molti affermano di trovare più documentazione per i micro di Microchip.. il vero problema è saper cercare !

Programmazione e Debug

PIC32MX hanno:

- 2 interfacce di debug e programmazione: interfaccia 2-Wire con un accesso non intrusivo e un real-Time data exchange con Applicazione e un interfaccia 4-WIRE MIPS Standard Enhanced JTAG.

- Una non intrusiva p.3

Dispone anche del supporto DMA per il debug.

Ha la possibilità di bloccare individualmente il funzionamento delle varie periferiche hardware durante le fasi di debug. questo permette nel caso in cui il micro venisse fermato da un breakpoint hardware, di decidere per ogni periferica se deve continuare a funzionare o se invece si deve bloccare immediatamente e riprendere successivamente. Tra i vari debugger a disposizione troviamo ICD2, ICD3, PICkit3, RealIce.. che permettono vari livelli di debug..

LPC2xxx permettono vari sistemi di programmazione, seriale, JTAG… E’ possibile effettuare debug tramite la porta JTAG.

Hardware a bordo

Entrambi i micro presentano simili risorse hardware, da notare che il LPC2138 dispone anche di un convertitore D/A.

Ram e Rom

Entrambi dispongono di 512K di flash e 32K di ram.

PIC32MX Le istruzioni MIPS16 possono permettono di occupare il 40% in meno di flash.

ARM7TDMI-S Le istruzioni Thumb sono in grado di occupare il 35% in meno di flash e di avere una performance del 160% rispetto ad un equivalente ARM connesso ad una memoria a 16 bit.

Stack

PIC32MX non implementano uno stack hardware. Questi processori si affidano al software per avere questa funzionalità.

LPC2138 come descritto in precedenza, usa il registro R13 come stack pointer.

Costi

I processori ARM, a parità di performance, costano di più degli altri, in questo caso, usando Farnel come metro di misura per l’acquisto di una decina di pezzi, troviamo il PIC32MX440F512H a 6,53€ mentre il LPC2138 a 12,04€. Quando si guardano i costi però bisogna tenere presente le caratteristiche del micro e ancora di più, non dimenticare i documenti in cui si dichiarano i problemi riscontrati sul micro in commercio, perché se il micro in questione ha gran parte del hardware affetto da problemi del die, sceglierlo solo per il basso costo non ha senso.

Quindi, cosa sceliere?

Opinione:

Dipende.. a livello di costi per i prototipi o piccoli numeri, sicuramente Microchip sta al primo posto grazie ai suoi sample gratuiti per chi si registra con email di dominio.. Questo però è uno specchietto per le allodole, li porta ad una veloce diffusione.. ma sul mercato scegliere PIC anziche ARM è un grave errore; lo steso progetto sviluppato con un micro ARM è vendibile ad un prezzo maggiore anche di 2 o 3 volte grazie all’immagine di stabilità e sicurezza che il nome ARM si è fatto.

Ringraziamenti

Ringraziamo Emc Elettronica per l’opportunità dataci.

Note e fonti

Per svolgere questa relazione approfondita abbiamo dedicato 60 ore, trovate nell’arco di 3 mesi tra un progetto e l’altro all’interno della nostra azienda.

Approfondimenti per PIC32MX:

Documenti pdf: pic32mx3xx/4xx, DS61113, DS61119

Link http://www.microchip.com/en_US/family/pic32/index.html

Link: http://www.mips.com/products/cores/32-64-bit-cores/mips32-m4k/

Approfondimenti per ARM:

Documenti pdf: LPC2131_32_34_36_38, ARM Architecture Reference Manual

Link http://www.arm.com/products/processors/classic/arm7/index.php

Link http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0234b/index.html

Link http://infocenter.arm.com/

http://blog.flyingpic24.com/2008/10/26/pic32-harvard-or-von-neumann/

Benchmark

CoreMark: http://www.coremark.org

Dhrystone wikipedia

Wheatstone wikipedia

ALTRI LINK per ARM: http://www.oscene.net/it/come-funziona/come-funziona-un-processore-arm

http://pessina.mib.infn.it/Corsi_del_III_anno/I%20microcontrollori%20Parte%20B%20%285%29.pdf

http://pessina.mib.infn.it/Corsi_del_III_anno/I%20microcontrollori%20Parte%20A%20%282%29.pdf

http://simplemachines.it/doc/arm_inst.pdf

http://www.diee.unica.it/eolab2/ASE-0506/Lucidi_ASE_F.pdf

questo sicuramente non significa che i loro core siano sempre i migliori. Hanno investito molto in marketing dei loro core, quindi e’ normale che abbiano creato uno standard. A questo punto mi chiedo: se tutti i microcontrollori a 32-bit hanno come CORE un ARM Cortex-MX, cosa li differenzierà. La guerra dei cloni cominciata e’! (Yoda)