In articoli passati avevamo affrontato tematiche su progetti modulari delle stazioni base, descrivendo i componenti chiave di una architettura ideale di un sistema bandabase di nuova generazione. In questo nuovo articolo ci portiamo su un livello successivo, prendendo in esame un’architettura ideale per schede bandabase di nuova generazione. Si esamineranno gli aspetti cruciali a livello di scheda associati a questi sistemi, suggerendo ai progettisti come massimizzare le prestazioni attraverso la parallelizzazione delle funzioni in uno switch bandabase centralizzato

Introduzione

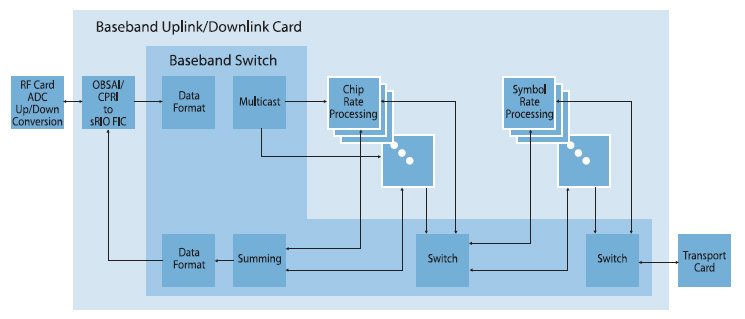

L'architettura quasi ideale è dove uno switch seriale RapidIO® è supportato da un sommatore, da un sincronizzatore nonché da un’interfaccia CPRI/OBSAI. Il progettista ha la facoltà di semplificare la ripartizione funzionale, come illustrato in figura 1.

Nonostante sia possibile implementare lo switch bandabase utilizzando più dispositivi, è anche possibile incrementare l’efficienza e utilizzare meno componenti discreti ricorrendo all’architettura di figura 2.

Lo switch bandabase è il cuore della scheda. Esso fornisce la connettività verso il DSP e i processori bandabase, per esempio al processore chip-rate utilizzato nei sistemi basati su tecnologia CDMA. Se i DSP sono in grado di eseguire le operazioni ad alta velocità – per esempio a livello chip-rate - è possibile eliminare dalla scheda ASIC e FPGA. Lo switch bandabase vede anche la scheda RF attraverso una interfaccia CPRI/OBSAI o una interfaccia proprietaria (basata su standard LVDS). Questa interfaccia trasporta per la maggior parte traffico ad alta velocità. Le frequenza possono arrivare fino a 3072 Mbps (come definito dallo standard CPRI), e il sistema può aprire su questi link più istanze, normalmente una per ciascuna scheda RF. Lato uplink, i campioni provenienti dalla scheda RF sono distribuiti ai blocchi di elaborazione. Per i sistemi CDMA-based questi campioni sono trasmessi ai CRP. Durante questo trasferimento i campioni possono anche essere formattati in base alle esigenze del processore o dell’algoritmo. Parleremo più diffusamente di questa formattazione nella seconda parte dell’articolo. Una volta completata l’elaborazione chip-rate i canali utente che emergono dai vari CRP passano all’elaborazione symbolrate (che riguarda per esempio operazioni di FEC, di elaborazione voce e così via). Queste funzioni richiedono una banda molto più bassa in quanto i campioni sono convertiti in bit e la funzione di de-spreading in CDMA è completa. A questo punto l’informazione “simbolica” deve essere commutata dai CRP ai DSP. Quando il DSP ha ultimato l’elaborazione simbolica, i pacchetti devono essere passati al modulo di trasporto per essere trasferiti ai livelli superiori della rete. Anche queste due operazioni di switching vengono svolte dallo switch bandabase.

Perchè questa architettura ?

Questa architettura è altamente flessibile e scalabile. Utilizzando lo switch bandabase come fulcro del sistema, il progettista può eliminare i componenti discreti che pregiudicano la scalabilità e la flessibilità, per esempio il sommatore o il sincronizzatore. Tradizionalmente una scheda bandabase utilizza interfacce semplici per scambiare dati e campioni con la memoria esterna. Questa strategia impone dei grossi vincoli al software in quanto si tratta di un approccio di interfacciamento di tipo “pull”, che per sua natura fa scendere i livelli di utilizzazione della banda al di sotto del 25%. Per garantire che la scheda bandabase sia dimensionabile su velocità superiori, i progettisti devono ricorrere a una nuova interfaccia di natura seriale. Questa interfaccia deve essere anche più intelligente della classica interfaccia di memoria. Essa deve poter inizializzare più blocchi di elaborazione e deve poter comunicare con essi. Tale funzione richiede un protocollo capace di identificare automaticamente i dispositivi sulla scheda bandabase, di inizializzarli e di gestire in modo flessibile le comunicazioni con essi. Il tutto deve supportare comunicazioni di tipo acknowledged e unacknowledged, push e pull. Al fine di facilitare l’accesso al software, il protocollo deve inoltre consentire l’uso di interrupt in banda. Sviluppare un algoritmo per la bandabase è di per sé un compito arduo. Questo protocollo evita pertanto al programmatore software il compito di dover reinventare uno standard di comunicazione. Un esempio eccellente di protocollo di questo tipo è il seriale RapidIO. Esso è supportato dai nuovi DSP oltre che dai blocchi di elaborazione per schede bandabase attualmente in commercio.

Latenza

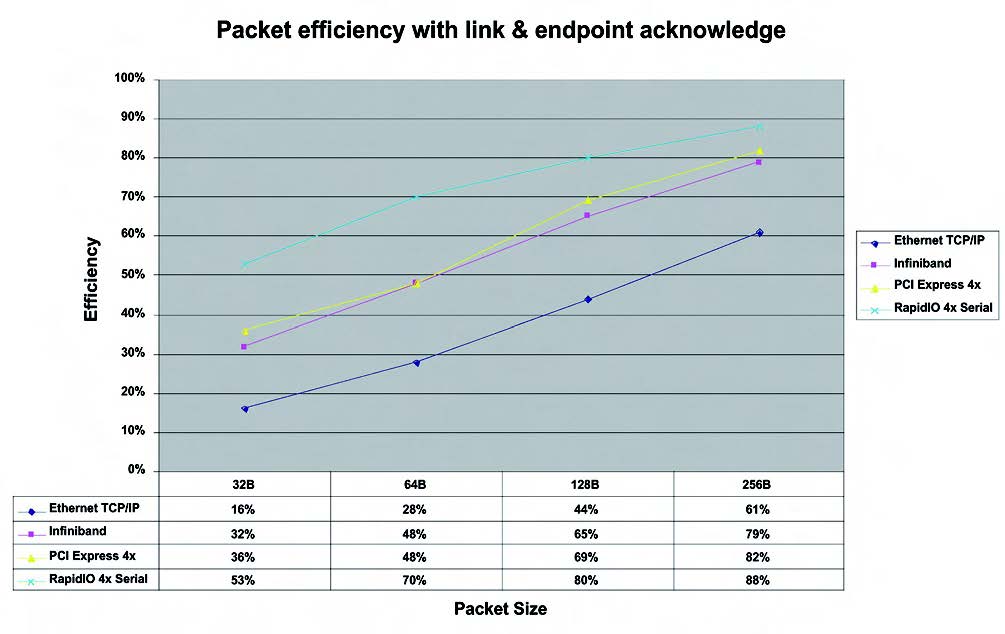

Uno dei primi problemi da affrontare quando si utilizza un protocollo complesso è la latenza. Nel CDMA iI controllo closed-loop della potenza è molto importante: qualsiasi incremento della latenza nella scheda bandabase influenza le prestazioni dell’intero sistema. A causa degli overhead, l’uso di un protocollo quale serial RapidIO® può portare teoricamente a un incremento della latenza. Viceversa, la latenza si riduce utilizzando interfacce seriali veloci di tipo unidirezionale (invece che bidirezionale). Cosa più importante, una semplice interfaccia di memoria comporterebbe più ritardi a livello software in quanto il processore dovrebbe gestire sia le funzioni base sia gli algoritmi di comunicazione. I protocolli come serial RapidIO® permettono di risolvere tutti questi problemi, raggiungendo così bassi livelli di latenza. La figura 3 illustra come serial RapidIO® possa operare con overhead estremamente bassi rispetto ad altri protocolli a pacchetto.

La latenza del ciclo completo è di circa 100 microsecondi, o 384 chip. Allocando solo 10 chip per l’elaborazione del protocollo serial RapidIO® sulla scheda bandabase, è possibile soddisfare le specifiche di latenza del loop di controllo della potenza.

Sincronizzazione

Ai fini della robustezza del sistema è molto importante anche la sincronizzazione della Base Transceiver Station (BTS). Nei moderni sistemi, le schede RF e bandabase sono sincronizzate attraverso un clock di sistema estremamente pulito (che normalmente gira a 30.72 MHz per i sistemi WCDMA). L’interfaccia tra schede bandabase e modulo TM è invece sincronizzata con un’altra sorgente di clock, per esempio quella utilizzata per il link T1 o Ethernet. Il passaggio da un dominio di clock all’altro avviene nei blocchi di elaborazione, per esempio i DSP, presenti sulla scheda bandabase. I DSP normalmente accumulano i campioni o i simboli prima di avviare l’algoritmo di elaborazione. Questo rende il tutto praticamente asincrono con il resto del sistema. Lo stesso concetto può essere utilizzato quanto si inserisce il protocollo serial RapidIO® nella scheda bandabase. La sincronizzazione può essere spinta sull’interfaccia della scheda RF. Interfacce quali CPRI gestiscono la sincronizzazione in modo ottimale ma non è necessario mantenere lo stesso livello di sincronizzazione sulla scheda bandabase. Un approccio più efficiente prevede la sostituzione delle interfacce sincrone di memoria con un protocollo flessibile, scalabile e modulare quale serial RapidIO. Il DSP si comporta intrinsecamente allo stesso modo ma i problemi di sincronizzazione vengono automaticamente ricondotti ai confini della scheda bandabase.

Funzioni di commutazione bandabase

Uno switch bandabase non è semplicemente uno switch di protocollo. Ad appannaggio esclusivo della scheda bandabase sono da segnalare numerose funzioni aggiuntive. È consigliabile che queste funzioni risiedano in un blocco centralizzato per le seguenti ragioni:

Molte funzioni sono ripetitive: funzioni quali la formattazione dei pacchetti sono normalmente ripetute in tutti i blocchi di elaborazione della scheda bandabase. Poiché i campioni CDMA sono inviati a tutti i blocchi di elaborazione, è più efficiente formattare i pacchetti in un blocco centrale prima dell’invio.

Formati di I/O differenti: i componenti commerciali non sempre utilizzano lo stesso formato di input/output: l’ADC sulla scheda RF può produrre un campione di dimensioni differenti rispetto a quelle richieste da un ASIC di elaborazione chip-rate o da un algoritmo DSP. Queste discrepanze possono essere risolte al meglio se tutti i pacchetti si concentrano in uno switch bandabase centralizzato.

Latenza ridotta: i blocchi di elaborazione quali i DSP spendono talvolta molte risorse per formattare i pacchetti, il che riduce la quantità di risorse di elaborazione disponibili per le funzioni di “alto volume” quali l’elaborazione in ricezione.

Esigenza di funzioni centralizzate: alcune funzioni – quali la somma nel downlink CDMA – devono essere eseguite dopo che ciascun processore chip-rate ha generato in uscita i campioni associati ai relativi utenti. Le informazioni d’utente vengono aggiunte prima dell’invio alla scheda RF.

Dal punto di vista del sistema, svolgere le seguenti funzioni nello switch bandabase è più efficiente.

Nell’ambito della manipolazione dei campioni: include le funzioni legate all’estensione di segno, alla cancellazione dei campioni, alla variazione del tipo di endian ecc. Nell’ambito della manipolazione dei pacchetti: include le funzioni legate al muxing, al demuxing e all’interleaving dei pacchetti da schede RF differenti. Ciò consente al sistema di presentare ai blocchi di elaborazione i campioni da schede RF differenti non come pacchetti multipli bensì come un unico pacchetto. Gli algoritmi normalmente iniziano a lavorare quando è disponibile un certo numero di campioni da ciascuna antenna. Quando il sistema riceve i campioni da più schede RF in un’unica locazione di memoria, l’algoritmo può iniziare a lavorare prima, riducendo i tempi di latenza. Somma: ai fini del multiplexing, i campioni di più DSP e CRP devono essere sommati nel CDMA. Questa attività può essere svolta al meglio nello switch bandabase in quanto tutti i dispositivi inviano i pacchetti all’interfaccia della scheda RF attraverso questo dispositivo. Operazioni DMA: in alcuni casi le porzioni dei pacchetti devono essere inviate a varie locazioni della memoria interna o esterna del processore.

Benefici potenziali

Qual è la percentuale di cicli di elaborazione che si possono risparmiare eseguendo queste operazioni in un dispositivo centralizzato - quali uno switch bandabase - rispetto a un processore quale un DSP? L’esempio seguente prende in considerazione un’applicazione WCDMA. Assumendo che tutte le funzioni chip rate e symbol rate possano essere implementate su uno o più DSP a 1GHz, ciascuna funzione dell’asse x è un esempio di funzione WCDMA. I dati comprendono anche le funzioni precedenti. Per esempio, il 27.5% relativo alla variazione del tipo di endian del campione comprende l’estensione del segno del campione stesso. I calcoli assumono un ritardo di 1-2 cicli per l’esecuzione di ciascuna funzione su campione singolo, 12 canali d’antenna e sistemi WCDMA a 3.84 Mcps con un rapporto di sovracampionamento di 2x. Da uno a due cicli di latenza per ciascuna funzione per campione è un caso ottimistico; ciò è basato sull’assunto che ciascun campione è accessibile nella memoria di primo livello o in un registro. In uno scenario realistico, i campioni saranno in una memoria di secondo livello che porta la latenza di accesso fino a 9-10 cicli (in un DSP a 1GHz) per il primo campione e a due cicli per ciascun campione successivo. Nello scenario più sfavorevole, una cattiva gestione della memoria a livello software può portare la lettura a 8-9 cicli per campione. In casi estremi, il DSP potrebbe diventare inutilizzabile per altri compiti in quanto tutte le risorse sono dedicate alla formattazione dei dati.

Conclusioni

Per i progettisti impegnati nello sviluppo di schede bandabase di nuova generazione, un’architettura basata su interfaccia seriale RapidIO® potrebbe offrire numerosi benefici in accordo ai requisiti di progettazione. Essa semplifica e minimizza i costi associati all’integrazione di nuove capacità o all’aggiornamento del sistema. in aggiunta, semplifica in modo sostanziale lo sviluppo software, senza incrementare le latenze.