Più di quarant'anni dopo l'impetuosa diffusione dei transistor MOSFET planari e nel mezzo della discussione sul superamento della legge di Moore, assistiamo all'introduzione di un nuovo transistor: FINFET. Facciamo conoscenza con il nuovo componente.

Introduzione

Gordon Moore nel suo famoso articolo ”Cramming more components onto integrated circuits (Electronics, 1965)” predisse l’impetuoso sviluppo della miniaturizzazione nei circuiti integrati (una originale interpretazione della Legge di Moore è presentata in "Oltre la Legge di Moore" EOS 15 agosto 2009). Effettivamente negli ultimi decenni la lunghezza del transistor usato nei circuiti integrati si è dimezzata in media ogni tre anni. Il transistor MOSFET è stato il protagonista di questo trend che non ha confronti in alcuna altra attività umana. Molto si è discusso a proposito di quale sarebbe stato il limite alla miniaturizzazione dei componenti nei circuiti integrati. Nel corso degli anni si è ritenuto che i limiti nella risoluzione litografica fossero la barriera ultima, il costo delle fabbriche necessarie a sostenere tecnologie nanometriche, limiti intrinseci nell’utilizzo di silicio come substrato, infine limiti fisici legati alle dimensioni degli strati di isolamento ormai prossime alla dimensione delle molecole, oppure limiti legati alle imperfezioni dei reticoli cristallini industrialmente producibili in serie (vedi in EOS l'interessante articolo "Mosfet e scaling: la miniaturizzazione è il futuro?" 31 marzo 2015). In realtà, ben prima di tutto questo, la tecnologia dei circuiti integrati, in particolare digitali, rischiava di trovare un limite nel degrado delle caratteristiche elettriche del suo componente fondamentale, il transistor MOSFET. Dopo un breve richiamo sul suo funzionamento, vedremo come riducendo drasticamente le dimensioni fisiche del componente, il transistor MOSFET non si comporti più come transistor, perdendo sostanzialmente la capacità di controllo della conducibilità del canale. Vedremo poi come il nuovo transistor, pur basandosi sugli stessi principi fisici, sia in grado di funzionare anche a dimensioni estremamente piccole (esistono prototipi a cinque nanometri), gettando le basi per proseguire ancora per parecchi nodi tecnologici, l’impetuosa diffusione delle tecnologie CMOS cui siamo abituati. Il nuovo transistor deve il suo nome all’aspetto assunto aggiungendo due strutture ai lati del canale di conduzione dei primi prototipi, che lo fanno vagamente assomigliare ad un pesce (fin in inglese significa pinna). Introdurremo anche strutture più tradizionali ma in grado di competere in ampi settori di applicazione, rendendo il panorama più vivace. Anche se non potremo mai avere tra le mani un FINFET ed i suoi concorrenti, non ne è infatti prevista la produzione come componenti discreti, è interessante conoscere da vicino questi nuovi componenti dei circuiti integrati che aggiungono una dimensione alle strutture elementari, creando una nuova elettronica 3D.

Il transistor MOSFET "tradizionale" nei circuiti integrati ed i suoi limiti

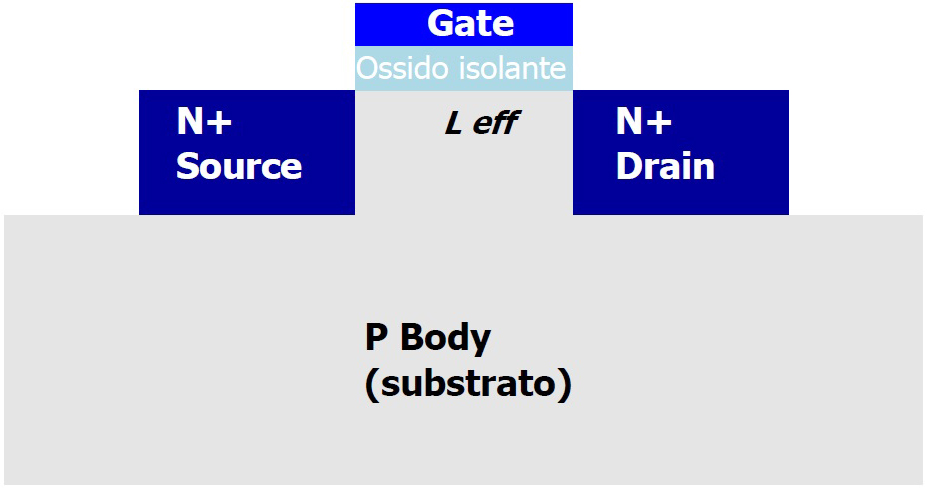

Per comodità del lettore, richiamiamo brevemente il funzionamento del transistor CMOS planare. Come vediamo in Figura 1, esso è composto da due aree fortemente drogate (di polarità P oppure N) separate da substrato poco drogato. Le aree drogate costituiscono source e drain. Un terzo terminale (gate) è direttamente affacciato sul canale che separa source e drain, realizzando il terminale di controllo. Il gate è isolato da uno strato di ossido. Considerato come esempio un transistor MOSFET di polarità N, con una tensione nulla, o al di sotto della soglia di conduzione, applicata alla gate, il transistor è in interdizione e non vi è passaggio di corrente tra drain e source. Applicando una tensione superiore alla soglia, il campo elettrico stabilito tra substrato e gate dà origine ad un accumulo di cariche elettriche e si stabilisce un vero e proprio canale di conduzione tra i terminali drain e source. La tensione applicata alla gate è quindi efficace nel controllare la conducibilità del transistor. A causa della presenza dello strato di ossido isolante non vi è circolazione di corrente tra gate e substrato. In altre parole, i transistor MOSFET presentano impedenze di ingresso (gate) estremamente elevate, caratteristica utile in molte situazioni progettuali.

Le strutture fisiche coinvolte sono naturalmente tridimensionali ma sono sviluppate soprattutto in lunghezza e larghezza, più che in altezza e la loro fabbricazione coinvolge fondamentalmente processi fisici e chimici sul piano x-y in molteplici passaggi consecutivi. In questo senso si parla di processi e dispositivi planari (vedi "Introduction to Semiconductor Technology" AN900 STMicroelectronics). Riducendo le dimensioni del transistor a lunghezze di canale inferiori a circa 100 nanometri, il comportamento del MOSFET inizia a presentarsi ben diverso da quello ideale descritto. Fenomeni di gate leakage, ossia circolazione di corrente continua tra gate e substrato in presenza di polarizzazione, iniziano a manifestarsi con pregiudizio delle prestazioni in termini di consumo e generazione di calore.

Figura 1. Il transistor MOS planare

Evoluzioni del transistor planare

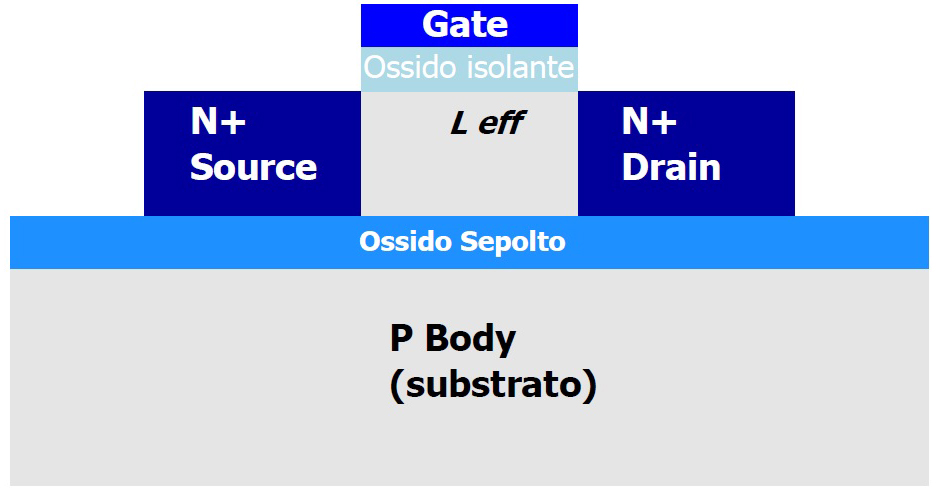

Accorgimenti di fabbricazione permisero di tenere il fenomeno sotto controllo, vedi Figura 2. L’aggiunta di uno strato di isolante sotto il canale, ed altri accorgimenti di processo, eliminano percorsi conduttivi e ripristinano una elevata impedenza, eliminando o riducendo grandemente il leakage.

Figura 2. Transistor MOS SOI (Silicon On Insulator)

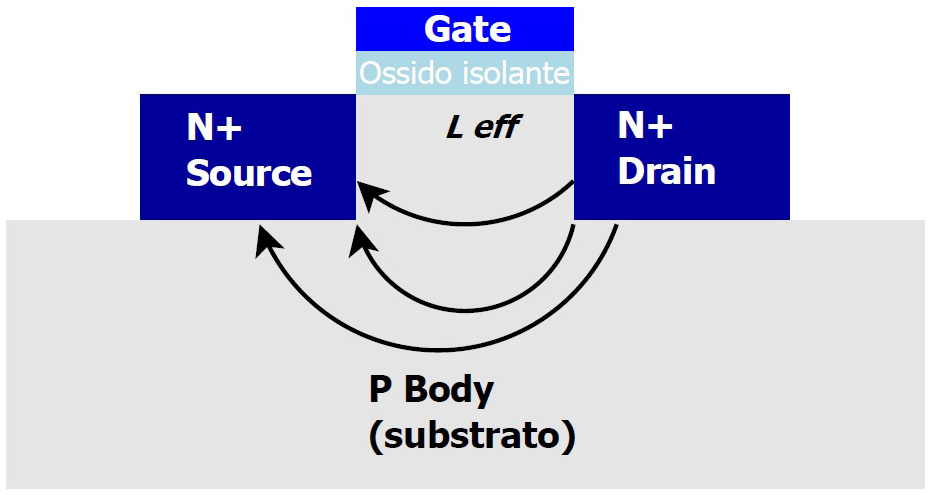

Con lunghezze di canale inferiori a poche decine di nanometri, drain e source sono talmente vicini che la differenza di potenziale tra i due terminali è da sola in grado di creare conduzione nel canale, vanificando l’effetto della gate. In altre parole, la struttura risultante conduce corrente anche in assenza di tensione sulla gate, di fatto non comportandosi più come un transistor. Osservando la distribuzione dei campi elettrici visibile nella Figura 3, possiamo notare la creazione di corrente di leakage anche lontano dalla struttura gate/substrato, cosa che compromette il funzionamento del dispositivo.

Figura 3. Quando Leff diventa piccola (<20nm), il campo elettrico tra Drain e Source causa correnti di leakage importanti, indipendentemente dalla tensione di Gate.

FIN-FET

Dopo alcune proposte iniziali dual-gate e multiple gate, la struttura visibile [...]

ATTENZIONE: quello che hai appena letto è solo un estratto, l'Articolo Tecnico completo è composto da ben 2124 parole ed è riservato agli ABBONATI. Con l'Abbonamento avrai anche accesso a tutti gli altri Articoli Tecnici che potrai leggere in formato PDF per un anno. ABBONATI ORA, è semplice e sicuro.

Ormai siamo arrivati quasi ai limiti dell’atomo, se si pensa che il raggio di un atomo di silicio è di circa 110 pm, siamo soltanto un ordine di grandezza sopra, che tecnologicamente secondo me sarà anche molto difficile da limare.

Mi capita spesso di utilizzare Mosfet di potenza in applicazioni su carichi induttivi come possono essere ventilatori a spazzole di potenza e di dover modulare la velocita’ non piu’ con i vecchi sistemi ad inserimento di resistori che sprecano piu’ energia con la dissipazione per effetto Joule.

Tale regolazione viene richiesta in modalita’ PWM ed anche qui ci si deve comunque scontrare con problematiche per la scelta del Mosfet adatto in base alla frequenza e potenza richiesta.

Entrano in gioco le capacita’ parassite di Gate e Drain e l’utilizzo di appositi driver con cui tarare le correnti di carica ( Gate ) nella modalita’ opportuna , per non incidere troppo sulla dissipazione per effetto joule a causa delle capacita’ parassite.

Risulta chiaro che si debbano cercare sempre migliori tecnologie costruttive per questi componenti ormai di uso insostituibile in molte applicazioni.

Già da tempo è noto che la legge di Moore presto o tardi perderà di validità in quanto arriveremo ad un limite tecnologico che impedirà un’ulteriore forte miniaturizzazione della tecnologia su silicio. Tuttavia, un orizzonte di 5nm è stupefacente, pensando alle dimensioni del primo transistore, e metterà a disposizione una enorme potenza di calcolo. Potenza che continuerà ad aumentare anche grazie ai nuovi approcci System on Package nella realizzazione di IC. Magari prima o poi la miniaturizzazione potrà anche fermarsi, ma certamente non si fermerà la forte spinta al progresso tecnologico.

Pensate che siamo arrivati ai limiti di miniaturizzazione? Sì questo è vero per quanto riguarda i transistori contenuti negli IC, ma in futuro si potrebbero inventare nuove tecnologie che rivoluzionerebbero quelle attuali. Ne abbiamo avuto esempio in passato: dai sistemi meccanici dei primi calcolatori si è passati ai sistemi elettromeccanici, poi è venuta l’era delle valvole termoioniche, poi i transistori, infine i circuiti integrati, che si sono evoluti fino ai nostri giorni, arrivando quasi ai limiti con la suddetta tecnologia FINFET. Chissà che tecnologia potrebbe venire fuori fra qualche anno per soppiantare gli attuali circuiti integrati, allargando la possibilità di ulteriore miniaturizzazione e riduzione di consumi dei dispositivi!

Ormai molto prossimi a divenire realtà sono i sistemi biologici; si pensi che un modello di “computer biologico” in grado di processare grandi quantità di dati in tempi analoghi a quelli di super computer di grandi dimensioni è già tra noi.

Aggungo che Google poco tempo fa ha annunciato di avere raggiunto una situazione stabile e funzionante per la sua tecnologia quantistica applicata ai computer. Non so se i FINFET, benché componenti molto interessanti, siano coinvolti in questa tecnologia ma dovranno essere sicuramente aggiornati i libri di scuola di elettronica.

Consideriamo anche che per il progetto di una CPU sono impiegate parecchie persone! Ho notato però che il ciclo vita di un microchip si sta accorciando, e che ogni pochi giorni assistaimo al lancio sul mercato di nuovi modelli, con qualche funzionalità in più…. Credo che oggi più che mai sia difficile scegliere il componente migliore per il nostro progetto. Ed è così che una rivista come EOS e una Community attiva possono creare un filo conduttore tra i produttori di componenti, l’offerta di mercato e gli elettronici che semplicemente desiderano rimanere aggiornati e qualche volta vorrebbero realizzare qualche sogno nel cassetto.