Non si intende parlare qui dell’animale sacro agli Antichi Egizi, naturalmente, ma di uno strumento per verificare la Signal Integrity dei nostri progetti senza costruire prototipi. IBIS è infatti l’acronimo di I/O Buffer Information Specification.

Nella vastissima gamma di Note Tecniche, Application Notes, Whitepapers rilasciate ogni mese da tutti i produttori di componenti elettronici, strumentazione e sistemi, si nascondono a volte piccole “gemme”, documenti preziosi per la loro chiarezza o per il contenuto particolarmente interessante. Certo, lo scopo è sempre contribuire, più o meno direttamente, alla vendita dei propri componenti, ma non di rado il valore formativo ed informativo di alcuni di questi componenti va ben oltre lo scopo immediato. Molte Application Notes di Hewlett Packard su vari aspetti della strumentazione elettronica, i suoi principi ed il suo uso, hanno affiancato da decenni libri di testo nelle Università di tutto il mondo. Note Applicative di Motorola circa le Linee di Trasmissione sono ancora oggi un testo di riferimento.

Certi documenti hanno contribuito validamente alla diffusione di nuove conoscenze e creato “cultura tecnica”. E’ opinione dell’autore che l’Application Note indicata in Rif. 1 appartenga a questa categoria. Cogliamo, quindi, l’occasione per discuterne il contenuto. Abbiamo visto su Firmware n.62 (vedi Rif.2) come sia sempre più frequente l’esigenza di preoccuparsi della qualità dei segnali distribuiti nelle nostre applicazioni e preoccuparsene prima della costruzione di prototipi. L’aumento di frequenze e tempi di transizione impone l’uso di tecniche di gestione dei segnai tipiche del dominio high-speed, quali impedenze controllate, terminazioni, controllo crosstalk eccetera. Verificare via simulazione il comportamento delle porzioni critiche, diventa importante per ridurre rifacimenti di hardware con conseguenti perdite di tempo e denaro. Gli strumenti disponibili da molti anni, una qualche versione del simulatore elettrico SPICE, sono usabili per lo scopo ma con problemi sia per i fornitori che per gli utenti. SPICE modella i circuiti a transistor-level, come si dice in gergo, rivelando nei modelli usati molto di circuiti interni e parametri di processo che i produttori ritengono confidenziali. SPICE può dare risultati molto accurati ma a prezzo di tempi di simulazione molto lunghi, specialmente nelle simulazioni “transient”, di tipico interesse in Signal Integrity.

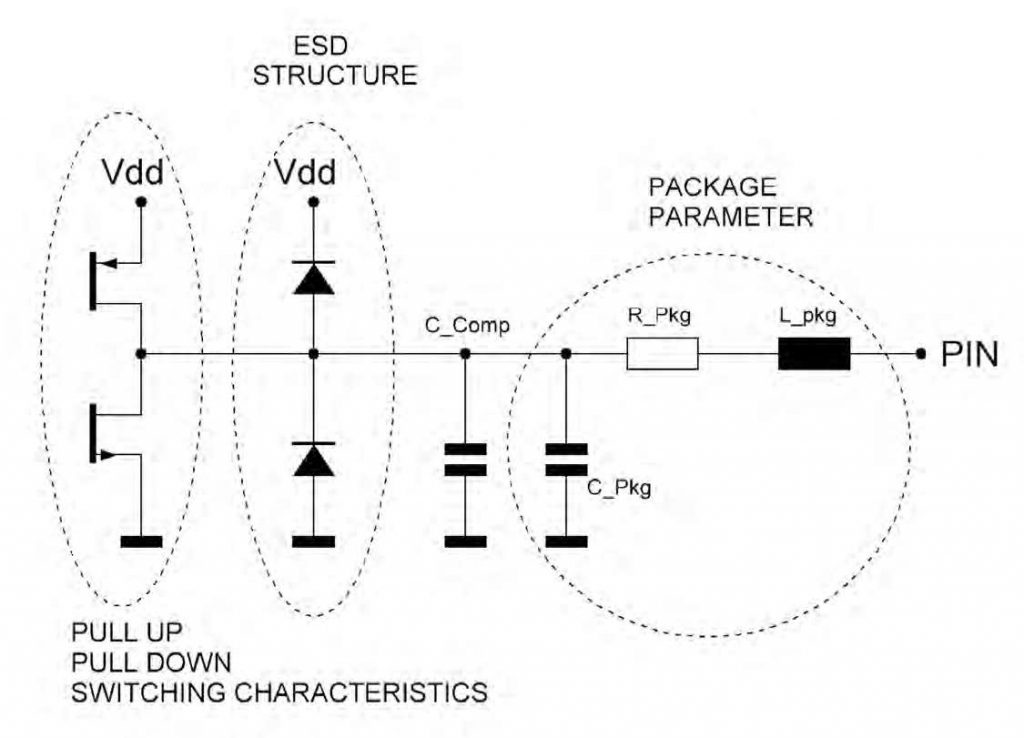

Figura 1: schema Equivalente di un Output.

Capita anche che i modelli resi disponibili non siano compatibili con la particolare versione di SPICE in uso. Questo insieme di ragioni portò Intel all’inizio degli anni ‘90 a proporre un’alternativa a SPICE, I/O Buffer Information Specification (IBIS) per permettere un’accurata simulazione del comportamento dei buffer di Input/Output (vedi figura 1), pur proteggendo la sicurezza delle proprie Intellectual Property, ovvero i dettagli di implementazione e produzione dei propri componenti. In realtà, sarebbe più appropriato parlare di una modelizzazione affiancata a quella propria di SPICE, senza la pretesa di sostituire quest’ultima nel 100% dei casi. Ogni simulazione è fondata su modelli che rendono conto del comportamento dei singoli enti coinvolti. IBIS rende disponibili modelli degli ingressi ed uscite di circuiti integrati logici (I/O buffers) come file di testo dal formato codificato in uno standard. Il nocciolo di tale file è costituito da tabelle con informazioni di corrente, tensione e temporizzazioni, gli stessi dati che ogni datasheet contiene in forma grafica. Renderli disponibili in forma numerica ne permette, evidentemente, un facile trattamento da parte dei software, da cui il soprannome di “executable datasheet” che ben rende l’idea. Il circuito interno diviene una scatola nera dalla quale non viene svelato alcun dettaglio, solo il comportamento ai morsetti esterni viene reso visibile. La velocità di simulazione viene notevolmente incrementata con una certa perdita di accuratezza, ritenuta modesta nella maggior parte delle applicazioni del modello. I modelli sono resi liberamente disponibili dai costruttori sui loro siti web. La specifica IBIS è gestita da un EIA/IBIS Open Forum, vedi rif. 3, che comprende vari produttori di circuiti integrati e vari fornitori di programmi CAD per la simulazione di circuiti stampati e sistemi. Procuriamoci un modello IBIS, per semplicità un sestuplo inverter CMOS (compatibile con LS-TTL) 74HCU04, vedi rif. 4. Vediamo alcune convenzioni sintattiche e non, definite per i modelli IBIS. Tutto quanto segue un carattere “|” (pipe) è considerato un commento ed ignorato in simulazione.

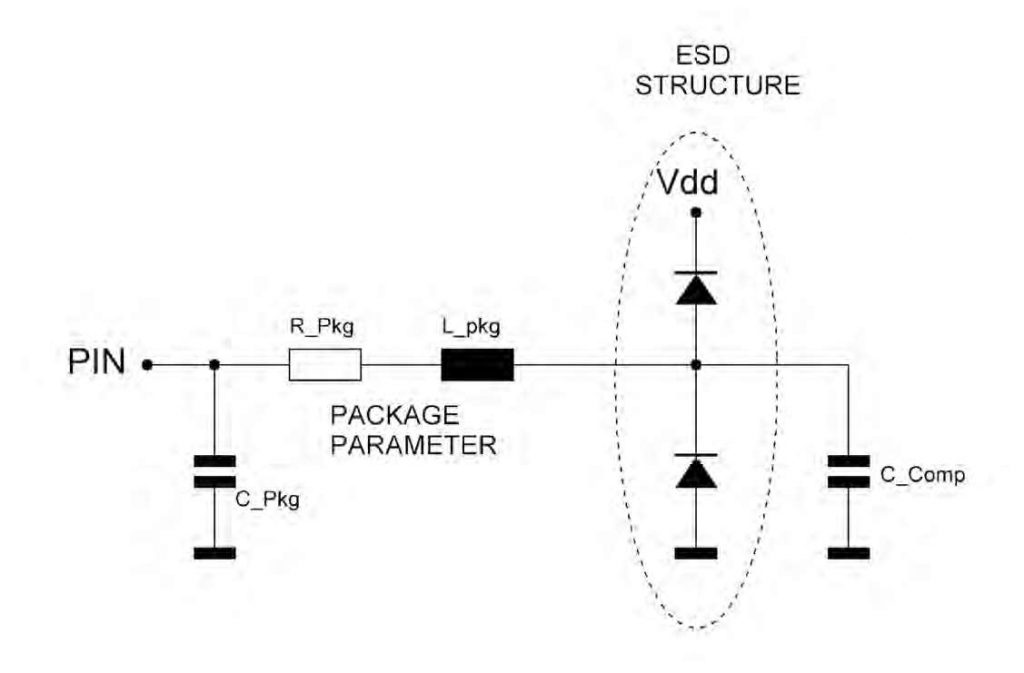

Figura 2: schema Equivalente di un Input.

Le keywords sono rese riconoscibili includendole tra parentesi quadre. Le correnti entranti nel dispositivo sono considerate positive. Le tabelle dati V/I devono avere abbastanza punti da rappresentare accuratamente le regioni non lineari delle curve rappresentate, senza bisogno di infittire il numero di punti nelle regioni lineari, appesantendo inutilmente il file. Troviamo innanzitutto un’intestazione che dichiara a quale dispositivo si riferisce il modello, chi lo ha generato e la versione IBIS standard cui soddisfa. Modelli più accurati e complessi potrebbero tenere conto anche delle inevitabili variazioni di processo, rendendo conto della dispersione dei parametrielettrici in produzione di serie. Troviamo, quindi, una tabella PACKAGE riassuntiva, che riporta i parametri elettrici tipici, minimi e massimi della resistenza, induttanza e capacità parassita dei fili di connessione e della struttura del package. Notare l’ordine, comune a tutte le tabelle IBIS, rende accessibile per primo il valore tipico, non il valore minimo. Segue poi una tabella analoga che dettaglia pin per pin i valori RLC, tipico, minimo e massimo. Il modello IBIS deve rappresentare il comportamento ai pin di connessione al circuito stampato (per questo si parla di modello comportamentale, “behavioral”), è quindi importante includere tutti i parametri parassiti. La keyword MODEL SELECTOR elenca differenti tipi di input o output disponibili nel componente. In dispositivi complessi questo può corrispondere a opzioni di slew rate e capacità di pilotaggio, selezionabili attraverso registri programmabili, come, ad esempio, in port I/O o bus memoria di microprocessori. Qui rappresentano, invece, le principali opzioni di alimentazione disponibili (2.5V, 3.3V, 5V) cui corrispondono, ovviamente, curve V/I e tempi di risposta differenti. Per analizzare correttamente il seguito, occorre tenere presenti gli schemi equivalenti di ingressi ed uscite che gli IBIS assumono come riferimento. Il chip presenta una capacità come unico parametro elettrico parassita. Questo è il parametro identificato, per ogni modello, da C_COMP (abbreviazione di Capacità Componente). Per ogni modello si indicano le soglie nominali ed il range di alimentazione. Per ciascuno degli oggetti/modalità di funzionamento dell’output, viene riportata nel file IBIS una tabella I/V che rende conto del valore assunto in corrispondenza ad ogni valore della variabile indipendente. Troviamo cosi per gli input (vedi figura 2) le caratteristiche elettriche dei diodi di protezione ESD (GND_CLAMP, POWER_CLAMP), mentre per gli output troviamo anche le caratteristiche elettriche in tree-state, pullup (stato logico ‘1’) pull down (stato logico ‘0’). Troviamo poi le tabelle che descrivono le transizioni 0->1 e 1->0 come tensione in funzione del tempo. Nei modelli IBIS si assume normalmente un carico di 50 ohm, ma, se opportuno, possono essere presenti fino a 100 tabelle con differenti valori di carico. Nel caso di buona linearità, sarà sufficiente riportare lo slew rate (keyword RAMP). Può anche esno, invece, le principali opzioni di alimentazione disponibili (2.5V, 3.3V, 5V) cui corrispondono, ovviamente, curve V/I e tempi di risposta differenti. Per analizzare correttamente il seguito, occorre tenere presenti gli schemi equivalenti di ingressi ed uscite che gli IBIS assumono come riferimento. Il chip presenta una capacità come unico parametro elettrico parassita. Questo è il parametro identificato, per ogni modello, da C_COMP (abbreviazione di Capacità Componente). Per ogni modello si indicano le soglie nominali ed il range di alimentazione. Per ciascuno degli oggetti/modalità di funzionamento dell’output, viene riportata nel file IBIS una tabella I/V che rende conto del valore assunto in corrispondenza ad ogni valore della variabile indipendente. Troviamo cosi per gli input le caratteristiche elettriche dei diodi di protezione ESD (GND_CLAMP, POWER_CLAMP), mentre per gli output troviamo anche le caratteristiche elettriche in tree-state, pullup (stato logico ‘1’) pull down (stato logico ‘0’). Troviamo poi le tabelle che descrivono le transizioni 0->1 e 1->0 come tensione in funzione del tempo. Nei modelli IBIS si assume normalmente un carico di 50 ohm, ma, se opportuno, possono essere presenti fino a 100 tabelle con differenti valori di carico. Nel caso di buona linearità, sarà sufficiente riportare lo slew rate (keyword RAMP). Può anche essere presente una tensione esterna a rappresentare, ad esempio, circuiti open collector. I modelli IBIS sono tipicamente generati attraverso simulazioni SPICE eseguite dal costruttore del circuito integrato nell’ambito di un ambiente di riferimento. L’ambiente viene correlato con misure di laboratorio ma non c’è necessità di confronto con misure ad ogni generazione di un nuovo modello. La validazione “di serie” è fatta innanzitutto facendo passare il singolo file in un analizzatore di sintassi (IBISCK5, disponibile nel sito in rif. 3). Viene poi eseguita una simulazione con il modello IBIS su carico standard e confrontata con una simulazione SPICE nelle stesse condizioni. Entrati in possesso di tutti i modelli IBIS degli input/output presenti nel percorso di segnale che intendiamo simulare, è opportuno un minimo di analisi, prima di importare tutto in un simulatore e procedere alla verifica di Signal Integrity che ci interessa. Far passare i modelli attraverso il syntax checker IBISCK5 ed analizzare gli eventuali errori è la prima operazione utile. E’ anche possibile scaricare il programma Visual IBIS Editor che integra un text editor, in grado di riconosce ed evidenziare le keyword, con visualizzatore grafico che legge le tabelle e ne traccia il diagramma XY. Eventuali anomalie quali non monotonicità delle transizioni 0->0 o 1->0 diverranno cosi evidenti. Simulazioni importanti per i moderni sistemi sono Simultaneous Switching Output (SSO, chiamata anche Simultaneous Switching Noise) e Power Integrity. La possibilità di simulare SSO con gli IBIS esiste almeno dalla revisione 4.0. La presenza di dati necessari è però facoltativa e va verificata modello per modello. Non c’è, inoltre, uniformità nel trattamento di questi dati da parte di programmi CAD di diversi fornitori, quindi una verifica circa l’uso dei dati nel proprio ambiente di simulazione è altrettanto necessaria. In modelli IBIS precedenti alla versione 5.0, gli I/O venivano supposti connessi ad alimentazioni ideali, in altre parole, non c’era rappresentazione del comportamento delle alimentazioni e relative correnti, in funzione dell’attività degli I/O. La versione 5.0 introduce, invece, la modellizzazione dei profili di corrente dei buffer durante le commutazioni, permettendo una accurata simulazione di rumore generato sulle alimentazioni (e quindi propagato al sistema), ed anche di eventuali eccessive cadute di tensione istantanee. E’ cosi possibile utilizzare i modelli IBIS per completare analisi di Power Integrity, in aggiunta a Signal Integrity (vedi rif. 5).