Un’introduzione ai microcontrollori low-power con interfaccia IR di Maxim.

Sempre più applicazioni, soprattutto nel settore embedded, richiedono l’adozione di microcontrollori a bassa dissipazione di potenza in grado di garantire comunque adeguata capacità di calcolo e connettività di vario tipo. MAXQ (figura 1) è la famiglia di microcontrollori proposta da Maxim per tale segmento di mercato. La CPU è di tipo RISC transport-triggered (vedi di seguito) con larghezza di parola a 16 bit e un insieme di sole 33 istruzioni, anch’esse a 16 bit (il che semplifica notevolmente la programmazione).

Caratteristiche generali

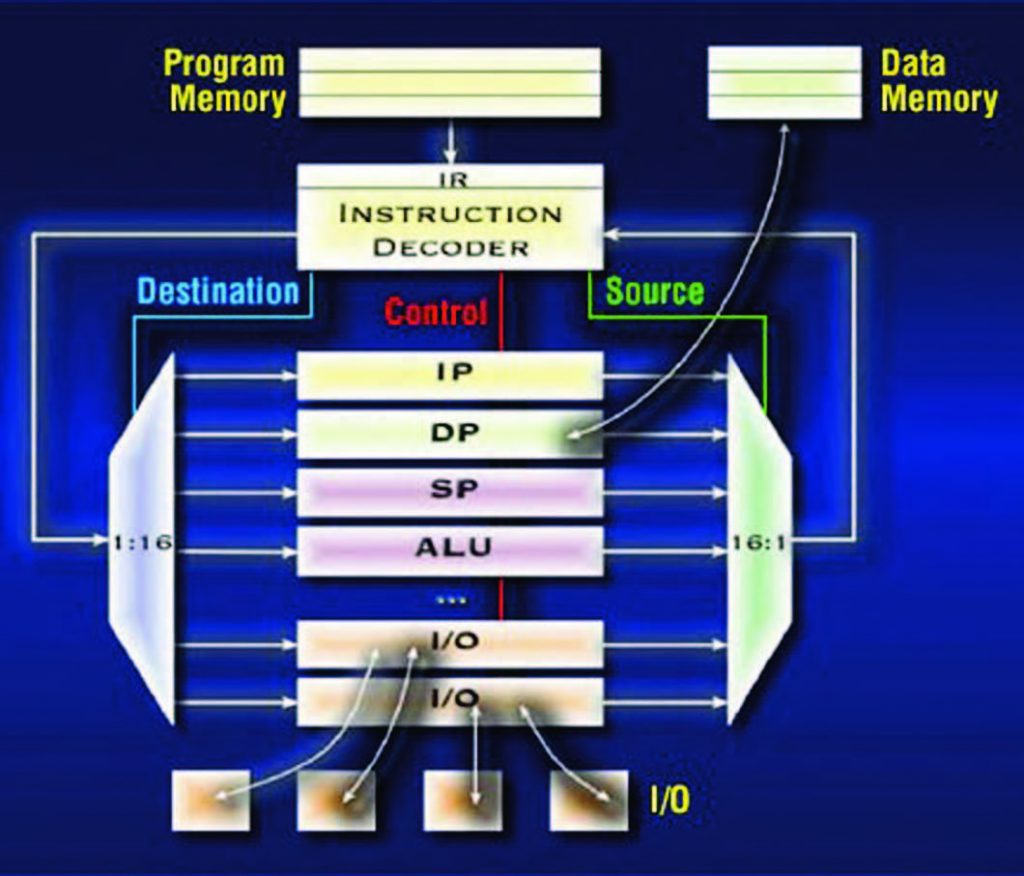

L’architettura (figura 2) è di tipo Harward con spazi d’indirizzamento separati per le memorie dati, programmi e registri. L’MMU assicura il partizionamento dello spazio di memoria tra le diverse applicazioni supportando così la protezione della proprietà intellettuale del codice da tentativi di reverse engineering; supporta la programmazione in-system e in-application della memoria Flash embedded. Sono integrati on-chip fino a 6 KByte di memoria RAM e 128 KByte di memoria Flash, partizionata in settori da 512 byte qualificati per fino a 20 mila cicli di scrittura. Le periferiche disponibili sono USART, SPI, I2C, timer a 16-bit con funzionalità di wake-up (mediante oscillatore integrato low-power), watchdog e RTC, controller PWM, IR timer con funzionalità di generazione della portante e modulazione, USB (solo su MAXQ622) e convertitore A/D con tipologia SAR e capacità di campionamento fino a 313 ksps (solo MAXQ8913 e MAXQ2010). L’interfaccia USART supporta comunicazione half-duplex in modalità sincrona e full-duplex in modalità asincrona, con generazione indipendente di baudrate e supporto per parità programmabile.

Figura 1: la famiglia MAXQ di micro con connettività IR.

La porta SPI opera in modalità master o slave con bit-rate sulla linea seriale fino a metà della frequenza del clock di sistema e con supporto per rilevamento delle collisioni in applicazioni multi-master. L’alimentazione dei dispositivi è compresa tra 1,7 e 3,6 V, erogabile mediante batteria a ioni di litio o direttamente da porta USB (mediante regolatore di tensione interno). La frequenza massima di clock, per i modelli MAXQ612/622 ad esempio, è di 12 MHz. L’assorbimento di corrente, per tali dispositivi, è di 4,8 mA alla massima frequenza di clock (o soli 520 µA ad 1 MHz) e si riduce ad 0,3 µA (tipico) in modalità stop a temperatura ambiente. I dispositivi sono disponibili in package TQFP/LQFP/TQFN con un massimo di 100 pin a un costo (per mille pezzi) che varia, a seconda del modello, tra 0,54 e 3,35 $.

Figura 2: l’architettura dei micro MAXQ.

L’insieme di istruzioni

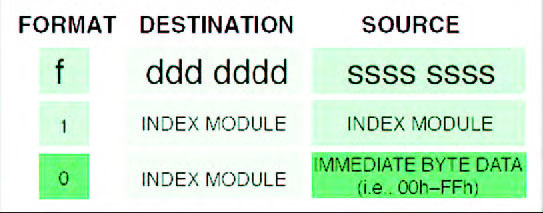

Caratteristica distintiva della CPU MAXQ20 dei micro MAXQ è il semplice formato delle istruzioni, mostrato schematicamente in figura 3. Tutte le istruzioni si riducono, ovvero, a operazioni di Move tra un operando sorgente e uno destinazione. Il campo destination dell’istruzione definisce appunto l’indirizzo dell’operando destinazione mentre la flag format caratterizza l’operando sorgente come di tipo immediato o registro. Nel primo caso il campo source dell’istruzione ne indica il valore a 8-bit mentre nel secondo ne definisce l’indirizzo. L’indirizzamento è tipicamente di tipo diretto, tranne che in casi particolari, come ad esempio per l’istruzione di copia del contenuto dell’accumulatore in una locazione di memoria dati indirizzata dal rispettivo puntatore. L’architettura della CPU, come detto, è di tipo transport-triggered nel senso che l’accesso in lettura o scrittura a un registro induce effetti collaterali (come la manipolazione del contenuto dell’operando) legati alle caratteristiche del registro stesso. Così, ad esempio, le diverse istruzioni di più alto livello eseguite dall’ALU sono virtualmente mappate come altrettanti registri di sistema, il che rende possibile descriverle, come detto, come operazioni di Move. L’insieme di istruzioni è ortogonale; tutte le operazioni logiche e aritmetiche, in altre parole, che utilizzano due registri possono accedere a un registro qualunque unitamente all’accumulatore mentre i dati possono essere trasferiti tra due registri in una singola istruzione. Lo spazio di registri comprende 16 moduli che consistono ognuno di un insieme di 32 registri e che sono associati a registri di sistema o periferiche del dispositivo (queste ultime, in particolare, corrispondenti ai 6 moduli agli indirizzi più bassi). Tra i registri di sistema vi sono, ad esempio, i 16 registri accumulatori accessibili dall’ALU, il puntatore all’accumulatore correntemente attivo, i registri di controllo e gestione delle interruzioni, due puntatori in memoria dati e uno in memoria programma, il puntatore all’istruzione corrente. All’interno di ogni modulo, i primi 8 registri sono accessibili in lettura/scrittura in un singolo ciclo di clock mentre i successivi 8 sono accessibili in lettura in un singolo ciclo e in scrittura in due cicli. L’accesso in scrittura/lettura ai restanti 16 registri richiede invece due cicli.

Figura 3: il formato delle istruzioni della

CPU MAXQ20.

L’ALU

La CPU MAXQ20 dei micro MAXQ dispone di ALU a 16-bit con 16 diversi accumulatori accessibili come operandi sorgente o destinazione. Un registro di sistema consente di selezionare l’accumulatore correntemente attivo, accessibile anche come registro di sistema stesso e operante come operando destinazione implicito per tutte le operazioni logiche e aritmetiche. Sono supportate operazioni unarie e binarie. Le istruzioni binarie operano sull’operando sorgente specificato dall’istruzione e sull’accumulatore correntemente selezionato. Sono implementate istruzione logiche (And, Or e Xor), aritmetiche (Add, Sub, Shift Left e Right, Rotate) oltre a istruzioni di salto condizionato e non, ritorno condizionale e loop. Le caratteristiche dell’ALU e la struttura dell’insieme di istruzioni rendono i micro MAXQ una soluzione a bassa dissipazione di potenza ma elevate prestazioni in termini di capacità di calcolo e dimensione del codice compilato. Benchmark comparativi pubblicati da Maxim mostrano un incremento delle prestazioni di un fattore compreso tra 3 e 5 rispetto ad altre architetture tradizionali come 8051, PIC18 o ATmega8.

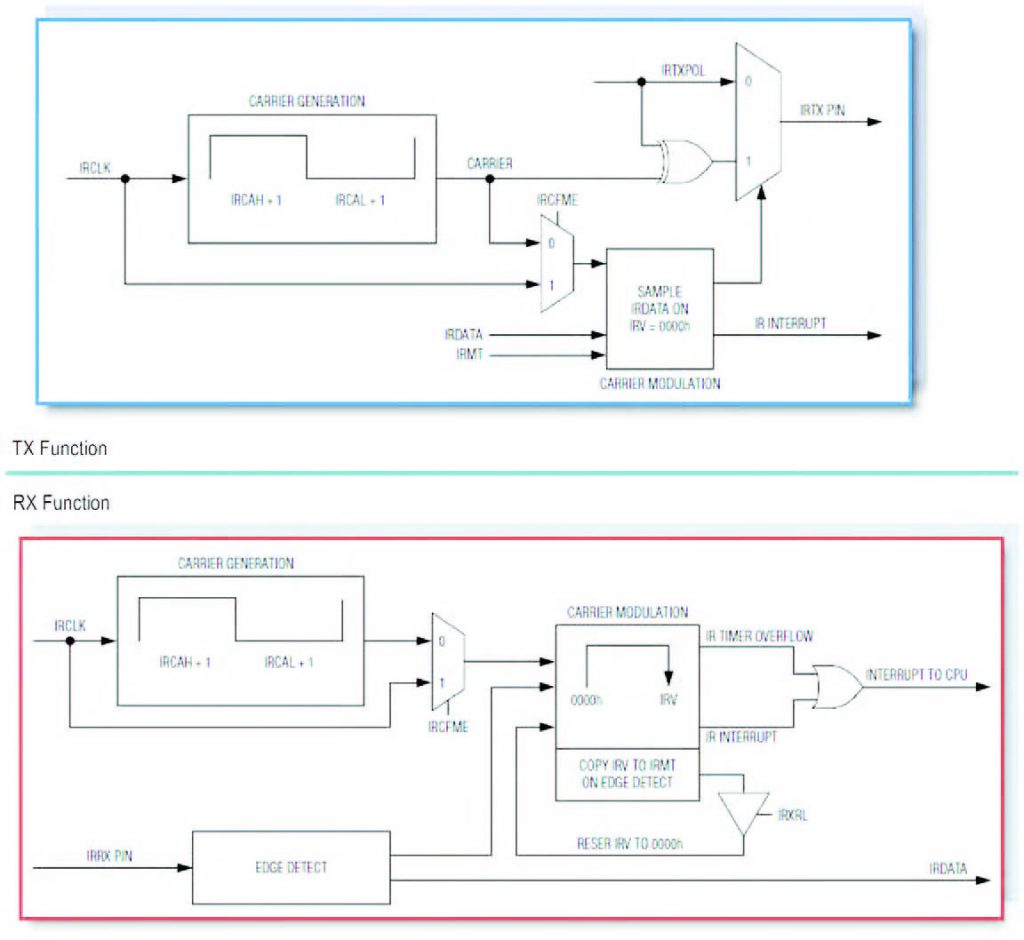

Periferica IR

I dispositivi MAXQ612/622 dispongono di una interessante periferica IR in grado di funzionare come trasmettitore o ricevitore in applicazioni di comunicazione a infrarossi a basso bit-rate. In trasmissione, ad esempio, la periferica (figura 4) dispone di generatore di portante con frequenza e duty cycle programmabili dall’utente mediante registri di periferica. La portante viene quindi modulata per un intervallo di tempo misurato mediante timer dedicato e anch’esso configurabile in termini di numero di periodi della portante stessa o di un segnale di clock esterno. Per ogni intervallo di modulazione, quindi, un bit di un ulteriore registro di controllo indica se durante l’intervallo stesso la periferica deve pilotare in uscita il livello idle o la portante generata. In ricezione, invece, la periferica implementa funzionalità di capture della linea di ingresso. Un circuito dedicato rileva, infatti, eventuali commutazioni su tale linea generando in corrispondenza di queste interruzioni al processore e memorizzando il corrispondente valore del timer in un registro di stato. Un registro di controllo consente di selezionare se il timer si incrementa in corrispondenza del fronte attivo di un segnale di clock di riferimento o per ogni ciclo della portante di riferimento rigenerata internamente. Per ridurre poi il carico della CPU, è implementata anche una speciale modalità denominata “carrier-burst-count mode”. Una volta determinata la frequenza della comunicazione, in tale modalità, il circuito può essere riprogrammato così da contare il numero di fronti attivi del segnale di ricezione e asserire l’interruzione alla CPU se non si verificano eventi per due cicli consecutivi della portante ricostruita.

Figura 4: schema di principio delle funzioni IR dei micro MAXQ.

Connessione USB sul MAXQ622

Oltre alle periferiche generiche della famiglia, il micro MAXQ622 include anche un’interfaccia USB 2.0. La porta integra il transceiver fisico, consentendo la connessione diretta al cavo per applicazioni di dimensioni ridotte. Supporta fino a 4 end-point di cui due (EP2 ed EP3) per trasferimenti bulk in ingresso, uno (EP1) per trasferimento bulk in uscita e uno (EP0) bidirezionale di controllo. Gli end-point EP1 ed EP2 implementano un double-buffer con 64 byte di memoria per consentire alla CPU di leggere o scrivere il pacchetto ricevuto o da spedire mentre un nuovo trasferimento è in corso. L’end-point EP3 ha invece un singolo buffer con capacità di memoria di 64 byte ed è tipicamente utilizzato per gestire interrupt pipe come, ad esempio, nella comunicazione con camere still image.

Interessante, però bisognerebbe spiegare con che cosa si programma, magari quanto costa un link alla famiglia, ai sistemi di sviluppo non sarebbe male, no?