La struttura generale del bus VME (Standard IEEE-1014-1987) e i fatti principali che hanno portato alla nascita di questo importante standard di comunicazione utilizzato in diverse applicazioni industriali, militari e commerciali.

Introduzione

Un BUS è una struttura di interconnessione tramite linee di comunicazione che permette lo scambio di informazioni tra varie unità dello stesso sistema: per esempio tra la CPU, la memoria centrale e le periferiche. Le linee del BUS sono condivise tra tutti i dispositivi. Possibili strutture di interconnessione sono: punto-punto, anello, stella. Un bus ha molti vantaggi: in particolare permette di mettere insieme parti costruite da case diverse (con conseguente discesa dei prezzi grazie al maggior volume di produzione). Per fare ciò, è necessario avere uno standard di bus. Esistono diversi tipi di standard:

- Standard “de facto”: è uno standard decretato tale dalla vasta diffusione di un bus sul mercato. Lo svantaggio di un tale tipo di standard è che non è completamente normalizzato. Esempio di questo standard è il UNIBUS (Digital).

- Standard “Promosso”: è il caso più frequente. Proviene dalla “promozione”, cioè dalla formalizzazione ufficiale di un bus esistente. Questa operazione viene fatta da un’apposita organizzazione internazionale, che sottopone il bus a prove (e, in alcuni casi, lo migliora aggiungendo potenzialità che alla casa costruttrice non interessavano). Esempi di questo standard sono: VME, EtherNet, MULTIBUS.

- Standard “da progetto”: i bus di questo tipo sono quelli tecnicamente più validi perché nascono senza dover garantire la continuità alle realizzazioni preesistenti. Sono però penalizzati dal fatto che non esiste una forza (grosso produttore o acquirente) che li “sponsorizzi” e faccia in modo che si impongano sul mercato. Questi sono generalmente poco diffusi. Esempi di questo standard sono: CAMAC, FutureBus.

Gli elementi caratteristici di un bus sono la velocità di trasmissione, lo spazio indirizzabile, l’ampiezza dei dati, l’immunità al rumore, la distanza da coprire, il supporto del multiprocessing, il costo. Esistono due tipi di trasmissione per un bus: trasmissione parallela e trasmissione seriale. La prima si utilizza quando il bus deve essere corto e veloce. La seconda quando il bus deve coprire distanze considerevoli ed essere economico (il driver di gestione è costoso ma è uno solo, mentre quello per i bus paralleli sono uno per filo).

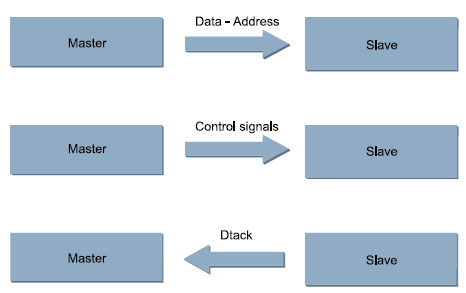

Per quanto riguarda la modalità del trasferimento, vi sono due possibilità. La prima prevede un dispositivo master e uno slave: il master manda sul bus un indirizzo che identifica lo slave con cui colloquiare. La seconda (usata, per esempio, nei bus per strumentazione) prevede tre dispositivi: un controller, un sender e un receiver. Il controller assegna i compiti di sender e receiver a due dispositivi e li lascia lavorare da soli mentre si occupa d’altro. Questa seconda alternativa rende evidentemente il sistema più flessibile. Il protocollo è la sequenza di operazioni che è necessario in un bus per stabilire la connessione, trasferire i dati e interrompere la connessione. Ne esistono due tipi: sincrono e asincrono. I bus sincroni sono quelli in cui si ha un segnale di riferimento temporale (il clock) e tutto avviene in corrispondenza dei fronti di salita (o di discesa) di questo segnale. I bus asincroni sono quelli in cui la cadenza degli eventi è fornita, di volta in volta, dai sottosistemi che trasferiscono i dati. Il vantaggio del bus asincrono è che si può adattare allo slave che stiamo interrogando, però è più complicato da gestire e più delicato per quanto riguarda la sensibilità al rumore. Spesso si troverà dei bus asincroni collegati ad una CPU che campiona con il proprio CK i segnali asincroni. Quindi, l’asincronicità rimane solo per la comunicazione. Tutto ciò perché una CPU asincrona è molto difficile da realizzare e gestire.

UN PO’ DI STORIA DEL BUS VME

Il VME (Versa Module Europa) è l’erede del lavoro fatto dai progettisti della Motorola, a partire dal 1978, per dotare le CPU della serie 68k di un bus. Questo lavoro produsse le prime specifiche di un bus denominato Versabus, successivamente accettato come standard IEEE 970. La Motorola aveva bisogno di promuovere la produzione del suo microprocessore single chip sperando di entrare nel mercato dei “mini-computer” dominato dalla DEC. Dagli anni 80 la Motorola cominciò a produrre sia moduli CPU che moduli slave per il Versabus. Il successo dei sistemi basati sul Versabus fu molto condizionato, specialmente in Europa dall’inadeguatezza degli strumenti software. Negli stessi anni un organismo internazionale, l’International Electrotecnhical Commission (IEC) aveva proposto uno standard meccanico modulare per il formato delle schede elettroniche detto comunemente Eurocard.

Approfittando dell’incoraggiamento della comunità europea che dava in quel tempo per le iniziative di standardizzazione in campo elettronico, la Motorola aderì con alcuni progetti ad un gruppo di lavoro per la definizione di un sistema di elaborazione distribuita. A questo gruppo parteciparono altre società importanti tra cui la Philips. Il gruppo di lavoro propose un sistema (il VME), ispirato al Versabus, ma alloggiato in una meccanica Eurocard. La presenza di progettisti non strettamente legate alla Motorola produsse delle specifiche sufficientemente generali da poter essere interpretate efficacemente anche con CPU di altre marche. La veridicità di queste affermazioni è oggi avvalorata dalla presenza sul mercato di molte schede in standard VME non basate su CPU Motorola. Sono adoperate CPU della Intel, AMD e altre ancora. Sull’onda del successo dello standard, nacque, sotto gli auspici della IEEE una associazione dei costruttori di moduli VME che si chiamò VMEbus International Trade Association (VITA). Questa organizzazione stampa due volte l’anno un’edizione aggiornata del catalogo di tutte le schede in standard VME e negli altri standard collegati (VXI e Futuresbus+) prodotte nel mondo. VITA, fondata nel 1984, è l’organizzazione commerciale responsabile del VMEbus standard ed altri campioni relativi. Il campione originale del bus VME era un bus a 16 bit, destinato per entrare nei connettori attuali Eurocard DIN. La versione successiva a 32 bit è stata in uso per molti anni (IEEE-1014-1987). Estensioni successive del bus VME è stata quella a 64 bit (VME64). Il contributo dello sviluppo del bus VME lo si deve a molte persone, tra cui:

- Jonh and Craig Mackenna: furono i promotori della specifica del VMEbus.

- Wayne Fischer: il primo presidente a guidare lo standard IEEE 1014.

- Mika Pauker, Arlan Harris: sviluppo del software di gestione del VMEbus in C.

LA STRUTTURA DEL BUS VME

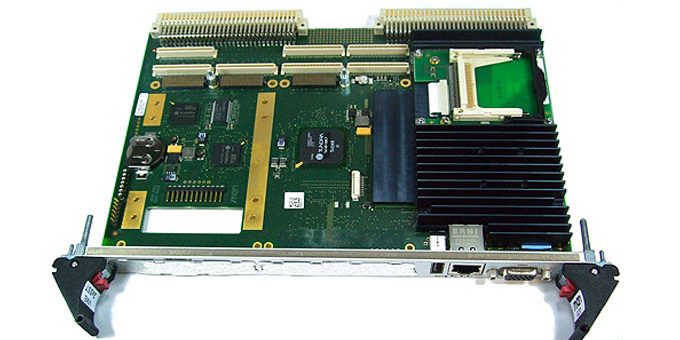

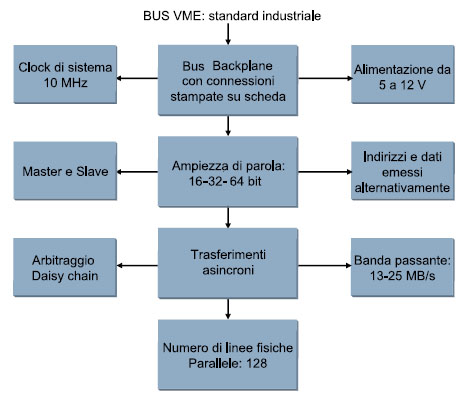

Il VME (Versa Module Europe) è un bus di lavoro introdotto negli anni 80 dalla Motorola e dalla Philips. Il bus VME (definito dalla standard IEEE1014) è dotato di una notevole banda passante e lavora secondo lo standard Eurocard in logica TTL. Eurocard è una disposizione standard europea per PCBs, che può essere inserito insieme ad un subrack standardizzato. L’architettura meccanica di Eurocard è stata definita originalmente sotto IEC-60297-3. Oggi, i campioni più ampiamente riconosciuti per questa struttura meccanica sono IEEE 1101.1, IEEE 1101.10 (anche conosciuto comunemente come “puntino dieci”) ed IEEE 1101.11. IEEE 1101.10 riguarda le caratteristiche supplementari di EMI e meccaniche richieste per VITA 1.1-1997 (R2002) che è il campione di estensioni VME64 così come PICMG 2.0 (R3.0) che è la specifica di CompactPCI. I sistemi del connettore che sono comunemente usati con le architetture di Eurocard includono il connettore originale DIN 41612 che inoltre è standardizzato come IEC 60603.2. Il VME è un bus multiprocessore che permette l’uso di CPU a 8, 16, 32 bit; utilizzato nell’ambito della ricerca, in applicazioni industriali, militari, commerciali e in sistemi di controllo del traffico, di commutazione e acquisizione dati.

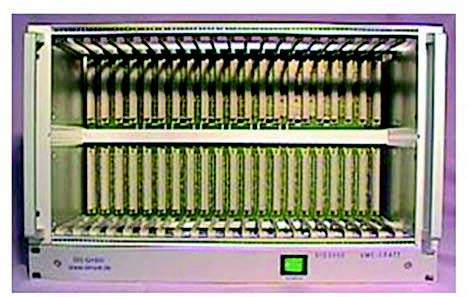

L’ambiente VME si basa su di un Crate, di opportune dimensioni (figura 1), contenente 21 slot, nei quali si possono inserire moduli delle dimensioni di 2.0x21.6 cm. Il primo slot è utilizzato per uno specifico modulo dotato di CPU con funzioni di crate manager (modulo di controllo).

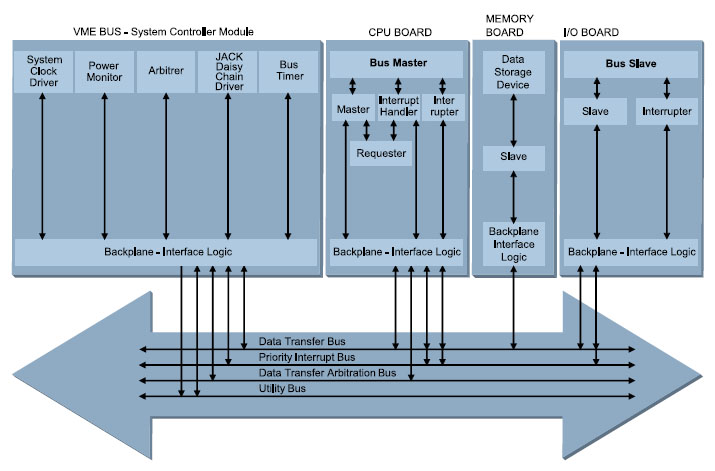

L’accesso alle schede installate al bus da parte del l’utente, è garantito dal modulo crate manager al quale vengono connesse le principali periferiche (monitor, tastiera, mouse, ecc…). Il bus VME si compone di 4 sottobus:

- Data Transfer Bus: utilizzato per le operazioni di scrittura e lettura dati.

- Arbitration Bus: controlla le richieste dei vari dispositivi per mezzo della CPU. Fornisce il permesso ad ogni dispositivo di utilizzare il bus ed informa i dispositivi quando il bus è occupato. Le richieste sono basate su priorità (4 livelli di arbitraggio).

- Priorità Interrupt Bus: è utilizzato per le operazioni di interruzione di processi (7 livelli di interrupt).

- Utilità Bus: è utilizzato per operazioni di reset.

Il bus VME (figura 2) lavora per mezzo di librerie che risiedono nel modulo principale dove c’è la CPU.

Queste librerie sono un insieme di comandi che vengono usati nella gestione delle varie operazioni (p.e. lettura, scrittura…) su vari registri di moduli elettronici che lavorano su bus VME. Le modalità di accesso sono uguali per tutti i moduli e consistono nell’interfacciare e “mappare” opportunamente il registro da leggere e/o scrivere mediante l’uso di opportune librerie VME. In uno dei prossimi articoli vedremo un software che permette la gestione di queste librerie VME. L’accesso al bus VME può avvenire in due modalità:

- Supervisore

- Non Privilegiato

La differenza tra questi due accessi risiede nella configurazione di alcuni parametri interni al bus VME da parte della CPU. In generale si preferisce accedere in modalità Non Privilegiato. La struttura del Bus VME è master-slave: il master gestisce il ciclo e lo slave che ha decodificato il proprio indirizzo risponde alla transazione. Il bus permette trasferimenti dati asincroni: lo slave termina il ciclo con un acknowledge quando ha finito di processare la transazione. I trasferimenti sul bus sono asincroni e le linee dati e quelle indirizzi sono separate.

I campi di indirizzamento possono utilizzare 16-bit (short), 24-bit (standard) e 32-bit (extendend), con possibilità di passare dall’uno all’altro dinamicamente, così come si possono gestire dinamicamente, byte (8-bit), word (16-bit) e long word (32-bit). I cicli trasferimenti dati possono essere: cycle, l’indirizzo viene inviato assieme ad ogni trasferimento dati; block transfer, un solo indirizzo è inviato per un trasferimento dati multiplo.

Nel bus VME tutti i trasferimenti sono di tipo DMA. Il DMA (Direct Memory Access) permette ad alcuni sottosistemi hardware di un computer di accedere alla memoria di sistema in lettura e/o scrittura indipendentemente dalla CPU; usato da molti sistemi hardware come controller di unità a disco, schede grafiche e schede audio. Il DMA è un componente essenziale di tutti i computer moderni, in quanto permette a periferiche che lavorano a velocità diverse di comunicare senza assoggettare la CPU a un enorme carico di interrupt. Essenzialmente, in un trasferimento DMA un blocco di memoria viene copiato da una periferica a un’altra. La CPU si limita a dare avvio al trasferimento, mentre il trasferimento vero e proprio è svolto dal controller DMA. Un caso tipico è lo spostamento di un blocco di memoria da unità di memoria esterna alla memoria principale. Se questa operazione, come avviene grazie al DMA, non blocca il processore, esso può continuare a svolgere altre operazioni. La struttura del bus VME può essere rappresentata mediante la figura 3.

Un circuito di controllo “Controller” permette la gestione degli accessi al bus VME. Un Master e uno Slave che regolano il flusso di dati e le operazioni di scrittura e lettura (figura 4).

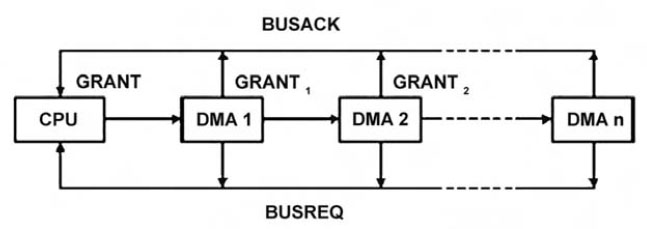

L’arbitraggio è una funzione di gestione del possesso del bus. Spesso, infatti, accade che CPU, memoria e altri dispositivi ne richiedano simultaneamente l’utilizzo. In questi casi, esistono varie tecniche per decidere chi ha diritto al trasferimento. Il bus VME utilizza l’arbiraggio Daisy Chain a controllo centralizzato (figura 5).

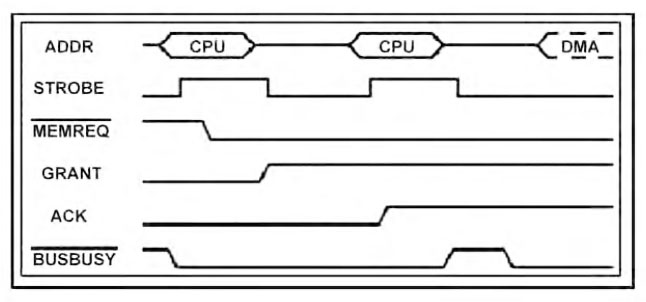

La struttura presenta un segnale di acknowledge che comunica alla CPU che il dispositivo è pronto per usare il bus. Quando un dispositivo ha necessità di utilizzare il bus segnala con un segnale che denominiamo BUSREQ alla CPU la volontà di compiere l’accesso, la CPU risponde con un altro segnale denominato GRANT ma non interrompe la sua attività. Sarà il segnale di BUSACK a comunicarle che la transazione sta per avere inizio. Solo allora sospenderà l’esecuzione del processo in corso, sospenderà l’invio di GRANT e rilascerà il bus. In questo modo il bus non è mai inutilizzato, poiché la CPU continua ad usarlo anche mentre invia GRANT e attende BUSACK. Inoltre, il sistema non si blocca come nel caso precedente, perché anche se ci sono più richieste e nessuno capisce a chi è diretto il GRANT, BUSACK non viene generato e dopo un po’ la CPU toglie anche GRANT. L’arbitraggio, invece, si può sovrapporre alla transazione perché una volta arrivato BUSACK il GRANT è “resettato” ed è possibile ricevere una nuova richiesta. Il diagramma temporale di figura 6 illustra la successione degli eventi. Gli errori principali che si verificano nell’ambito del bus VME possono essere: Errori di trasferimento: destano poca preoccupazione perché hanno bassa probabilità di veri ficarsi e, anche quando si verificano, vi si pone facilmente rimedio ripetendo la trasmissione.

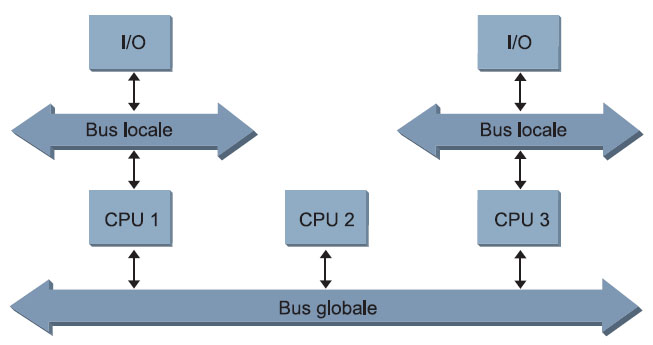

Per rilevarli è sufficiente aggiungere un bit di parità all’informazione trasmessa. Errori dello Slave: si verificano quando si indirizza uno slave che, per qualche motivo, non riesce a svolgere l’operazione richiesta. Errore di indirizzamento: si verificano quando la memoria indirizzata è inesistente o rotta; poiché non c’è risposta la CPU si blocca. Nell’ambito della gestione delle interruzioni per sistemi multiprocessore è difficile per un interrupt sapere a quale CPU andare. Possiamo decidere che ciascuna CPU risponda solo ad alcuni livelli di interrupt (figura 7).

Il problema è che se si danneggia una CPU, gli interrupt ad essa inviati vanno persi irrimediabilmente. A questo punto è più semplice vincolare alla CPU anche i dispositivi che generano quegli interrupt. In un sistema multiprocessore c’è anche la necessità di inviare segnali di interrupt da una CPU all’altra. Il dispositivo, quindi, chiede il controllo del bus e dopo averlo ottenuto, pone il vettore di interrupt sul bus dati. L’Interrupt Vector (vettore di interrupt) è un metodo più efficiente. La periferica inoltra la richiesta di interruzione (INT) e riceve un segnale (INTACK) che comunica che il bus è libero, successivamente essa invia sul bus dati un vettore che contiene informazioni relative all’interrupt richiesta a cui la CPU risponde con un segnale ACK che si propaga in daisy chain. L’interrupt vector contiene il motivo della richiesta dell’interrupt o, meglio ancora, il puntatore a una tabella contenente la descrizione dell’interrupt e l’indirizzo della sua routine di gestione.

Personalmente ho utilizzato un sistema VME con ADC e I/O register per gestire un sistema di acquisizione dati per esperimenti gravitazionali.