L’elemento centrale di qualsiasi dispositivo FPGA è il suo “blocco logico”, cioè un circuito logico in grado di essere configurato dall’utente per potere implementare semplici funzioni logiche o aritmetiche arbitrarie. L’interconnessione di più blocchi logici permette poi di realizzare circuiti di complessità maggiore.

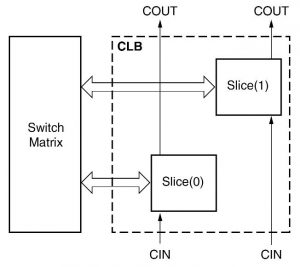

Negli anni sono state proposte ed utilizzate diverse strutture per la realizzazione dei blocchi logici, caratterizzati da differenti gradi di complessità (“granulosità”) e diverse soluzioni circuitali (semplici porte logiche, multiplexer, Look-Up Table, etc). Gli FPGA basati su tecnologia SRAM, come quelli prodotti da Altera o Xilinx, hanno adottato fin dall’inizio una soluzione simile, che si è mantenuta quasi del tutto immutata nel tempo: i blocchi logici sono realizzati principalmente tramite Look-up Table (LUT) per la generazione delle funzioni combinatorie e latch/flip-flop in uscita come elementi di memoria. Inizialmente le LUT furono dotate di 4 ingressi ed una uscita. Questa scelta era dettata da considerazioni sull’area occupata dai singoli blocchi logici e dalle caratteristiche delle funzioni che si sarebbero implementate tramite le LUT. In ciascun blocco logico mediamente erano presenti due o quattro LUT, ed altrettanti flip-flop. Questa configurazione è stata sostanzialmente mantenuta nel tempo, con l’eccezione di alcuni piccoli miglioramenti. Più recentemente, la crescita di complessità delle applicazioni implementate su FPGA ed il forte scaling tecnologico possibile (processi da 90 e 65nm), hanno indotto Xilinx a ritoccare le caratteristiche dei blocchi logici configurabili (CLB) presenti sui propri dispositivi, pur mantenendone la struttura generale. I nuovi CLB presenti sulle FPGA Virtex-5 risultano infatti notevolmente più complessi e flessibili di quelli presenti sui dispositivi delle generazioni precedenti, ed aggiungono diverse utili funzionalità. Il CLB delle Virtex-5 (Figura 1) è ancora costituito da due “slice”, cioè due unità funzionali che possono essere utilizzate assieme per svolgere una funzione più complessa, o indipendentemente per implementare due funzioni più semplici. Ciascun CLB è connesso ad una matrice di commutazione (Switch Matrix) che ne permette l’instradamento dei segnali, e ai CLB adiacenti (verticalmente) attraverso le linee dedicate ai riporti veloci, utilizzati per realizzare operazioni aritmetiche più efficienti. Le maggiori novità sono contenute all’interno delle slices, come verrà descritto meglio di seguito.

Figura 1. Struttura e connessioni dei CLB

LE SLICE

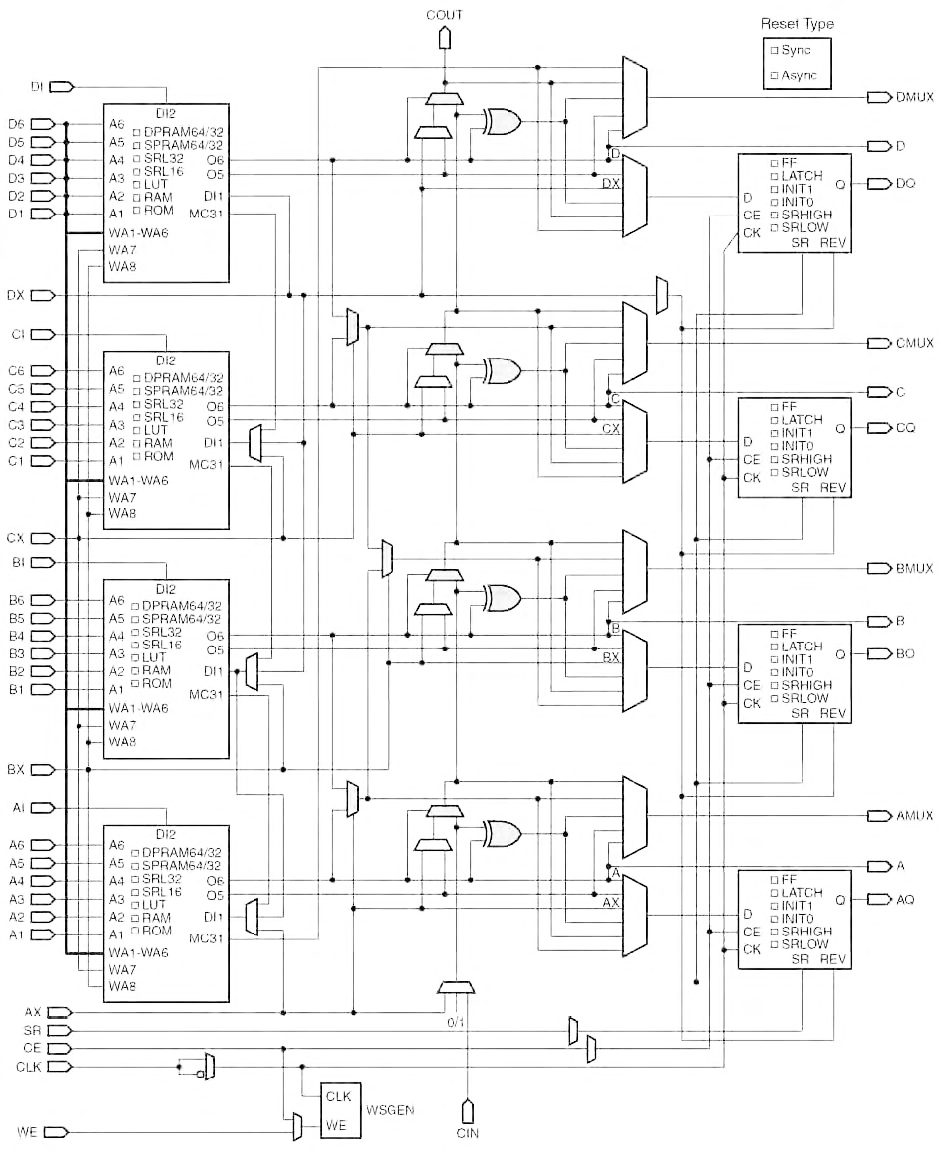

Le slice sono i blocchi logici elementi dell’FPGA: esse contengono le LUT ed i flip-flop, più alcuni circuiti dedicati all’implementazione di funzioni aritmetiche. Nei dispositivi precedenti ciascuna slice conteneva essenzialmente due LUT a 4 ingressi ed una uscita, due flip-flop e la logica per il calcolo e la propagazione veloce dei riporti (fast carry chain). Con l’introduzione delle Virtex-5 la struttura delle slice è stata notevolmente modificata e arricchita in complessità e versatilità (Figura 2).

Figura 2. Struttura delle slice presenti nelle Virtex-5

La caratteristica che risalta di più, e che rappresenta una significativa discontinuità con il passato è l’impiego in ciascuna slice di ben quattro LUT dotate ciascuna di 6 ingressi e due uscite, quattro flip-flop configurabili, una catena per riporti estesa alle 4 uscite, e dei multiplexer relativamente larghi (adatti a gestire il numero e l’ampiezza dei segnali presenti nelle slice). Come nei dispositivi più recenti, le slice presenti sul dispositivo sono di due tipi (opportunamente alternati sulla matrice): le “slicel” e le “slicem”. Nelle prime le LUT svolgono soltanto la funzione di generatori di funzioni logiche (quindi di “ROM”). Le seconde invece dispongono al posto delle semplici LUT di elementi molto più complessi, che possono funzionare oltre che come generatori di funzioni logiche, anche come memorie RAM distribuite a singola o doppia porta, profonde 32 o 64 bit, e registri a scorrimento da 16 o 32 bit. In un CLB quindi sono presenti complessivamente 8 LUT, 8 FF, che possono implementare fino a 256 bit di RAM distribuita e registri a scorrimento larghi fino a 128 bit. Questa grossa granulosità permette di implementare funzioni sensibilmente più complesse su ogni singolo CLB, ossia permette di impiegare un numero inferiore di CLB, contenendo così i ritardi di comunicazione.

Funzioni logiche

Le Look-up Table presenti nelle slice, come già detto sono dotate di 6 ingressi e di due uscite. Esse possono essere utilizzate in due modalità diverse: o come generatori di funzioni logiche a 6 ingressi e ad una uscita, o come generatori di due funzioni diverse di 5 ingressi. In quest’ultimo caso l’unico vincolo è che gli ingressi devono essere comuni alle due funzioni. Le LUT possono anche essere utilizzate congiuntamente per ottenere funzioni logiche di 7 o 8 ingressi. Per fare questo sono utilizzati tre multiplexer posti a valle delle LUT. Due di questi sono utilizzati per raggruppare le LUT a coppie, in modo da ottenere due funzioni indipendenti di 7 ingressi. Il terzo multiplexer può essere utilizzato per combinare le due uscite e generare una funzione complessiva di 8 ingressi. Per un numero di ingressi maggiore è necessario utilizzare più slice o più CLB. Le uscite delle LUT possono essere portate direttamente alle uscite della slice, agli elementi di memoria, o alla logica per il calcolo e la propagazione dei riporti, come visibile dalla Figura 2.

Elementi di memoria

Alle uscite di ciascuna slice sono presenti degli elementi di memorizzazione configurabili. Questi 4 elementi (uno per ciascuna LUT) possono essere configurati indipendentemente per funzionare come flip-flop o come latch. Nel primo caso si ottiene un comportamento da flip-flop di tipo D, funzionante sul fronte del segnale di clock, che è comune a tutti gli elementi. È possibile invertire il segnale di clock in modo da rendere gli elementi sensibili ai fronti di salita o di discesa. È possibile infine utilizzare un segnale di Clock Enable (CE) per i flip-flop, e decidere la modalità di reset e preset sincrona o asincrona da impiegare. Nella modalità di funzionamento da latch, gli elementi funzionano in maniera simile ad un latch RS, possono quindi memorizzare i dati in base dal livello assunto dai segnali di controllo (e non ai fronti, come nel caso dei flip-flop). Rispetto ad un latch RS classico la configurazione in cui gli ingressi di controllo sono entrambi alti è tollerata e porta ad un azzeramento del dispositivo. Anche nel caso di funzionamento da latch è possibile impiegare il segnale di Clock e di Clock Enable, che servono in pratica da abilitazione alla memorizzazione. In particolare si può ottenere anche il funzionamento da latch trasparente (quando il clock è a livello basso). Gli elementi dispongono anche di un reset/preset globale, che serve per specificare lo stato subito dopo la configurazione del dispositivo.

REALIZZAZIONE DI MEMORIE DISTRIBUITE

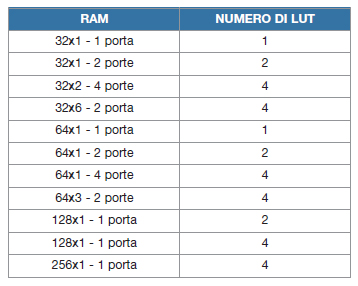

Le LUT presenti nelle slice di tipo M (slicem) possono funzionare da blocchi di RAM distribuita, e possono essere organizzati in una varietà di configurazioni in modo da ottenere le tipologie di memorie riportate in Tabella 1.

Tabella 1. Tipi di RAM implementabili da una slicem

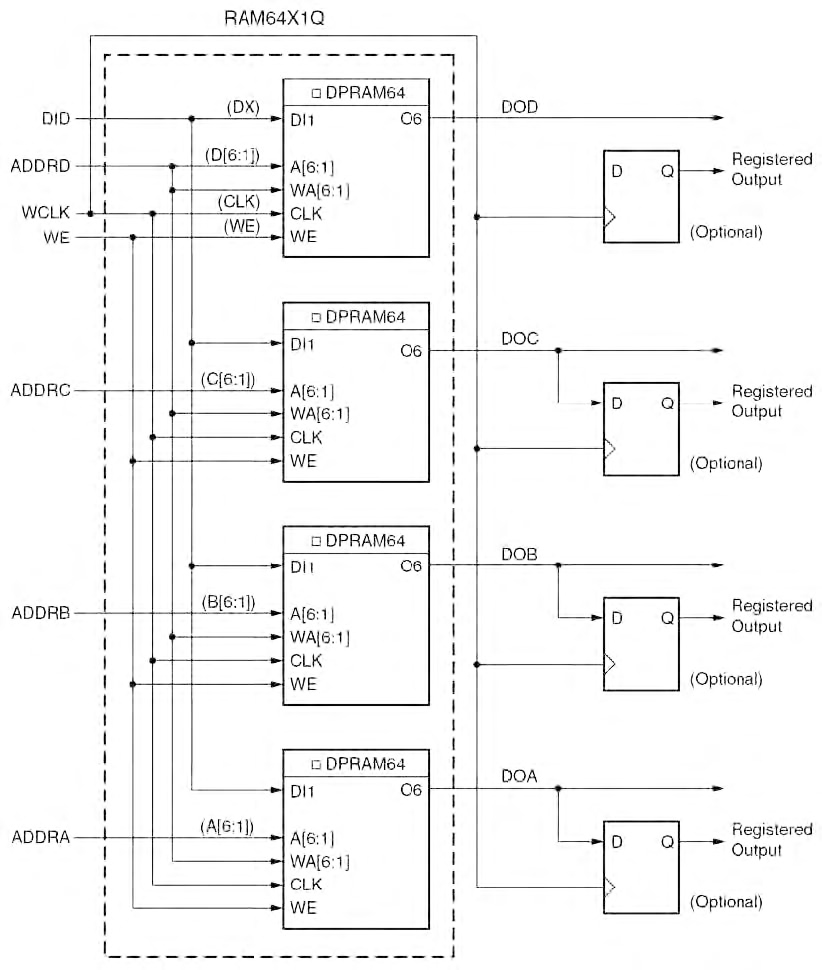

Come si può notare si possono realizzare diverse combinazioni di memorie a singola, a doppia e perfino a quadrupla porta. Questo significa che i dati contenuti in essi possono essere scritti e letti indipendentemente utilizzando anche due o quattro bus per i dati e gli indirizzi. Tutti i tipi di RAM così ottenuti hanno la caratteristica di essere sincroni in scrittura ed asincroni in lettura. In pratica la scrittura avviene in corrispondenza dei fronti di clock, quando il segnale WE è alto. I dati in uscita variano invece in maniera asincrona, e quindi cambiano al cambiare dell’indirizzo fornito. Se si vuole ottenere un comportamento sincrono anche in lettura, è possibile inserire dei registri sulle uscite, che saranno realizzati utilizzando gli stessi flip-flop presenti in ciascuna slice. L’utilizzo di uscite registrate permette di ridurre il tempo necessario per stabilizzare le uscite dopo il fronte di clock (clock-to-out), ma implica una latenza aggiuntiva di un ciclo di clock nel percorso dei dati. La possibilità di implementare blocchi di RAM distribuita di dimensioni relativamente grandi, ed in particolare a 4 porte, rappresenta una novità, ed è resa possibile dalla nuova struttura delle slice. La Figura 3 mostra il modo in cui una RAM a 4 porte da 64x1 bit viene implementata. Chiaramente le configurazioni viste possono essere utilizzate anche per implementare “ROM” organizzate nello stesso modo, riuscendo ad ottenere fino a 256x1 bit per ciascuna slice.

Figura 3. Configurazione RAM 64x1 a Quattro porte

IMPLEMENTAZIONE DI SHIFT REGISTER

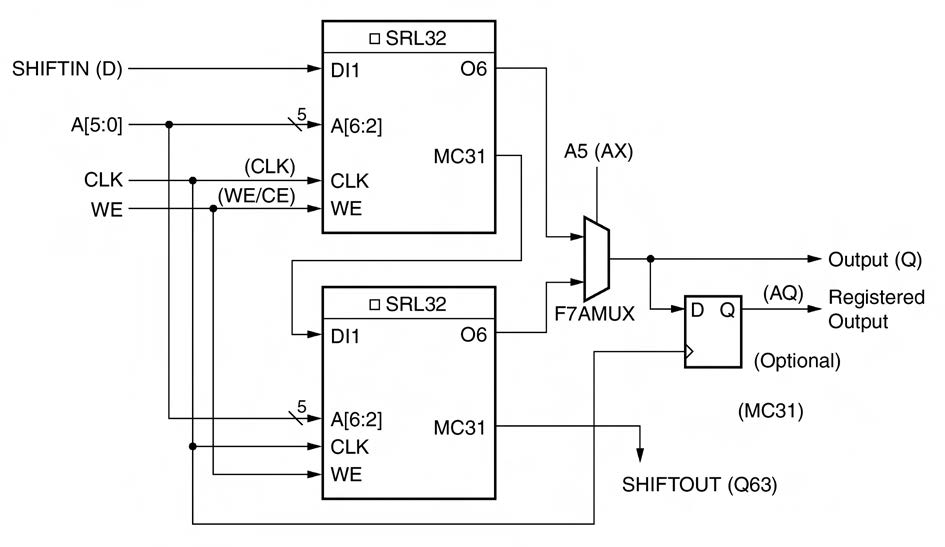

Una delle caratteristiche più interessanti ed utili delle slice di Xilinx, introdotta con la serie Virtex, è la capacità di configurare le LUT presenti nelle slicem come registri a scorrimento. Le slice dei dispositivi precedenti potevano implementare una struttura chiamata “SRL16”, che in pratica permetteva di utilizzare la RAM associata a ciascuna LUT come un registro a scorrimento lungo fino a 16 bit. Questa caratteristica si rivela estremamente utile, in quanto permette di ritardare i segnali di un certo numero di cicli di clock, senza la necessità di impiegare flip-flop (e quindi un numero elevato di slice). Grazie alla nuova struttura del CLB della Virtex-5, ed in particolare all’incremento del numero di ingressi delle LUT e del loro numero, questa caratteristica è ulteriormente estesa. Adesso infatti è possibile realizzare shift register lunghi fino a 32 bit utilizzando una sola LUT, e concatenare fino a 4 LUT in modo da realizzare un registro a scorrimento di lunghezza massima 128 bit utilizzando una sola slice! La Figura 4 mostra la configurazione utilizzata per uno shift register a 64 bit utilizzando due LUT. Le operazioni di scorrimento e di lettura dagli ingressi sono sempre sincrone con il fronte del clock.

Figura 4. Implementazione di un registro a scorrimento a 64 bit usando due LUT

IMPLEMENTAZIONE DI MULTIPLEXER

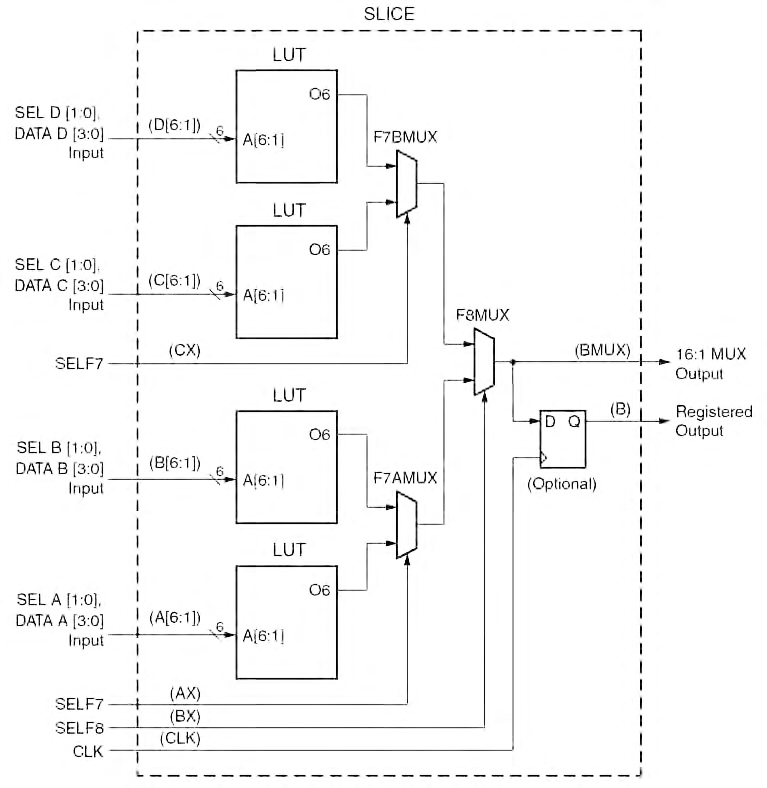

Negli ultimi anni, con la diffusione dei processori integrati nell’FPGA (sia come soft che come hard IP), è aumentato il bisogno di implementare un numero elevato di multiplexer per la gestione dei bus. Questa necessità è stata anche favorita dall’abbandono dei buffer three-state interni (BUFT) dalla serie Spartan-3 in poi. Il CLB delle Virtex-5 è stato quindi progettato anche per sopperire in maniera efficiente a questo bisogno. La particolare struttura delle slice, sia di tipo M che L, infatti permette di realizzare multiplexer di tipo 4:1, 8:1 ed 16:1. Per realizzare i multiplexer vengono utilizzate le LUT ed i tre multiplexer posti di seguito, che permettono di combinare i loro risultati. In questo modo un multiplexer 4:1 può essere realizzato utilizzando una sola LUT, e quindi fino a 4 mux possono essere implementati in una slice. Per realizzare un multiplexer 8:1 occorrono invece due LUT, e quindi 2 mux trovano posto in una slice. La realizzazione dei multiplexer 16:1 coinvolge tutte e 4 le LUT e tutti i multiplexer interni (Figura 5), e quindi impegna l’intera slice. Le uscite dei multiplexer possono essere anche registrate, utilizzando gli stessi flip-flop presenti nella slice.

Figura 5. Multiplexer 16:1 realizzato con una sola slice