Dimmi che interfaccia usi e ti dirò chi sei… Esistono molti modi di interfacciarsi con un microcontrollore, ma è difficile dire quale sia il migliore. Questa è l’occasione per fare un po’ di luce su due tecniche di interfacciamento seriale: SPI e I2C.

Interfacce seriali sincrone

Le interfacce seriali sincrone sono caratterizzate dalla presenza di un segnale di sincronizzazione (clock) che determina la cadenza con cui i dati transitano attraverso il bus. Tipicamente il segnale di sincronizzazione viene generato da una unità Master e viene utilizzato dagli Slave per la trasmissione e ricezione dati. Il vantaggio di un sistema di questo tipo risiede nel fatto che tutte le unità interessate nello scambio di informazioni possono comunicare indipendentemente dal loro oscillatore locale. Questo consente di interfacciare periferiche operanti a frequenze anche molto differenti. Due tipici esempi di interfacce seriali sincrone sono appunto SPI (Serial Peripheral Interface) sviluppata da Motorola e I2C (Inter Integrated Circuits) sviluppata da Philips. Lo scopo di questa trattazione è confrontare queste due soluzioni evidenziandone pregi e difetti.

Comunicazione SPI

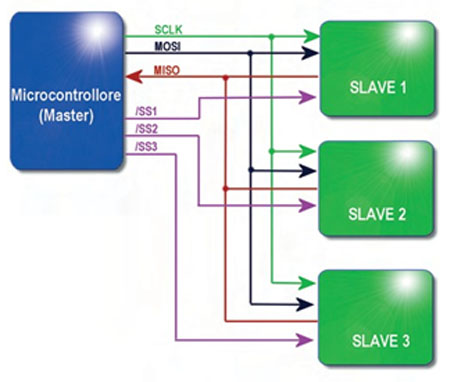

La comunicazione SPI (evoluzione della meno recente Microwire) prevede una periferica Master che comunica con diverse periferiche Slave e richiede un bus il cui numero di conduttori dipende dal numero di periferiche connesse. In particolare il bus è composto da 3+n fili (dove n è il numero di periferiche Slave). Il Master ha infatti una connessione dedicata per ciascuna periferica Slave (Slave Select) come mostrato in figura 1.

I segnali tipici di una comunicazione SPI sono i seguenti: SCLK: Serial shift CLocK. È il segnale di sincronismo generato dal Master. Tale segnale raggiunge tutte le periferiche Slave. MOSI: Master Out Slave In. Questa è la linea dati in uscita dal Master. Raggiunge in parallelo tutti gli salve e costituisce un ingresso per ciascuno di essi. MISO: Master In Slave Out. È la linea dati in uscita da ciascuno Slave e raggiunge l’unità Master.

/SS: Slave Select. È la linea di selezione di ogni singola periferica Slave. Esiste una linea /SS in uscita dal Master per ciascuna periferica Slave. Tali linee sono attive basse (quindi un livello logico basso su /SSn attiva la periferica n).

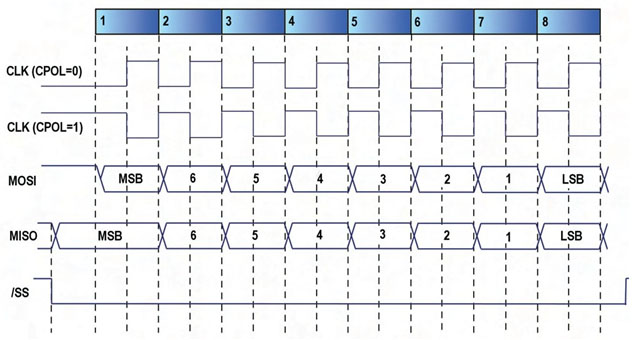

La distinzione tra le linee dati da e verso le periferiche permette di ottenere una comunicazione full-duplex. Un dispositivo SPI possiede due bit di configurazione detti CPOL (ClockPOLarity) e CPHA (Clock PHAse). Il primo determina lo stato idle del segnale di sincronismo: CPOL=0 significa che il segnale di clock è considerato idle quando è a livello logico basso. CPHA determina invece su quale fronte del segnale di clock vengono letti i dati: con CPHA=0 i dati in uscita dal Master vengono letti in corrispondenza del fronte di discesa e i dati in uscita dagli Slave vengono letti in corrispondenza del fronte di salita del segnale di clock. Disponendo di due bit di configurazione sono possibili quattro diverse modalità e due periferiche SPI connesse tra loro devono necessariamente utilizzare la stessa configurazione.

Tuttavia due delle quattro possibilità consentono a periferiche SPI di comunicare con le meno recenti periferiche Microwire garantendone la compatibilità. Nelle figure 2 e 3 sono mostrate due temporizzazioni tipiche di una comunicazione SPI per il trasferimento di un byte.

La figura 2 è riferita ad una comunicazione con CPHA=0 mentre la figura 3 è riferita ad una comunicazione con CPHA=1. In ciascun diagramma sono riportati i due casi CPOL=0 e CPOL=1. Le modalità di comunicazione SPI, determinate dalle impostazioni dei due bit di configurazione, sono riassunte nella tabella di figura 4.

| SPI MODE | CPOL | CPHA | CLK EDGE (CAMBIO DATO) | CLK EDGE (ACQUISIZIONE DATO) |

| 0 | 0 | 0 | Discesa | Salita |

| 1 | 0 | 1 | Salita | Discesa |

| 2 | 1 | 0 | Salita | Discesa |

| 3 | 1 | 1 | Discesa | Salita |

| Figura 4. Modalità di comunicazione SPI e relativa configurazione di CPOL e CPHA | ||||

Comunicazione I2C

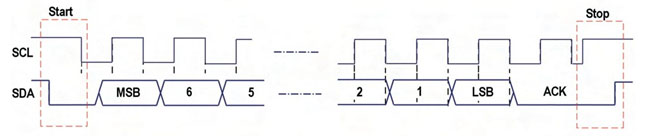

Una comunicazione I2C si avvale di un bus seriale a due fili ed è sempre di tipo half-duplex. La struttura di un bus I2C è riportata in figura 5.

I due segnali sono SCL (SerialCLock) e SDA (SerialDAta), sono entrambi bidirezionali e necessitano di una connessione verso il positivo di alimentazione mediante resistori di pull-up. Le linee SCL ed SDA sono infatti di tipo open collector per consentire l’implementazione della funzione AND cablato (wired AND) direttamente sul bus. A differenza di una comunicazione SPI, I2C è una architettura multiMaster in cui la periferica che inizia la trasmissione e genera quindi il segnale di sincronismo è designata come Master, mentre la periferica oggetto della transazione indirizzata dal Master è considerata come Slave. Una periferica designata come Master per una certa trasmissione, potrà quindi essere anche uno Slave per una trasmissione successiva. La periferica Slave può in ogni momento rallentare o addirittura interrompere la comunicazione del Master, mantenendo a livello basso la linea SCL (operazione nota come clock stretching e possibile grazie al meccanismo dell’AND cablato in cui uno zero logico su una linea condivisa prevale sempre sul livello logico alto). Questa tecnica permette la corretta comunicazione dati tra una periferica Master veloce ed una periferica Slave relativamente lenta. Il meccanismo dell’AND cablato consente anche di gestire l’arbitraggio: se due periferiche Master iniziano contemporaneamente una trasmissione dati, verrà data priorità a quella che trasmette per prima uno zero logico. I dati possono essere trasferiti a velocità massime di 100Kbps in modalità Standard, 400Kbps in modalità Fast e 3.4Mbps in modalità High-Speed. Nella modalità Standard gli Slave sono indirizzati con una modalità di indirizzamento a 7 bit, mentre nelle modalità Fast e High-Speed l’indirizzamento può essere a 7 o a 10 bit. Fisicamente il carico capacitivo sul bus non deve eccedere i 400pF per non compromettere la velocità di comunicazione. In figura 6 è riportato il diagramma temporale di una tipica comunicazione I2C. Le periferiche sono level-sensitive per cui il dato deve essere stabile per tutto l’intervallo di tempo in cui la linea SCL permane a livello alto. Solo quando la linea SCL è a livello basso è possibile commutare il bit sulla linea SDA a meno di due eccezioni:

- START: la periferica Master inizia una nuova comunicazione con una transizione da 1 a 0 mentre la linea SCL è a livello alto;

- STOP: la transizione da 0 a 1 da parte del Master mentre la linea SCL è alta segna il termine di una comunicazione.

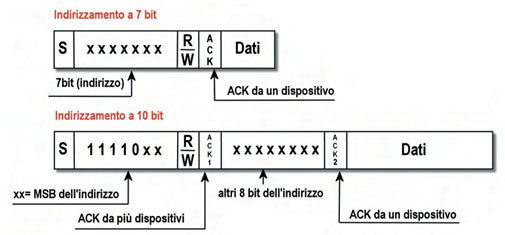

Nella figura 7 sono riportate le due tecniche di indirizzamento a 7bit e 10bit. Nel caso di indirizzamento a 7 bit, a seguito della condizione di start (indicata con S in figura 7) viene trasmesso un byte i cui primi 7 bit sono l’indirizzo dello Slave mentre l’ottavo bit indica se lo Slave indirizzato dovrà ricevere o trasmettere dati. Dopo l’invio del byte, solo una periferica Slave risponderà con un acknowledgment (ACK) a seguito del quale inizierà la trasmissione dati vera e propria. Nel caso di indirizzamento a 10bit, a seguito della condizione di start viene inviato un byte i cui i primi 7 bit sono costituiti dalla sequenza 11110xx dove xx sono i due bit più significativi dell’indirizzo della periferica target. L’ottavo bit determina ancora la direzione del flusso dati. L’invio di tale sequenza comporterà l’acknowledgement da parte di più periferiche (ACK1 in figura 7). Una volta ricevuti gli ACK si inviano i restanti 8 bit dell’indirizzo in modo che solo una periferica risponda con l’ACK (l’ACK2 in figura 7).

Meglio SPI o I2C?

Riassumendo quanto già visto in precedenza, SPI non necessita di un meccanismo di indirizzamento e lo scenario tipico vede un dispositivo Master (tipicamente un microcontrollore) ed uno o più dispositivi Slave periferici. I2C consente invece una architettura multimaster a due fili e ciascuna periferica (Slave) viene identificata con un indirizzo a 7 o 10 bit. Difficile dire quale delle due è la migliore in quanto la scelta di una soluzione dipende dalla velocità di trasmissione richiesta, dal numero di periferiche nonché dalla lunghezza del bus. Risulta pertanto più costruttivo operare una comparazione tra i due sistemi in modo che l’utente abbia tutti gli strumenti per valutare quale delle due soluzioni è quella ottimale per la propria applicazione. La comparazione è riportata nella tabella a fondo pagina.

| SPI | I2C |

| CONNESSIONE DELLE PERIFERICHE | |

| Le periferiche vengono connesse usando un minimo di tre fili e per questo motivo l’interfaccia SPI viene anche indicata come 3-wire interface. Le periferiche interconnesse condividono anche le stesse linee di alimentazione e, nel caso di più slave, è necessario disporre anche di un segnale /SS di abilitazione della singola periferica. Per la connessione di un master ed N slave sono quindi necessari 3+N fili oltre alle due linee di alimentazione. | Le periferiche vengono connesse tra loro mediante due fili. Il protocollo prevede l’indirizzamento delle periferiche mediante un identificativo a 7bit o 10bit (nel primo caso sono indirizzabili 27=128 periferiche mentre nel secondo caso 210=1024 periferiche). In nessuno dei due casi è richiesto un chip select. |

| VELOCITÀ DI COMUNICAZIONE | |

| La comunicazione dati in SPI può raggiungere anche i 10Mbps. Il grande vantaggio della comunicazione SPI in termini di velocità è la modalità full-duplex che consente lo scambio dati nelle due direzioni simultaneamente. | La comunicazione è half-duplex e può raggiungere velocità massime diverse in base alla modalità di trasmissione. In particolare:

Standard mode: max 100Kbps |

| ARCHITETTURA DI CONNESSIONE | |

| Architettura master-slave. In una comunicazione SPI è consentita la presenza di un solo master ed uno o più slave. Tuttavia è possibile implementare una architettura multimaster gestendo opportunamente via software le periferiche utilizzando il segnale /SS (Slave Select). | Architettura multimaster. Il protocollo prevede un sistema di arbitraggio basato su AND cablato che consente la gestione di conflitti generati dalla trasmissione dati contemporanea da parte di più periferiche. Per le caratteristiche dell’AND cablato, viene data priorità alla periferica che trasmette per prima uno zero logico. |

| IMMUNITÀ AL RUMORE | |

| La lettura/scrittura dati viene effettuata sul fronte di salita o di discesa del segnale di clock a seconda della modalità di comunicazione scelta. Questo aumenta fortemente l’immunità al rumore in quanto il dato viene campionato solamente per un breve periodo di tempo. | La comunicazione è level sensitive il che significa che il dato deve essere stabile per il tempo in cui il segnale di clock è attivo (livello alto). Minore è la velocità di comunicazione maggiore è tale intervallo di tempo tanto che un livello di rumore particolarmente elevato può compromettere il singolo bit provocando la transazione di una informazione errata. |

Conclusioni

Se l’applicazione prevede l’interconnessione di molti dispositivi tra cui possono esservi più microcontrollori funzionanti come Master, I2C diviene in questo caso una scelta obbligata. Lo stesso vale se si intende minimizzare le interconnessioni per semplificare lo sbroglio o per risparmiare porte di I/O sul microcontrollore. Se l’obiettivo è alta velocità di trasmissione, basso costo ed alta immunità al rumore, allora la scelta non può che ricadere su una interfaccia SPI, rinunciando però ad una architettura multimaster e sacrificando qualche I/O in più sul vostro microcontrollore.

Leggi anche:

I2C: risoluzione delle problematiche comuni

L’SPI come canale di comunicazione: mettiamolo alla prova su Archiduino

I2C: un viaggio alla (ri)scoperta del protocollo, tra basi e funzioni avanzate

Cosa rende felice un ingegnere?

Uno dei grandi dilemmi, è sempre stato scegliere il giusto standard di comunicazione. Ottimo articolo.

Ciao Emanuele, molto chiaro, professionale e istruttivo questo articolo.

Ho trovato molto utile la tabella in cui si confrontano le due soluzioni con i pro e i contro; un approccio veramente “esaustivo” e “ingegneristico”. Sarà certamente di molto aiuto nella formazione culturale di chi, per hobby, passione o lavoro, si trova a dover scegliere il tipo di seriale da utilizzare nelle sue realizzazioni. Un grande grazie per questa bella “iniezione culturale”.

Credo sia un articolo molto utile a chi deve scegliere la periferica da utilizzare, semplificando, l’I2C più lenta ma gestibile già con solo due I/O, mentre l’SPI più veloce ma con necessità di almeno 3 I/O. Comunque un salto di qualità rispetto all’ormai obsoleta RS232 (anche se in alcuni ambienti ha un suo perché)