Così come la struttura dei componenti a semiconduttori sta sempre più riducendosi, anche la tensione nominale di alimentazione tende ad abbassarsi con il vantaggio, naturalmente, di minori consumi e di velocità operative sempre maggiori. In questo articolo si vedrà come collegare fisicamente una memoria, funzionante con una tensione di 3V, con un sistema digitale a 5V. Ovvero, analizzeremo alcune tecniche per l’interfacciamento di una memoria DataFlash a 3Volt con un microcontrollore alimentato a 5Volt. La tensione che deve alimentare la DataFlash deve essere compresa tra 2,7V e 3,6V. Innalzandola ulteriormente si rischia di danneggiare seriamente il modulo.

DEFINIZIONE DEI LIVELLI LOGICI

Attualmente, i sistemi logici principali sono rappresentati dagli standard TTL e CMOS. È importante capire a fondo le differenze esistenti nell’interfacciamento di una DataFlash con questi due modelli differenti.

Livelli logici TTL:

In questo standard, la minima tensione d’ingresso VIH per rappresentare un valore logico 1 (vero) è di 2,0V e la massima tensione VIL per rappresentare uno stato logico 0 (falso) è di 0,8V.

Livelli logici CMOS:

In questo standard invece, la minima tensione d’ingresso VIH per rappresentare un valore logico 1 (vero) è pari a (Vcc x 0,7). Ad esempio, in un sistema alimentato a 5 V, il valore “alto” è assicurato da un potenziale di almeno 3,5V. Invece la massima tensione VIL per rappresentare uno stato logico 0 (falso) è pari a (Vcc x 0,2). Riferendoci all’esempio precedente, esso sarà uguale a 1,0V.

FOCALIZZAZIONE DEI PROBLEMI

Per capire pienamente i problemi derivanti da un interfacciamento di un dispositivo funzionante a 3V con uno a 5V, occorre considerare i seguenti due aspetti:

- Esigenza di adattamento dei due livelli di Input e Output dei due dispositivi;

- Regolazione della tensione sul DataFlash.

I pin del DataFlash hanno una buona tolleranza fino a 5V e non presentano problemi di sorta negli standard TTL e CMOS. I Pin di Output comunque operano soltanto entro le specifiche della DataFlash con un limite di alimentazione imposto a VCCDF. Tipicamente la DataFlash dispone di un pin data (in Output) funzionante in modalità seriale e 8 pin funzionanti in modalità parallela. Nell’articolo verrà presa in considerazione la trasmissione seriale, in quanto non tutti i modelli prevedono la trasmissione parallela. Il pin RDY/BUSY è un Output Open Collector ed indica lo stato corrente del dispositivo. Può essere connesso direttamente ad un’alimentazione di 5V tramite una resistenza di pull-up di 1Kohm.

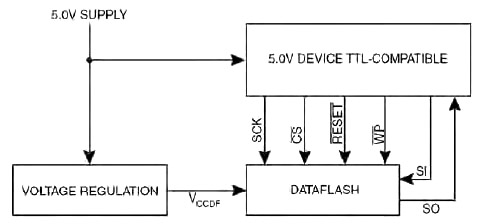

Pilotaggio di un ingresso TTL

Per pilotare un ingresso TTL compatibile da un’uscita DataFlash, occorre far corrispondere ed incrociare i segnali minimi TTL necessari. L’uscita della DataFlash opera a VCCDF – 0,2V. Comunque nel caso peggiore, o se il livello VCCDF è insignificante, il livello minimo di uscita raggiungibile dalla DataFlash è di VOH = 2,7V – 0,2V= 2,5V. La figura 1 illustra un tipico sistema dove una DataFlash sta pilotando un carico TTL compatibile.

Pilotaggio di un ingresso CMOS

Quando un segnale di output, proveniente dal pin SO (Serial Output) della DataFlash, pilota un ingresso CMOS, sorge qualche problema. Infatti un ingresso CMOS compatibile funzionante a 5V, richiede un segnale d’ingresso VIH pari ad almeno 3.15V, valore tuttavia più grande del livello d’uscita che la DataFlash può fornire, nel peggiore dei casi. Poiché l’output della DataFlash non è capace di pilotare direttamente l’ingresso del dispositivo CMOS, è richiesto un metodo alternativo di traslazione. La figura 2 mostra l’esigenza della presenza di un traslatore di livello, per raggiungere lo scopo.

SOLUZIONI POSSIBILI

Esistono diverse soluzioni da adottare per risolvere il problema delle traslazioni di tensioni. Ecco quelle più comunemente utilizzate.

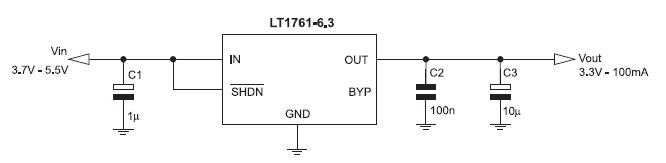

Serie LT1761 Linear Technology

Un tipico regolatore di tensione è rappresentato dall’integrato LT1761 e le sue evoluzioni. Esso provvede ad ottenere una tensione di 3,3V da una tensione di alimentazione di 5V. È molto stabile e soprattutto immune al rumore. La figura 3 mostra un possibile schema applicativo.

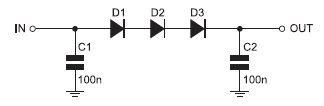

Semplice convertitore di tensione con diodi

Un’altra tecnica per abbassare la tensione è quella di utilizzare tre diodi al silicio, come mostrato in figura 4.

Il valore di soglia di ciascun diodo (circa 0,7V di caduta) contribuisce ad abbassare la tensione totale di circa 2,1V. I vantaggi di questa soluzione sono da ricercarsi nella praticità, economicità circuitale e, soprattutto, nell’ingombro molto limitato. La limitazione invece è nella necessità di alimentare il modulo con una tensione di almeno 4,8V, per assicurare un’uscita di 2,7V. Scegliendo diodi con valori di soglia differenti, è possibile variare con precisione l’intera caduta di tensione.

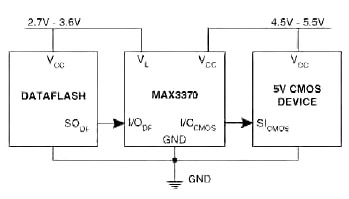

Convertitore Maxim MAX3370

Il circuito illustrato in figura 5, utilizza l’integrato della Maxim MAX3370 come adattatore di tensioni.

Esso adatta infatti il basso voltaggio del dispositivo della DataFlash con la tensione CMOS compatibile a 5V.

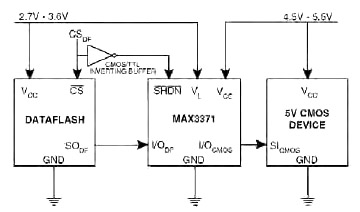

Convertitore Maxim MAX3371

Il circuito illustrato in figura 6 utilizza invece l’integrato MAX3371.

Questo dispositivo include un controllo attivo sull’uscita bassa del pin SHDN, permettendo un flusso dati bidirezionale, semplicemente scollegando la resistenza interna di pullup. In ogni caso è necessario aggiungere al circuito un inverter addizionale, tra il DataFlash e il pin SHDN del MAX, per facilitare il trasporto del segnale. Il MAX3370 e il MAX3371 operano ad una velocità di trasferimento pari a 2 Mbps, valore più che sufficiente per la maggior parte delle applicazioni.

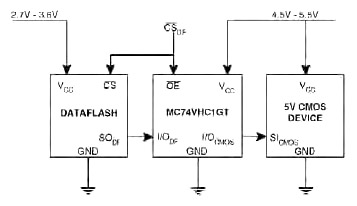

Buffer MC74VHC1GT

Un’altra alternativa per la traslazione dei livelli è rappresentata dal buffer non invertente MC74VHC1GT (figura 7).

Questo dispositivo provvede ad una perfetta traslazione logica, mantenendo pienamente la compatibilità CMOS e TTL. Il dispositivo incorpora anche una funzione che permette l’indirizzamento dell’uscita su un bus multiplo.