Negli ultimi anni i regolatori a basso drop-out sono stati usati per alimentare gli FPGA che richiedono basse tensioni ed alte correnti, con problemi di interferenze e limitazioni nella risposta ai transienti. Grazie alle recenti innovazioni del settore, i nuovi LDO non presentano più problemi di prestazioni.

I circuiti integrati a corrente elevata e bassa tensione come i dispositivi a logica programmabile (PLD), tra cui FPGA, DSP, µP e ASIC, sono diffusi in quasi tutti i sistemi embedded destinati a vari settori, ad esempio industriale, comunicazione, telecomunicazioni, server, videogiochi, apparecchiature medicali, beni di consumo audio/video e automotive. Gli FPGA consentono di realizzare applicazioni molto innovative in questi segmenti di mercato. Gli istituti di ricerca di mercato In-Stat e Gartner prevedono che nel 2010 gli FPGA registreranno una crescita superiore ai 2,5 miliardi di dollari. Uno dei fattori decisivi per l’utilizzo degli FPGA nelle applicazioni automotive è la possibilità di eliminare l’errore umano come, ad esempio, nei sistemi anticollisione. Anche i sistemi di sicurezza disposti dai governi nazionali richiedono l’uso degli FPGA, ad esempio i sistemi ABS, i sistemi di controllo della stabilità e i sistemi di sospensioni indipendenti a controllo elettronico. La combinazione di corrente elevata, bassa tensione e rapida risposta ai transienti dell’attuale generazione di processori FPGA e ASIC pone esigenze ancora più rigorose ai dispositivi che alimentano i canali principali, di I/O e i tranceiver. Questi circuiti integrati digitali sono potenti, ma mutevoli dal punto di vista dell’alimentazione. In genere per alimentare questi dispositivi venivano utilizzati regolatori a commutazione più efficienti che, però, comportano potenziali problemi di interferenze e limitazioni in termini di risposta ai transienti e layout. Per questo negli ultimi anni gli LDO sono stati usati in alternativa per queste applicazioni, ma anche loro avevano alcune limitazioni. Grazie alle recenti innovazioni del settore, la tendenza è cambiata e i nuovi LDO non presentano più problemi di prestazioni.

LE SFIDE IN MATERIA DI PROGETTAZIONE

Sulla scorta della legge di Moore, le larghezze delle tracce nelle produzioni dei wafer diminuiscono sempre più, consentendo a questi circuiti integrati di funzionare con tensioni più basse. Correnti più elevate e un funzionamento con tensioni di uscita inferiori per molti rail di tensione d’ingresso richiedono un aumento del consumo energetico. Occorre quindi un packaging innovativo per far uscire il calore dal circuito integrato di potenza. Per gli LDO, la capacità di operare con basso dropout, riduce al minimo il differenziale tra la tensione di ingresso e di uscita, mentre il regolatore mantiene la regolazione e la stabilità dell’uscita riducendo la dissipazione di calore e i problemi termici. I requisiti in termini di PSRR elevato e basso rumore di tensione in uscita sono altre due sfide da affrontare. Un dispositivo con elevata reiezione della tensione può più facilmente filtrare e reiettare il rumore all’entrata, ottenendo un’uscita pulita e stabile. Inoltre un dispositivo con basso rumore di tensione in uscita su un’ampia banda passante è adatto per alimentare i moderni rail a basso rumore dove la sensibilità al rumore è un elemento di cui tener conto nella fase di progettazione. Man mano che i requisiti di velocità per gli FPGA di fascia alta aumentano, la tolleranza al rumore dell’alimentazione continua a diminuire per ridurre al minimo i bit error. Questi errori digitali dovuti al rumore riducono drasticamente le velocità di trasmissione dati effettive di questi PLD ad alta velocità. Il rumore dell’alimentazione in uscita a correnti elevate è decisamente un fattore importante, difficile da ottenere. Le alte velocità dei transceiver, ad esempio negli FPGA, impongono livelli di corrente più elevati dovuti al maggiore consumo energetico della commutazione dei circuiti. Questi circuiti integrati sono veloci, possono passare da una corrente di carico quasi vicina allo zero a diversi ampere in qualche decina o centinaia di nanosecondi, richiedendo un regolatore con una risposta ai transienti ultrarapida.

UN TIPO DI REGOLATORE PER ALIMENTARE I CIRCUITI INTEGRATI DIGITALI

Un regolatore lineare con adeguate specifiche è la soluzione ideale per alimentare questi nuovi FPGA. Ma per poter usare un LDO, occorrono le seguenti caratteristiche:

# rapida risposta ai transienti

# funzionamento entro un ampio intervallo di tensione di entrata/uscita

# elevata corrente di uscita

# rumore in uscita molto basso # dropout molto basso

# ottima resa termica

# PSRR ad alta frequenza

# funzioni di debug del sistema, come caratteristica addizionale.

LDO ULTRAFAST™

L’LT®3070 è un regolatore lineare a programmazione digitale che presenta la tensione di dropout più bassa, il rumore più contenuto e la risposta ai transienti più veloce di qualsiasi altro LDO monolitico da 5A attualmente in commercio. L’architettura basata su MOS consente di avere una tensione di dropout di soli 85 mV a pieno carico, senza variazioni della corrente al pin di massa, considerata la variazione della tensione di entrata o uscita. Il rumore di tensione in uscita a 5 A è di soli 25 uVRMS su una larghezza di banda compresa tra 10 Hz e 100 kHz, mentre il PSRR è di 30 dB a 1 MHz. La larghezza di banda a guadagno unitario di 1 MHz e i condensatori ceramici in uscita da appena 15 uF assicurano che l’LT3070 risponda a brusche variazioni di carico da 4,5 A con un overshoot/undershoot di 30 mV, con un considerevole risparmio in termini di ingombro delle capacità complessive, di spazio e costi. Vedere la figura 1 per maggiori dettagli.

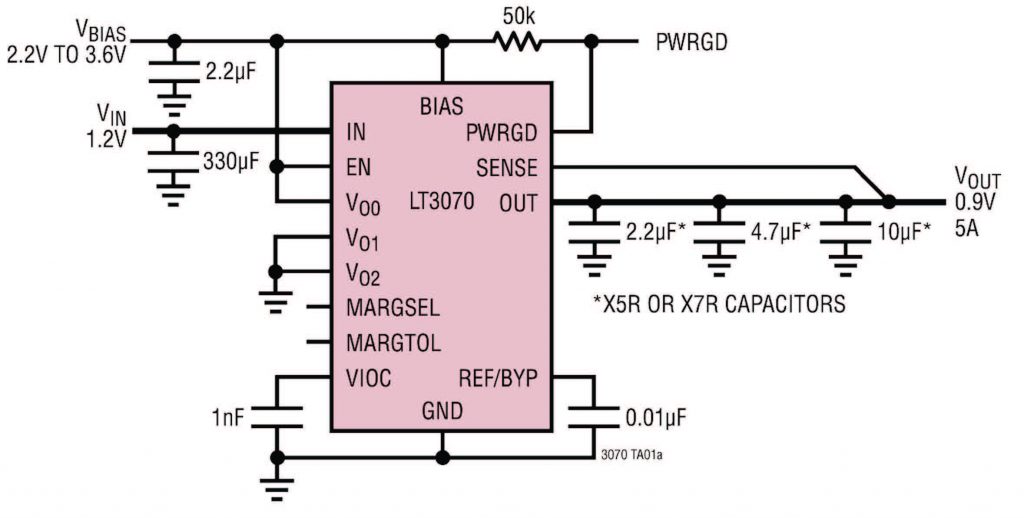

Figura 1: tipico circuito applicativo dell’LT3070.

L’LT3070 è l’ideale per alimentare in modo efficiente dispositivi a bassa tensione e corrente elevata. La tensione di uscita dell’LT3070 può essere programmata in modo digitale nell’intervallo compreso tra 0,8 V e 1,8 V con incrementi di 50 mV. La precisione si attesta su un valore di ±1% rispetto alla linea, al carico e alla temperatura. La funzione di margining digitale consente di regolare la tensione di uscita del sistema in incrementi di ±1%, ±3% o ±5%, funzionalità molto utile durante il debug per lo sviluppo dei sistemi. Il segnale power good indica se la tensione di uscita è compresa nell’intervallo di regolazione o se il dispositivo è in condizioni di blocco da sottotensione (UVLO); il segnale indica anche eventuali guasti termici. L’LT3070 ha una tensione di alimentazione in ingresso compresa tra 0,95 V e 3,0 V, mentre la tensione di polarizzazione va da 2,2V a 3,6V. Quest’ultima fornisce il gate drive per il dispositivo di commutazione NMOS interno. Inoltre per ottenere una corrente di uscita superiore e garantire la distribuzione del calore su un PCB è possibile collegare in parallelo più dispositivi LT3070. Tramite una funzionalità di tracking nel dispositivo è possibile controllare un regolatore buck esterno in modo da mantenere l’LT3070 a una tensione di ingresso su un valore di VOUT + 300 mV, riducendo al minimo la dissipazione della potenza senza compromettere il PSRR. Se la tensione di uscita viene modificata dinamicamente, la funzionalità di tracking regola automaticamente la tensione di uscita del regolatore buck per garantire lo stesso livello di efficienza. Il circuito di protezione interno comprende il blocco UVLO e la protezione dal flusso di corrente inversa, funzionalità avanzate di limitazione della corrente con foldback della potenza e di arresto termico con isteresi. Infine l’LT3070 è disponibile in un package QFN-28 da 4 x 5 mm a basso profilo (0,75 mm) e caratteristiche termiche avanzate ed è in grado di operare con temperature di giunzione comprese tra -40°C e +125°C.

RISPOSTA AI TRANSIENTI ULTRARAPIDA

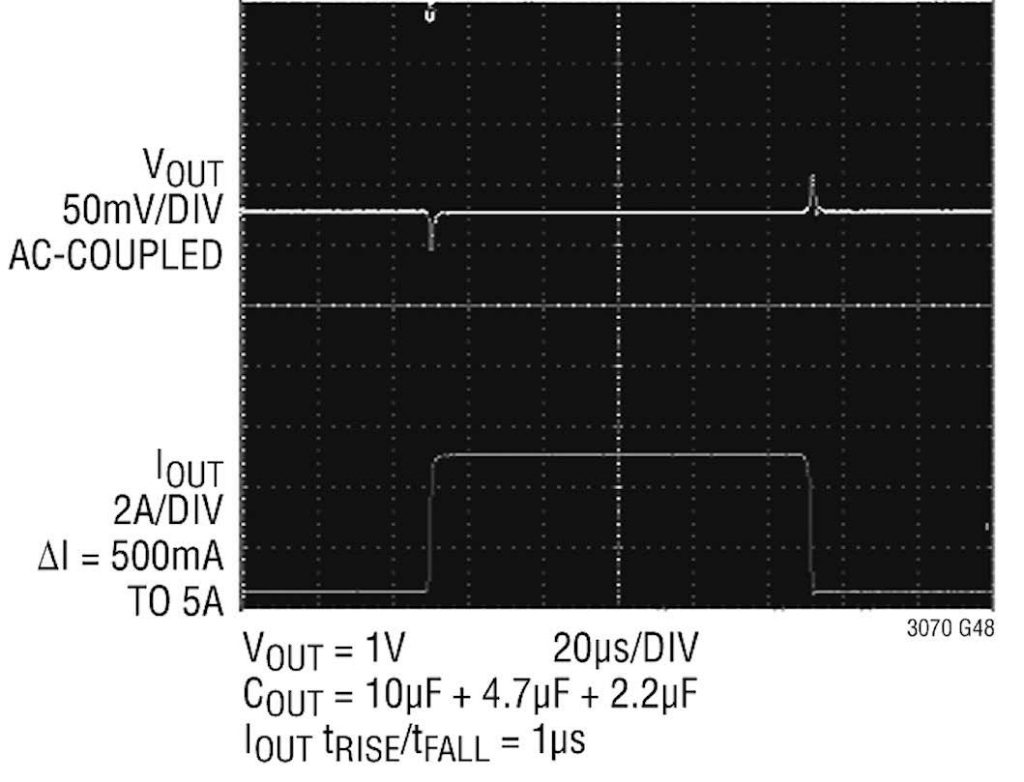

L’elevata larghezza di banda dell’LT3070 garantisce una risposta ai transienti ultrarapida usando condensatori ceramici in uscita a bassa ESR, con un considerevole risparmio in termini di ingombro delle capacità complessive, di spazio e costi. I condensatori di bulk non sono adatti per fronti di commutazione rapidi perché la loro ESL parassita è notevolmente più alta dell’LT3070 disaccoppiato con ceramici più piccoli. L’architettura dell’LT3070 gestisce un MOSFET di potenza a canale N interno come “source follower”. Questa configurazione consente all’utente di ottenere un regolatore con dropout bassissimo, risposta ai transienti ultrarapida e un ottimo PSRR ad alta frequenza. L’LT3070 raggiunge un’ottima larghezza di banda del regolatore e un’eccellente risposta ai transienti (figura 2), eliminando i costosi condensatori di bulk al tantalio o elettrolitici nelle più moderne applicazioni con microprocessori.

Figura 2: risposta ai transienti di carico dell’LT3070.

L’utente ottiene così un notevole risparmio in termini di ingombro delle capacità complessive. Altrettanto evidente è l’ulteriore risparmio in termini di costi di avviamento, costi d’acquisto/delle scorte e spazio. Gli LDO con source follower a canale N sono fondamentalmente più veloci dei loro equivalenti a canale P. La bassa impedenza del terminale di sorgente a canale N riduce l’impedenza di uscita effettiva dell’LT3070. L’uscita a impedenza levata dovuta al drain di un LDO a canale P richiede condensatori di uscita costosi, limitando l’effettiva larghezza di banda di quell’approccio. L’uscita a bassa impedenza dell’LT3070 consente la larghezza di banda del loop necessaria per avere un’ottima risposta ai transienti.

IL CONTROLLO VIOC

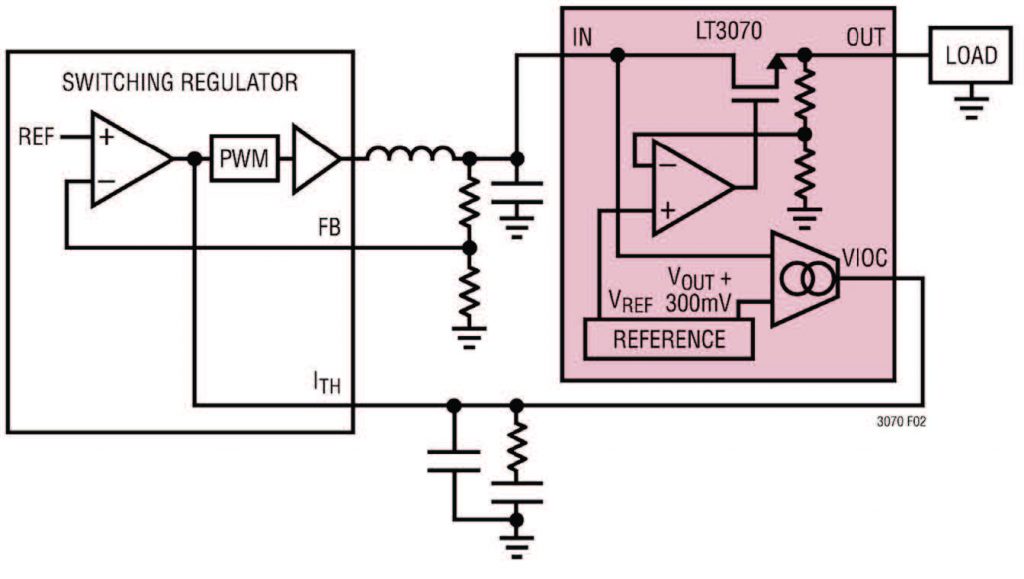

L’LT3070 comprende una funzionalità di tracking che consente di controllare il regolatore buck a monte che l’alimenta. Il pin VIOC è l’uscita di un amplificatore a transconduttanza integrato che genera o assorbe 250 uA di corrente. Esso può regolare l’uscita della maggior parte dei regolatori a commutazione LTC® o dei moduli di potenza LTM®, assorbendo corrente dal nodo di compensazione ITH. La funzione VIOC controlla il regolatore buck che alimenta l’ingresso dell’LT3070 mantenendolo a una tensione di ingresso di VOUT + 300 mV. Questa tensione differenziale VIN-VOUT di 300 mV viene scelta per garantire una rapida risposta ai transienti e un buon PSRR ad alta frequenza, riducendo al minimo la dissipazione della potenza e garantendo la massima efficienza. Ad esempio, la conversione da 1,5V a 1,2V e la conversione da 1,3V a 1V produce una dissipazione massima della potenza di 1,5W con una corrente di uscita di 5A. La figura 3 mostra la rete di resistenze di feedback del commutatore che imposta la massima tensione di uscita del regolatore a commutazione quando il regolatore lineare è disattivato.

Figura 3. diagramma a blocchi del controllo VIOC dell’LT3070.

Ma quando l’LT3070 è attivato, l’anello di feedback VIOC riporta la tensione di uscita del regolatore a commutazione a VOUT + 300mV. Con la funzione VIOC si crea un anello di feedback tra l’LT3070 e il regolatore a commutazione che va compensato in frequenza per la stabilità. Fortunatamente la connessione del VIOC a molti pin ITH del regolatore a commutazione LTC rappresenta una caratteristica ad alta impedenza che è il miglior nodo circuitale per compensare l’anello di feedback; inoltre occorrono minime variazioni di valore dei componenti di compensazione esistenti. Riassumendo, l’LT3070 ha le seguenti caratteristiche tecniche:

# corrente di uscita: 5A

# tensione di dropout: 85mV tipica

# VOUT programmabile in modo digitale: da 0,8 V a 1,8V

# marginatura dell’uscita digitale: ±1%, ±3% o 5%

# basso rumore in uscita: 25 VRMS (da 10 Hz a 100 kHz)

# disposizione in parallelo: due dispositivi per un’uscita di 10 A

# precisione del limite di corrente: ±15% # ±1% di precisione rispetto alle variazioni di linea, carico e temperatura

# stabilità con condensatori di uscita a bassa ESR ceramici (minimo 15 F)

# PSRR ad alta frequenza: 30 dB a 1 MHz

# funzione di attivazione/disattivazione dell’uscita

# pin VIOC per il controllo del convertitore buck per mantenere bassa la dissipazione di potenza e ottimizzare l’efficienza

# segnale PWRGD/UVLO

# limite di corrente con foldback

# arresto termico con indicatore di allarme rapido

# package QFN-28 da 4x5 mm a basso profilo (0,75 mm)

CONCLUSIONI

La tendenza per i circuiti integrati digitali ad alte prestazioni è di aumentare la corrente e ridurre le tensioni di esercizio, ridimensionando la tecnologia di produzione. Ma questi progressi comportano altre esigenze, ad esempio la necessità di una rapida risposta ai transienti, basso rumore e massima efficienza di funzionamento per ridurre al minimo il calore. In genere l’alimentazione di questi circuiti integrati digitali era affidata a regolatori a commutazione basati su induttori; per risolvere questi problemi Linear Technology offre invece una nuova generazione di regolatori lineari a bassa tensione che non richiedono l’uso dell’induttore. Il LT3070 è un regolatore lineare a programmazione digitale che presenta la tensione di dropout più bassa, il rumore più contenuto e la risposta ai transienti più veloce di qualsiasi altro LDO monolitico a 5A LDO attualmente in commercio. Inoltre questo dispositivo può essere utilizzato per la post-regolazione dei regolatori a commutazione.

La progettazione è un processo di ottimizzazione, i parametri di cui tener conto sono molti e diversificati, ma tra questi è molto importante il rumore e il package più idoneo per il funzionamento del circuito integrato e per il suo montaggio.

I tempi di bootstrap di questi componenti si sono ridotti notevolmente, per cui occorrono degli alimentatori efficienti con basse perdite soprattutto alle bassi tensioni.