Un’introduzione al tool HSL di MentorGraphics il quale promette una migliore produttività oltre a tempi ridotti di sviluppo e verifica che si traducono in maggiore qualità e incremento dei profitti.

L'elevata complessità logica dei moderni dispositivi (ASIC o FPGA) richiede la definizione di nuove metodologie che consentano maggiore produttività e minori tempi di sviluppo. È infatti ormai opinione condivisa che la riduzione del time-to-market sia il principale strumento a disposizione delle aziende per aumentare i profitti. In questa direzione, si è vista crescere negli ultimi anni la diffusione dei tool di progetto ESL (Electronic System Level).

Nel volume dal titolo ESL Design and Verification, pubblicato nel 2001 da Gartner Dataquest, società di analisti per il settore EDA, si definisce genericamente ESL una metodologia di progetto che prevede “l’adozione di un adeguato livello di astrazione al fine di migliorare la comprensione di un sistema e aumentare la probabilità di implementazione corretta delle sue funzionalità in modo efficace in termini di costi”. La maggior parte dei moderni sistemi ESL adotta linguaggi di alto livello come C++/SystemC o Matlab per la descrizione del sistema, ma vi sono anche esperienze di utilizzo di idiomi più recenti, come SysML.

Soluzioni esl per la sintesi di alto livello

Tra le soluzioni ESL rientrano in particolare i tool di sintesi HSL (High-Level Synthesis) che consentono di sintetizzare a livello RTL modelli in linguaggi astratti, come C++ o SystemC. Tali linguaggi astratti, in effetti, sono i modi nei quali, nell’approccio tradizionale diffusamente adottato, viene oggi specificato un generico sistema; la specifica risultante viene considerata alla stregua di un modello di riferimento. Il modello viene validato e ne sono quindi definite le possibili architetture, con riferimento ai vincoli di dissipazione di potenza, occupazione di area e massima frequenza di lavoro imposti dalla specifica applicazione. L’architettura selezionata viene infine descritta a livello RTL mediante linguaggi di descrizione hardware. In questa fase di pura codifica, l’intervento pesantemente manuale del progettista rappresenta una delle principali cause di errore; la descrizione RTL deve necessariamente essere verificata rispetto al modello di riferimento e il processo iterativo può richiedere, nel caso dei sistemi più complessi, lunghi periodi, con impatti negativi sul time-to-market del progetto e, quindi, sui relativi margini di profitto. I tool HSL citati in precedenza consentono di automatizzare tale ultima fase di sintesi, consentendo di derivare la descrizione RTL direttamente dal modello di riferimento di alto livello. Pur essendo automatizzata, la procedura è tuttavia direttamente controllata dal progettista, al quale viene lasciata libertà di scegliere le soluzioni implementative che ritiene più idonee. Da questo punto di vista i tool HSL rappresentano un interessante strumento per l’incremento della produttività, soprattutto nei progetti di elevata complessità logica. Una recente ricerca condotta da Mentor Graphics tra oltre 1.100 ingegneri in diversi àmbiti di applicazione ha mostrato (figura 1) che, nel 13% dei casi, l’azienda per la quale essi lavorano adotta già metodologie di progetto HSL; il 45% ha invece segnalato l’intenzione di valutare tali strumenti nel corso dell’anno. Secondo quanti avevano esperienza, anche indiretta, con tali tool, la riduzione media del tempo di progetto rispetto a quanto si avrebbe invece con tradizionali linguaggi di descrizione hardware è del 35%.

![Figura 1: la diffusione dei tool HSL nel 2011 (da [2]).](https://it.emcelettronica.com/wp-content/uploads/2019/09/la-diffusione-dei-tool-HSL.jpg)

Figura 1: la diffusione dei tool HSL

nel 2011 (da [2]).

Catapult C: sintesi rtl da descrizioni C++/Systemc

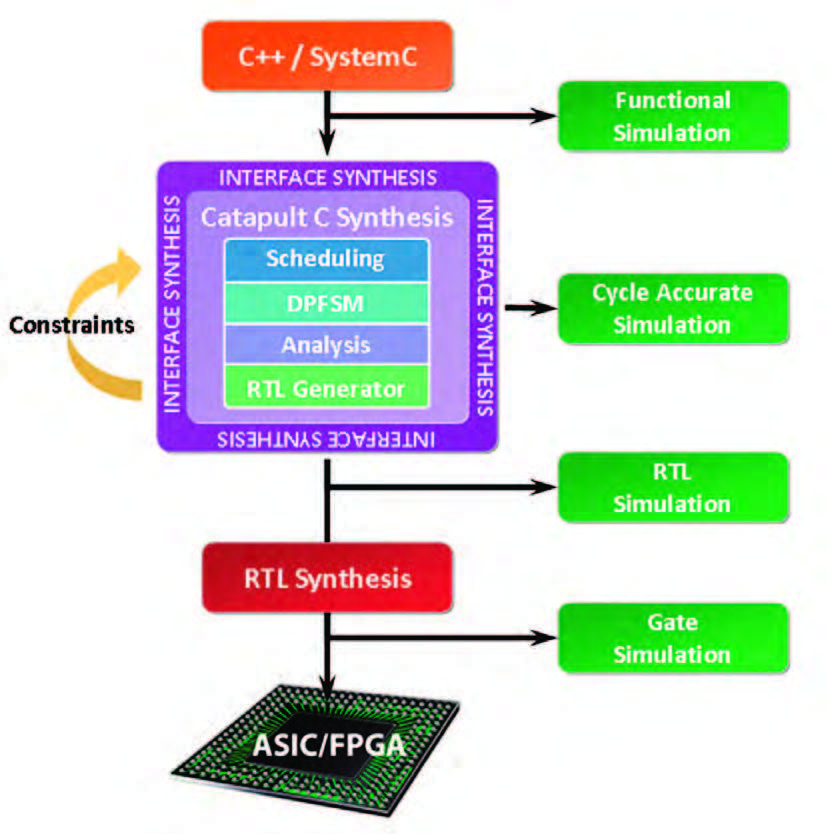

Catapult C Synthesis è il tool di progettazione HSL di Mentor Graphics. Il tool è stato riconosciuto da Gary Smith EDA come il migliore della categoria. Catapult è in grado di sintetizzare a livello RTL un’architettura a partire da specifiche in linguaggio C++ o SystemC (figura 2). Esso supporta molte delle principali funzionalità di tali linguaggi come classi, template e puntatori e modelli computazionali astratti di tipo untimed o cycle-accurate. La possibilità di gestire descrizioni gerarchiche, poi, consente agevolmente al progettista di costruire la propria architettura a diversi livelli di complessità; sono supportate metodologie di progetto bottom-up e top-down. Allo stesso tempo, il tool è in grado di identificare autonomamente possibili gerarchie consentendo al progettista di selezionare interattivamente la struttura ottimale. Catapult non richiede la definizione di interfacce di comunicazione esplicite ma è in grado di inferire direttamente queste dal codice C++ sulla base di constraint utente, grazie ad una tecnologia di sintesi proprietaria per la quale è stato richiesto brevetto. Il progettista è in questo modo in grado di modificare le modalità di implementazione delle interfacce di streaming dati ed handshaking tra i diversi moduli della propria architettura senza dover per questo modificare il codice sorgente, riducendo così la possibilità, evidentemente, di introdurvi errori. Di contro, l’adozione di descrizione TLM in linguaggio SystemC consente la modellizzazione cycle-accurate per le applicazioni che richiedano la sintesi di interfacce predefinite (nella integrazione, ad esempio, di System-On-Chip mediante protocolli standard) pur mantenendo ad alto livello la descrizione delle funzionalità del core dei moduli.

Figura 2: il flusso di progetto con Mentor Catapult C Synthesis.

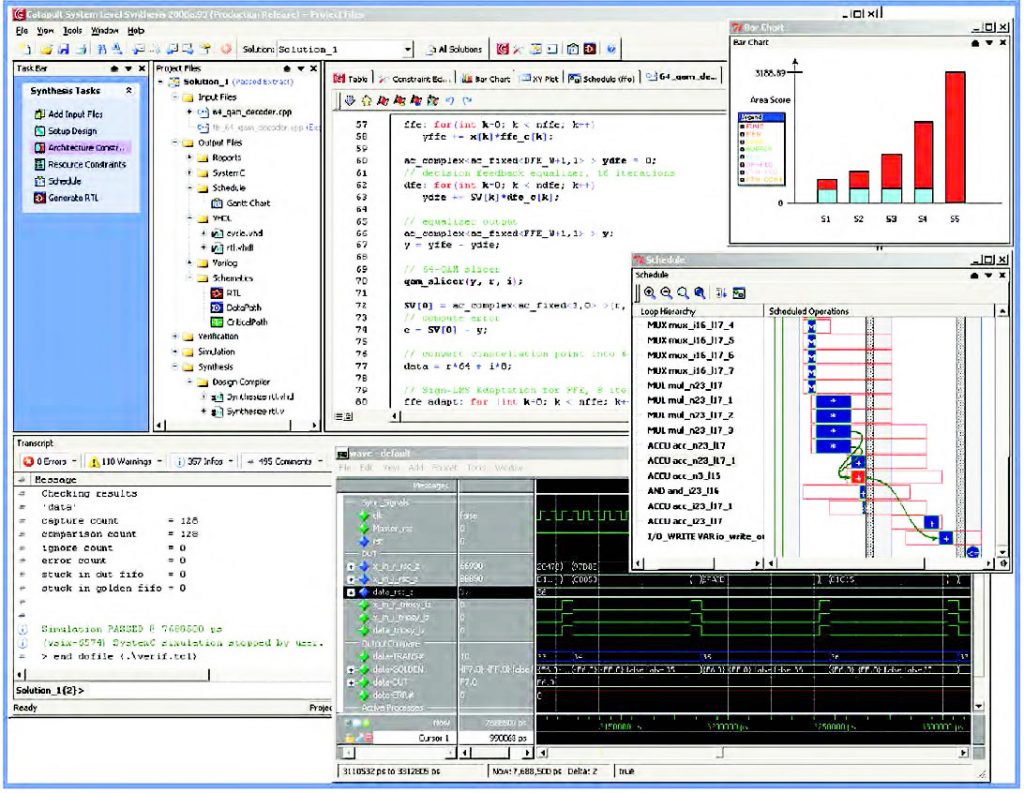

Analisi architetturale e ottimizzazione

La sintesi dell’architettura è automatica ed ottimizzata rispetto ai requisiti imposti in termini di occupazione di area, dissipazione di potenza e massima frequenza di funzionamento. Catapult (in figura 3 ne è mostrata l’interfaccia di lavoro) dispone, infatti, di funzionalità automatiche di merging e unrolling di loop, pipeling di path dati e di controllo, clock gating, mapping di memorie e resizing del parallelismo di queste, sharing e merging delle risorse. È tuttavia direttamente controllabile dal progettista mediante definizione di direttive specifiche. Dispone di strumenti di visualizzazione grafica dei risultati come diagrammi Gantt, viewer di schematico e di path critici e supporta cross-probing per l’identificazione delle sezioni del circuito fuori specifica. L’adozione inoltre di uno schema di scheduling delle risorse in stretta relazione con le caratteristiche dell’architettura target, grazie all’integrazione di librerie certificate direttamente dai relativi vendor, facilita il raggiungimento degli obiettivi di timing closure e consente di valutare in breve tempo occupazione di area e latenza di elaborazione dell’implementazione ottenuta.

Figura 3: l’interfaccia di lavoro di Catapult, strumenti per la definizione dei constraint e la visualizzaizone grafica dei risultati.

Verifica front-to-back completamente automatizzata

Catapult integra, inoltre, un flusso di verifica funzionale completamente automatizzato, fornendo funzionalità di linting e static code check del modello, report di code coverage, check a runtime. L’infrastruttura di verifica creata per il modello C++ può essere del resto riutilizzata per la validazione della descrizione RTL sintetizzata, così da assicurare elevata confidenza della validità dei risultati; il tool è in grado di generare automaticamente transactor e comparatori per il confronto delle uscite del modelli RTL e di quello in linguaggio C++/SystemC, considerando quest’ultimo come riferimento. Catapult si integra con la maggior parte dei tool di progetto ESL oggi disponibili in commercio, non soltanto proprietari, come Vista e Questa, distribuiti dalla stessa Mentor Graphics, ma anche di terze parti, tra i quali, ad esempio, DesignCompiler di Synopsys, RTL Compiler di Cadence, XPower di Xilinx, PowerPlay di Altera. Tra i vantaggi principali di Catapult possono sicuramente essere annoverati la riduzione drastica dei tempi di sviluppo e validazione (nessuna iterazione a livello RTL, generazione di codice RTL error-free), l’incremento della produttività dei progetti, la maggiore facilità di riutilizzo del codice. Tutte le principali aziende del settore elettronico come Hitachi, Ericsson, Nokia, STMicroelectronics o Alcatel Space hanno riportato storie di successo (in termini di riduzione dei tempi di progetto e verifica e di qualità dei risultati ottenuti) nella valutazione e nell’utilizzo del tool.

Un articolo veramente molto specialistico, sicuramente apprezzato da tutti coloro che con la progettazione dell’hardware programmabile hanno a che fare a livello professionale.

Nel mio caso mi ha fatto ricordare il corso che feci all’università di FPGA e VHDL e ho bene in memoria quanto non fosse esattamente banale lavorare con VHDL per chi viene dalla programmazione software.

Ritengo quindi che tool di questo genere siano assolutamente utili per chi è del settore, anche se immagino, da programmatore, che per sollevare il progettista dai dettagli e rendere ottimale la transcodifica si introduca di sicuro un overhead, probabilmente tanto più marcato quanto più complesso sarà il progetto di partenza. Questo molto probabilmente potrebbe andare a discapito dell’efficienza del risultato.