In questo articolo analizziamo caratteristiche e prestazioni dei microcontrollori PIC10F32X e PIC1XF150X di Microchip.

Sempre più sistemi richiedono oggi la necessità di estendere un’architettura standard mediante funzionalità specifiche dell’applicazione nel rispetto, tuttavia, della tendenza alla miniaturizzazione e alla integrazione spinta che caratterizza oggi l’elettronica in generale e, in particolar modo, il settore embedded. Un’interessante soluzione in questo senso è rappresentata dai nuovi modelli (Figura 1) di microcontrollori PIC10F(LF)32X e PIC1XF(LF)150X, annunciati da Microchip.

Figura 1: i nuovi micro di Microchip integrano un’architettura standard e nuove periferiche configurabili

ARCHITETTURA STANDARD

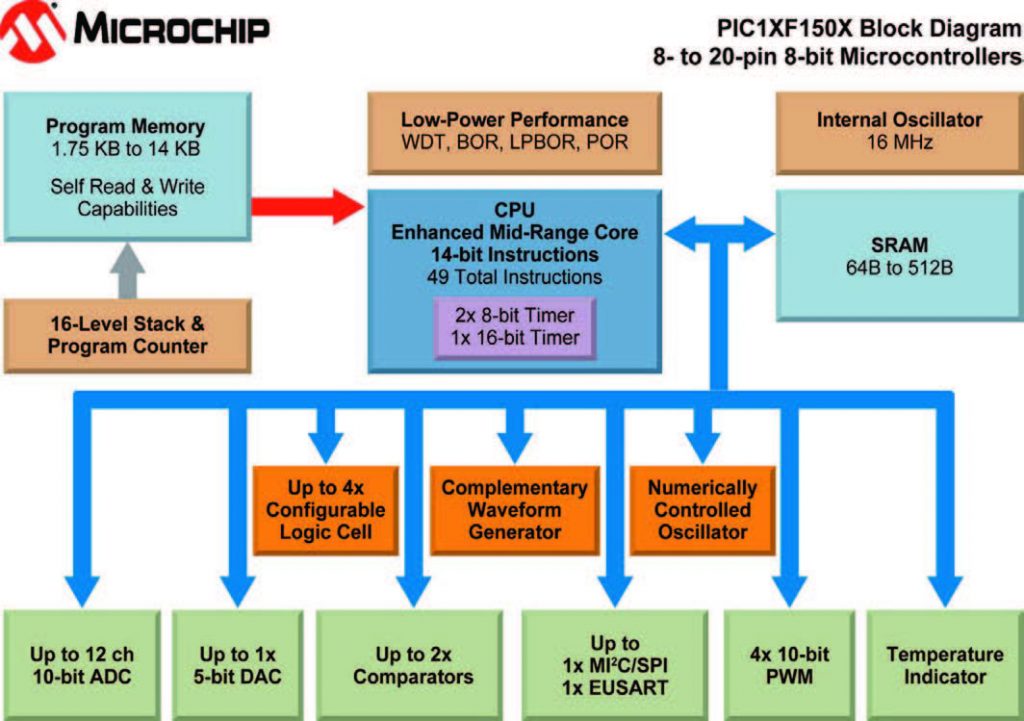

I dispositivi si basano (Figura 2) su una CPU RISC x14 a 8 bit caratterizzata da un insieme ridotto di istruzioni a 14 bit (sono solo 35 per il modello PIC10F32X e 49 per quello PIC1XF150X), indirizzamento di tipo diretto, indiretto e relativo, stack hardware a 8 o 16 livelli, frequenza di clock fino a 16 o 20 MHz per una capacità di calcolo fino a 5 MIPS. I micro sono caratterizzati dal supporto per un ampio intervallo di tensioni di alimentazione d’ingresso (da 1,8 a 5,5 V) e da ridotta dissipazione di potenza, richiedendo un assorbimento di corrente di soli 20 nA in stand-by e 30 μA/MHz in normali condizioni operative. I modelli della serie PIC10F32X integrano memoria programma di 896 byte (pari a 512 word) con capacità di self read e write e memoria dati da 64 byte, un oscillatore a 16 MHz, due timer a 8 bit e un PWM a 10 bit, tre canali ADC a 8 bit con riferimento di tensione fissa oltre alle nuove periferiche NCO (Numeric Controller Oscillator), CWG (Complementary Waveform Generator) e CLC (Configurable Logic Cell). Queste sono presenti anche nei modelli della serie PIC1XF150X; vi sono, però, in questo caso, fino a quattro moduli CLC e sono supportati da una memoria programmi fino a 14 kbyte e una di dati fino a 512 byte, un oscillatore integrato, due timer ad 8 bit e uno a 26 bit, fino a 12 canali ADC a 10 bit e un DAC a 5 bit, due comparatori, una porta MI2C/SPI e un EUSART, quattro uscite PWM a 10 bit e un indicatore di temperatura oltre ai circuiti WDT, BOR, LPBOR e POR. I nuovi microcontrollori sono disponibili in diversi package tra i quali, ad esempio (in funzione del modello selezionato) le versioni SOT-23 a 6 pin, PDIP a 8 o 14 pin o la più piccola QFN a 20 pin (di soli 4 x 2 mm2 di superficie).

Figura 2: architettura dei micro PIC1XF150X

LOGICA CONFIGURABILE

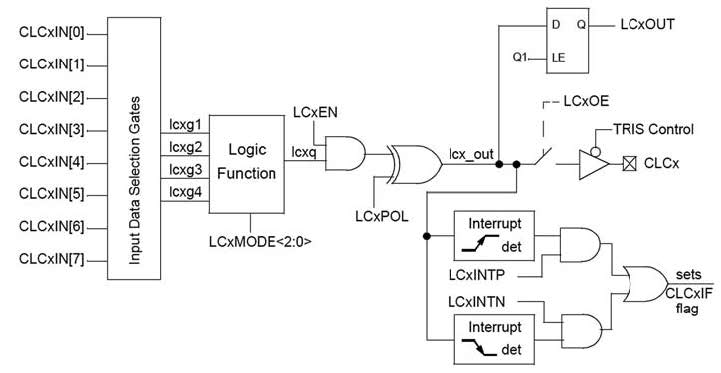

Caratteristica distintiva dei microcontrollori PIC10F(LF)32X e PIC1XF(LF)150X è, come citato inizialmente, la disponibilità di una periferica logica configurabile per implementare funzionalità specifiche dell’applicazione. Lo schema a blocchi semplificato di tale periferica è riportato in Figura 3.

Figura 3: architettura della periferica CLC, un modulo logico configurabile

Gli ingressi possono essere pilotati fino a 2 segnali di I/O, linee di clock interne, bit di registri o uscite di altre periferiche del microcontrollore. L’uscita, analogamente, può essere ridiretta verso un pin di I/O o connessa ad altre periferiche interne. Le funzioni logiche implementabili (a 4 ingressi) sono di tipo AND, NAND, ANDOR, AND-OR-INVERT, OR-XOR, ORXNOR ed è disponibile un elemento di memoria utilizzabile come latch S-R o come flip-flop di tipo D con ingresso di SET e RESET o di tipo J-K. È possibile abilitare la generazione di un’interruzione alla CPU in corrispondenza di una commutazione dell’uscita della funzione logica. Le funzionalità logiche in generale del blocco CLC non sono inoltre affette dalla modalità sleep. Applicazioni tipiche che fanno uso della logica CLC riguardano, ad esempio, l’implementazione di un encoder Manchester in congiunzione con la porta SPI, un divisore di frequenza, un circuito di wake-up condizionale dallo stato di sleep o anche un decoder in quadratura.

UN CIRCUITO PER LA GENERAZIONE DI FORME D’ONDA

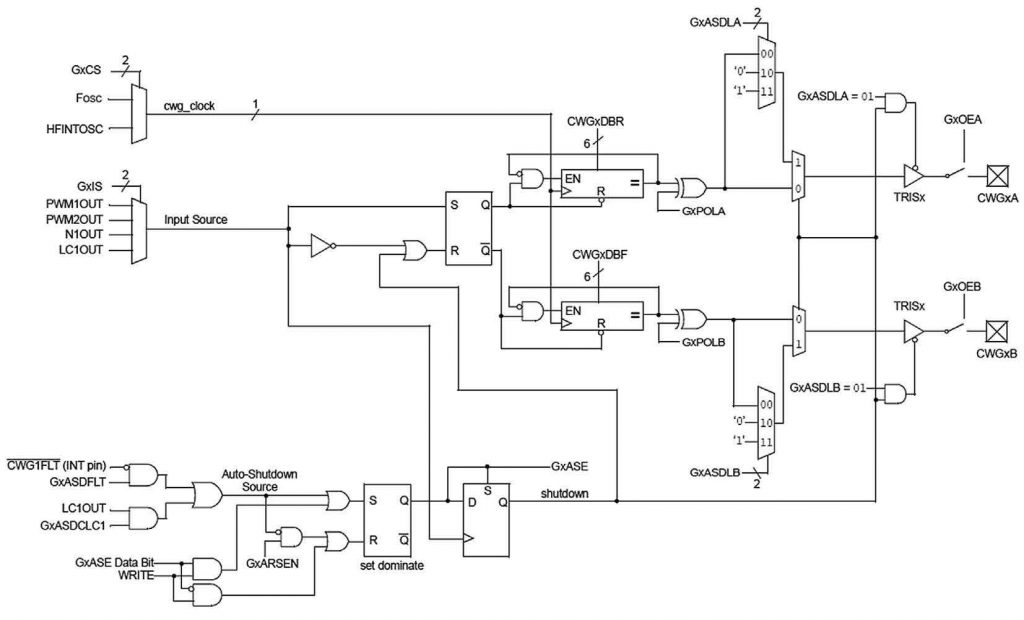

CGW (Complementary Waveform Generator) è la nuova periferica presente nei microcontrollori PIC10F(LF)32X e PIC1XF(LF)150X che consente di generare in uscita due segnali complementari a partire da una stessa forma d’onda di ingresso, proveniente, ad esempio, dall’uscita di uno dei moduli PWM già presenti a bordo. La Figura 4 mostra lo schema a blocchi della periferica.

Figura 4: architettura della periferica CGW, un generatore di forme d’onda complementari

Importante è la funzionalità di controllo dead-band che consente di evitare che i segnali complementari possano in qualche modo (a causa, ad esempio, dei vari ritardi introdotti sulle linee) essere contemporaneamente attivi; ciò è fondamentale quando i segnali sono usati per pilotare circuiti che devono operare in opposizione di fase. La periferica CGW contiene, infatti, due contatori a 6 bit che consentono di ritardare il fronte di salita di un segnale da quello di discesa della linea complementare, e viceversa. Vi è poi una funzionalità di auto shut down che consente di “spegnere” immediatamente le uscite a seguito di apposito comando, istruito in software o attivando una specifica linea di ingresso del microcontrollore. La condizione di shut down può essere resettata automaticamente o mantenuta fino a comando software opportuno. Come per la periferica CLC, le funzionalità proprie del modulo CWG non sono affette dalla particolare modalità di sleep del microcontrollore.

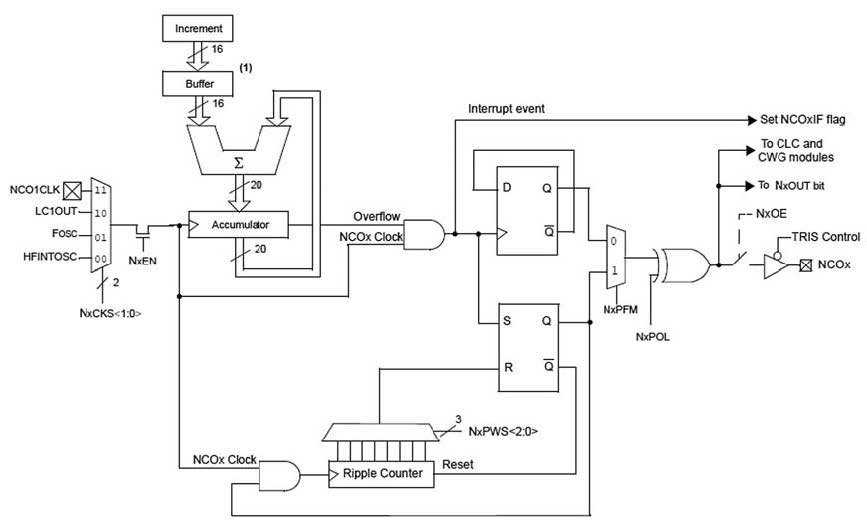

UN OSCILLATORE CONTROLLATO NUMERICAMENTE

Il circuito NCO (Numeric Controller Oscillator) è, infine, un oscillatore controllato numericamente. Consiste di un accumulatore a 20 bit che viene incrementato di una quantità configurabile in corrispondenza della transizione del segnale di clock di ingresso, selezionabile tra diverse sorgenti. Quando l’accumulatore va in overflow, è generata (se abilitata) un’interruzione alla CPU e la linea di uscita del modulo NCO commuta. L’incremento dell’accumulatore può essere configurato direttamente dalla CPU mediante appositi registri, rendendo così la periferica un vero e proprio divisore di clock con fattore arbitrario. In modalità FDP (Fixed Duty Cycle) l’uscita commuta il proprio stato in corrispondenza di ogni evento, generando così un segnale periodico avente duty cycle del 50%. In modalità PFM (Pulse Frequency Mode), invece, la linea viene attivata in corrispondenza dell’evento e resta attiva per un numero di colpi del segnale di clock di ingresso anch’esso configurabile, così da produrre un’uscita pulsata. L’uscita del modulo NCO può essere riportata su pin di I/O del microcontrollore o in ingresso ad altre periferiche interne. Come in precedenza, la periferica NCO continua a operare normalmente anche se il microcontrollore è in modalità di sleep, sempre che sia attivo il segnale di clock selezionato per il suo funzionamento.

TOOL E STRUMENTI DI SVILUPPO STANDARD

Tutti i nuovi microcontrollori citati in precedenza sono supportati dai tool di sviluppo standard di Microchip. MPLAB X, in particolare, è il nuovo ambiente di sviluppo con interfaccia grafica che migliora la precedente suite MPLAB 8, introducendo le funzionalità di Call Graph per la rappresentazione grafica dell’albero di chiamate a una funzione, la gestione di hyperlinks nel testo sorgente per una più semplice navigazione all’interno del codice, il parsing e l’accesso a template in tempo reale per una riduzione dei tempi di scrittura dello stesso, il supporto per configurazioni multiple all’interno del proprio progetto e versioni diverse del compilatore C. MPLAB C Compiler è il compilatore nativo ma una versione ottimizzata è disponibile anche presso HI-TECH; quest’ultima, adottando la tecnologia proprietaria OCG (Omniscient Code Generation) che estrae informazioni da più file per una generazione di codice più intelligente, consente un incremento della densità di questo fino al 50%. MPLAB PICkit 3, MPLAB REAL ICE e MPLAB ICD 3 sono, infine, debugger in circuit elencati in ordine crescente di prestazioni e costi; l’ultimo presenta anche capacità di emulazione in circuit.

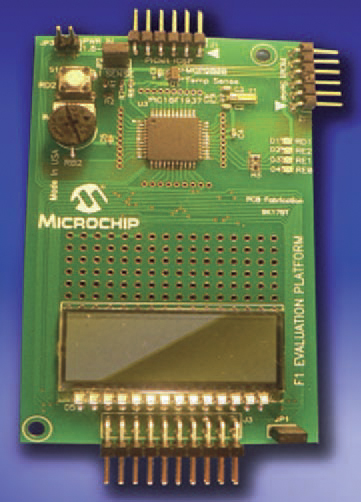

Per scopi di valutazioni sono infine disponibili la F1 Evaluation Platform e il PICDEM Lab Development Kit. La prima (Figura 6) rende disponibile il microcontrollore su un PCB dotato di un’area per prototyping, un potenziometro, un pulsante meccanico, un sensore di temperatura, un cristallo a 32 kHz e alcuni LED, oltre a un header di espansione (per la connessione, ad esempio, di una scheda di add-on per il controllo di motori DC brushless). Il solo microcontrollore e un header di espansione dove sono accessibili i relativi pin di I/O, oltre ad un’analoga area di prototyping, si trovano invece sul kit PICDEM Lab Development Kit; in questo caso la scheda consente di alloggiare fino a cinque diversi micro in altrettanti socket. Interessante è, poi, la guida inclusa all’uso della versione gratuita dell’ambiente di programmazione grafica Flowcode V3 di Matrix Multimedia. La maggior parte dei nuovi modelli annunciati da Microchip per la linea di microcontrollori PIC10F(LF)32X e PIC1XF(LF)150X sono già disponibili sul mercato per campionatura o produzioni in volumi. Il costo indicato sul sito web è inferiore a 40 centesimi di dollaro per acquisti dell’ordine delle 10.000 unità.

Figura 5: architettura della periferica NCO, un oscillatore controllato numericamente

Figura 6: la scheda di valutazione F1 Evaluation Platform