Per rispondere ai requisiti I²C sia per le interfacce IPMB (Intelligent Platform Management Bus) che per gli IPMC (Intelligent Platform Management Controller) impiegati nei sistemi AdvancedTCA può essere necessario far fronte a problemi complessi. Un progettista deve far sì che ciascuno shelf (backplane, cavi e IPMC) non superi il limite capacitivo di 690pF e che i segnali I²C soddisfino i requisiti relativi al tempo di salita. A tale riguardo è stato raccomandato il buffer per bus I²C, per aiutare gli IPMC a ridurre la capacità totale rilevata dal System Manager sulla IPMB, dividendo il bus del sistema in vari bus più piccoli, isolati elettricamente. In tal modo si fa un passo avanti nel soddisfare i requisiti relativi al tempo di salita poiché la capacità è proporzionale al tempo di salita. Tuttavia, questi buffer offrono ulteriori funzioni oltre all’isolamento capacitivo. Le applicazioni AdvancedTCA più frequenti richiedono collegamento in serie dei buffer, accelerazione incorporata del tempo di salita e altre funzioni dalle quali dipende l’affidabilità del sistema. Queste ulteriori funzioni assicurano funzionalità essenziale a qualsiasi IPMB e stanno diventando rapidamente caratteristiche principali dei prodotti offerti semplicemente in virtù della loro continua accettazione e richiesta crescente. L’LTC4307 di Linear Technology è uno di tali buffer che offre basso offset ingresso-uscita, accelerazione incorporata del tempo di salita e ripristino di un bus bloccato – funzioni che aiuteranno moltissimo i progettisti di shelf e blade nello sviluppo di robusti sistemi AdvancedTCA.

La richiesta di buffer per i bus

I primi bus I²C erano relativamente semplici: consistevano solo di alcuni dispositivi, confinati in una piccola area della scheda di circuiti. Parallelamente alla loro crescente diffusione sono aumentate l’ampiezza e la complessità dei sistemi, finché a un certo punto la capacità del bus non ha limitato la velocità a un valore inferiore a quello specificato; per risolvere questo problema sono stati sviluppati appositi buffer. Da allora, sono state sviluppate funzioni avanzate che assicurano importanti miglioramenti delle prestazioni di sistemi ma che non sono conosciute o capite molto bene; da qui la naturale propensione di alcuni progettisti di sistema di trascurare l’importanza dell’uso dei buffer per i bus o di semplificarne eccessivamente la selezione.

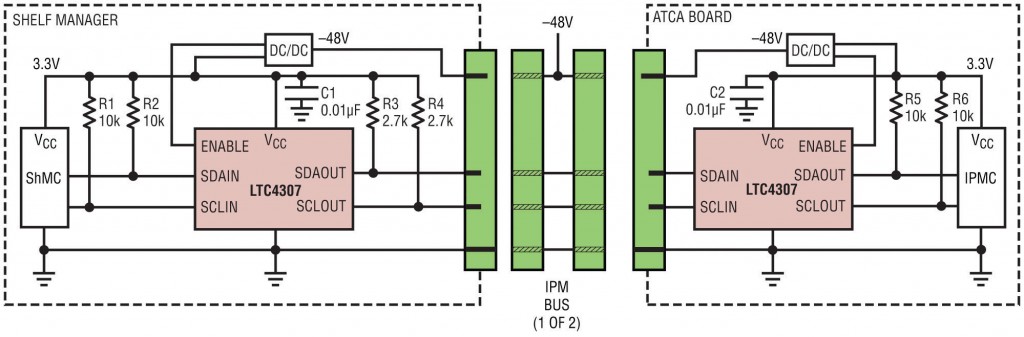

I motivi alla base del recente aumento della richiesta di questi buffer non sono solo quelli che originariamente hanno portato al loro sviluppo. I buffer per i bus sono stati utilizzati per la traslazione dei livelli e come buffer capacitivi dei segnali SDA e SLC I²C sin dalla pubblicazione della specifica PICMG 3.0 Revisione 2.0 (nota anche come AdvancedTCA) nel 2005. Gli utenti di sistemi AdvancedTCA avevano bisogno di un buffer per bus che risiedesse sul bordo di ciascuna scheda da inserire nel backplane passivo comune e che presentasse meno di 10pF di capacità al pin, consentendo di usare fino a 24 schede in un sistema e rimanendo sotto il limite di capacità di 690pF del backplane. Inoltre, gli IPMC dovevano assicurare che fosse presente un acceleratore del tempo di salita su entrambe le linee I²C per soddisfare la specifica di 900ns relativa al tempo di salita. Per quanto semplici possano sembrare questi requisiti, anche i bus seriali più semplici diventano più complessi, richiedendo agli IPMC di misurare parametri come la temperatura o la tensione, leggere informazioni vitali sul prodotto dalle schede individuali e apportare modifiche al sistema, aumentando prestazioni richieste ai buffer per bus.

Figura 2 – Applicazione AdvancedTCA IPMB semplificata

Le applicazioni AdvancedTCA non fanno eccezione per quanto riguarda la tendenza dei sistemi di trasmissione dati a un continuo aumento della complessità parallelamente a una riduzione del consumo di potenza. Ne consegue che agli IPMC viene richiesta una gestione migliore delle interfacce IPMB e delle corrispondenti schede AdvancedTCA. Le applicazioni attuali richiedono una migliore possibilità di collegamento in serie dei buffer per bus presenti su più schede installate insieme alla IPMB nonché supporto per schede a bassa tensione, senza andare a scapito dell’affidabilità a livello di scheda e di sistema. Esiste ora l’opportunità di creare una nuova soluzione basata sull’originale, ma ancora apprezzato, LTC4300A che è stato utilizzato nella PICMG 3.0. Rev 2.0 e di sfruttare nuovi buffer per bus come l’LTC4307, in grado di rispondere alle crescenti esigenze dei sistemi AdvancedTCA di domani.

Un basso offset rende possibile il collegamento in serie

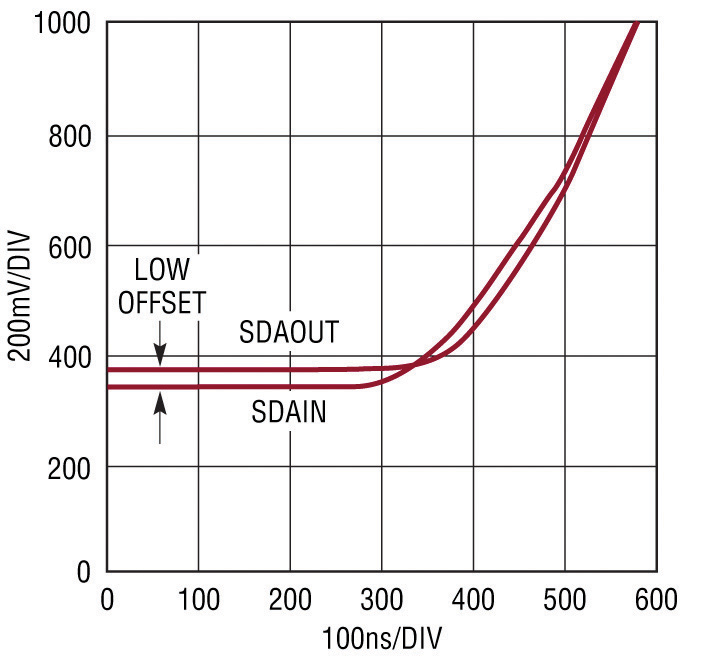

Le tensioni di offset (Vos) sono un problema inevitabile in molti tipi di dispositivi e, in questo caso, sono sempre presenti nei buffer delle linee I²C consentono la naturale modalità bidirezionale di funzionamento dei buffer e aiutano a identificare la direzione di trasmissione dei dati sui pin SDA e SCL. Ancora più importante, questi offset garantiscono che il latching non si verifichi sul bus. La specifica PICMG 3.0. Rev 2.0 richiede che gli IPMC pilotino una determinata frazione della massima tensione logica di basso livello all’uscita (VOL) sui backplane, e i buffer per bus devono funzionare secondo la loro tensione logica di basso livello all’ingresso (VIL). La tensione di offset di basso livello del buffer per bus diventa quindi importante quando il collegamento in serie dei buffer richiede che una tensione di uscita di basso livello a monte, sommata alla tensione di offset, sia minore della tensione d’ingresso di basso livello consentita del buffer successivo o dell’IPMC di ricezione. Per esempio, nel caso di un IPMC che comunichi con un altro IPMC attraverso tre buffer, il progettista deve far sì che VOL(n) < VIL(n+1), dove VOL(0) = VOL dell’IPMC principale, e VOL(n) = VOL(n-1) + VOS(n-1). Buffer di questo tipo collegati in serie con tensioni di basso livello ingresso-offset consentiranno quindi l’espansione di interfacce IPMB con più dispositivi periferici e linee di bus più lunghe.

I progettisti di sistemi AdvancedTCA sanno che i circuiti integrati degli IPMC pilotano tensioni logiche di basso livello molto più piccole di quelle effettivamente specificate nelle schede dati. Sfortunatamente, è prassi comune fra i produttori di CPU di limitarsi a copiare la tabella dei valori elettrici della specifica relativa alla linea I²C nelle schede dati per mostrare facilmente la conformità. Ne consegue che alcuni progettisti mettono in dubbio la possibilità di collegare in serie dei buffer per bus, per timore di violare la soglia VIL dei buffer, specialmente verso l’estremità di ricezione della catena del segnale, solo per scoprire, con sorpresa, che in qualche modo sono stati in grado di attuare il collegamento in serie senza alcun problema. Questo perché i circuiti integrati degli IPMC pilotano realisticamente le tensioni logiche di basso livello a valori ridottissimi, fino a 50mV. Ad esempio, un tale valore di 50mV combinato con un offset del buffer per bus pari a 60mV (un valore tipico) presente nell’LTC4307, genera una tensione logica di basso livello in uscita pari a 110mV che deve essere accettata dal buffer successivo. La tensione di offset è piccola quanto basta affinché, con l’ingresso logico di basso livello di 480mV dell’LTC4307, il progettista sia in grado di collegare in serie fino a sette buffer se necessario, un’operazione che sarebbe più difficile utilizzando generazioni più vecchie di buffer per bus con tensioni logiche d’ingresso di livello più basso e tensioni di offset più alte.

Figura 3 – Transizione del fronte di salita che mostra la tensione di offset ingresso-uscita di basso livello

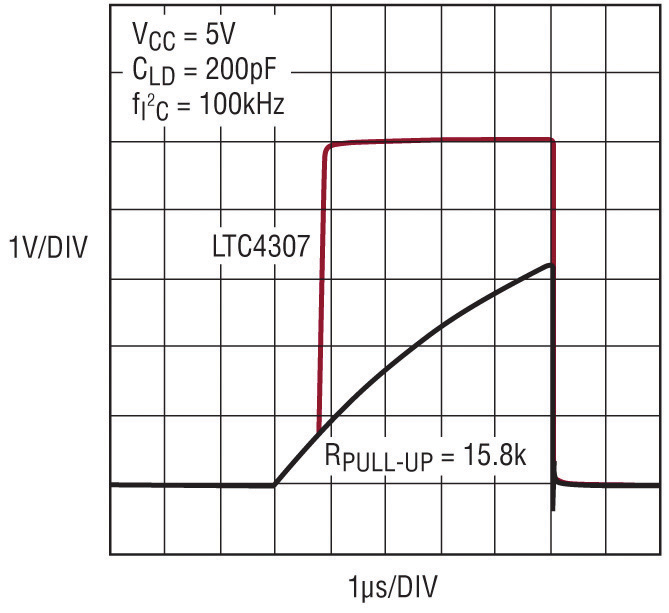

L’accelerazione del tempo di salita fa fronte ai tempi di salita dell’interfaccia IPMB

Le linee del bus I²C rimangono inattive a livello alto, tramite resistori di pull-up collegati alla tensione di alimentazione, mentre gli IPMC e altri controller sulla IPMB trasmettono portando le linee a livello basso. La specifica PICMG 3.0 Rev 2.0 stabilisce che sia i segnali SCL che quelli SDA aumentino monotonamente da 1V a 2,3V in 900ns con un resistore di pull-up da 2,7kΩ a 3,3V e un carico di 690pF. Questa operazione richiede l’uso di circuiti attivi per accelerare i tempi di salita ed è in questo caso che risultano utili i generatori di corrente aggiuntivi forniti dagli acceleratori del tempo di salita (RTA, rise time accelerator).

Gli RTA incorporati nell’LTC4307 offrono elevate correnti di pull-up con slew rate limitato affinché i requisiti sul tempo di salita siano soddisfatti. Dopo le condizioni iniziali sul fronte di salita, gli acceleratori si inseriscono automaticamente durante le transizioni positive del bus e ne fanno aumentare le tensioni a una velocità di 100V/µs su tutti e quattro i pin SDA e SCL. Ciò aumenta notevolmente l’affidabilità sia della scheda che del sistema in vari modi. Anzitutto, gli acceleratori assicurano transizioni regolari, controllate durante i fronti di salita; i sistemi AdvancedTCA diventano quindi molto meno sensibili al rumore sui fronti di salita poiché i circuiti di pull-up degli acceleratori presentano impedenze notevolmente inferiori a quelle dei resistori di pull-up del bus. In secondo luogo, gli acceleratori permettono di usare resistenze di pull-up del bus maggiori, il che riduce il consumo di potenza e migliora il margine di rumore del livello logico basso. Per sistemi con carico leggero, in cui alti valori dello slew rate possono causare riflessioni di linea di trasmissione sul bus, l’LTC4307 regola la corrente di pull-up riducendola quando i fronti di salita aumentano a velocità maggiori di 1V/10ns. Gli RTA si disinseriscono automaticamente quando i livelli logici rimangono alti, sui fronti di discesa e durante la generazione automatica del segnale di clock o del bit di stop.

Gli acceleratori del tempo di salita sono disponibili sia in forma discreta, separati che integrati con i corrispettivi buffer per bus. Questa seconda soluzione è più comoda poiché la rilevazione e le regolazioni dello slew rate vengono eseguite a entrambi i capi del buffer. Non avrebbe importanza a quali IPMC sul bus è affidato il compito di soddisfare i requisiti sul tempo di salita, poiché i buffer inseriti nelle varie sezioni della IPMB assicurerebbero l’accelerazione a tutti i bus intermedi anziché a ciascun nodo individualmente quando si utilizzano soluzioni discrete.

Figura 4 – Confronto tra acceleratori del tempo di salita e resistori di pull-up per forme d’onda I²C

È consigliabile ricorrere agli RTA nella maggior parte dei casi eccetto nei sistemi che utilizzano resistori di pull-up a bassissima resistenza o che presentano bassa capacità del bus, poiché in queste condizioni, quando si inseriscono per errore gli acceleratori possono trasformare piccole perturbazioni di rumore in picchi sulle linee di alimentazione. In applicazioni in cui non si utilizza alcuna accelerazione del tempo di salita, sono necessari resistori di pull-up a bassa resistenza per assicurare che i requisiti sul tempo di salita siano soddisfatti. Tuttavia, non è facile attuare questa condizione, specialmente in sistemi a tensione inferiore in cui resistori di pull-up a resistenza più bassa corrispondono a cadute di tensione inferiori ai capi dei resistori, riducendo quindi il margine della tensione logica di uscita a basso livello. Inoltre, gli IPMC hanno bisogno di assorbire 1,2mA a massa mentre mantengono la massima tensione logica di uscita a basso livello necessaria per pilotare i segnali I²C. Ossia, sebbene alcuni buffer per bus non offrano accelerazione del tempo di salita e possano vantare conformità alle specifiche AdvancedTCA, purtroppo tale conformità non sempre comporta una IPMB funzionale in sistemi sia di grandi che di piccole dimensioni. Quindi, è raccomandabile usare buffer per bus con accelerazione del tempo di salita che possano sia garantire la conformità che ridurre ulteriormente il numero di componenti, il grado di complessità e il costo, specialmente in sistemi a bassa tensione con carico notevole.

Affidabile hot-swapping degli IPMC

I controller di bus devono presentare uno stato di alta impedenza all’interfaccia IPMB quando vengono spenti e accesi, un requisito creato specificamente tenendo presente l’hot-swapping. L’LTC4307 ottiene questo risultato grazie alla sua bassa capacità d’ingresso, minore di 10 pF, riducendo al minimo i disturbi sul bus durante le operazioni di hot-swapping. L’LTC4307 è dotato anche di circuito di protezione contro la scarica elettrostatica a +/-5kV basato su un modello del corpo umano. Poiché i buffer per bus normalmente sono inseriti davanti al percorso del segnale I²C di una scheda AdvancedTCA, strutture robuste contro la scarica elettrostatica possono contribuire a ridurre i danni causati a un IPMC durante operazioni di hot-swapping. inoltre, all’avvio l’LTC4307 monitora sia la IPMB che il bus lato scheda per rilevare una condizione di inattività o di presenza del bit di stop prima che si inserisca il circuito di connessione ingresso-uscita, prevenendo qualsiasi disturbo alle altre schede AdvancedTCA sul bus. Inoltre, una precarica di 1V su tutte le linee SDA e SCL riduce al minimo il differenziale di tensione del caso peggiore applicato a questi pin quando la scheda viene inserita a caldo nella IPMB in funzione.

La rilevazione e il ripristino di bus bloccati promuovono l’affidabilità dei bus

Sfortunatamente, anche il funzionamento del bus I²C utilizzato dalle interfacce IPMB in sistemi AdvancedTCA ha difetti, tra cui il rischio di una situazione di bus “inceppato”. I dispositivi slave utilizzano il segnale di clock, SCL, per campionare i dati sul bus e saltuariamente perdono il sincronismo, mantenendo senza necessità la linea SDA in uno stato basso. I motivi potrebbero essere molteplici. La maggior parte del tempo, uno slave attende cicli di clock aggiuntivi avviati dal master e, per qualche ragione, non li riceve: un master malfunzionante potrebbe non trasmettere appropriatamente tutti i cicli di clock oppure un bit di start o di stop potrebbe essere stato distorto lungo un’interfaccia IPMB rumorosa; o forse è semplicemente lo slave a essere malfunzionante. Indipendentemente dal motivo, i casi di bus bloccati si verificano anche nelle condizioni e negli ambienti più improbabili. Se non si rimedia al problema, un dispositivo bloccato impedisce ad altri dispositivi sul bus di comunicare finché non si sblocca andando allo stato alto. Quindi, è nel migliore interesse del progettista della scheda assicurare una trasmissione dati funzionale sull’interfaccia IPMB mediante qualche tecnica di rilevazione e ripristino di bus bloccati.

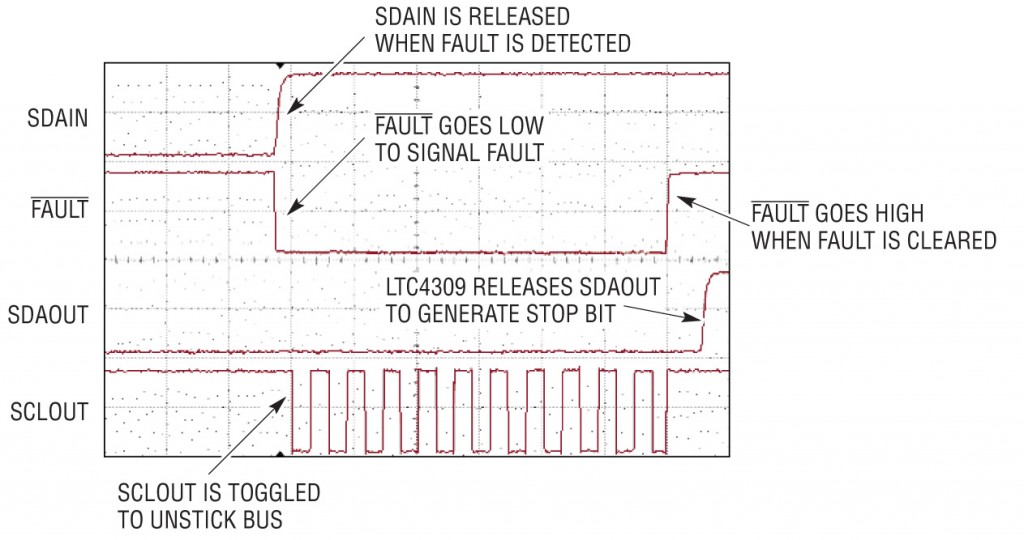

Buffer per bus come l’LTC4307 sono dotati di appositi circuiti per risolvere questo problema: le uscite di entrambi i pin SDA e SCL vengono monitorate indipendentemente per rilevare una condizione di bus bloccato e se viene rilevato uno stato basso, si avvia un timer interno di 30ms, che si azzera solo se il bus ritorna allo stato alto entro il tempo specificato; in caso contrario, le connessioni ingresso-uscita per entrambi i segnali I²C vengono interrotte, prevenendo ulteriori comunicazioni con il dispositivo bloccato, mentre il buffer genera fino a 16 impulsi di clock a 8,5kHz su SCLOUT nel tentativo di sbloccare il bus lato scheda. Se il bus si sblocca o se i 16 impulsi di clock vengono completati, viene generato un bit di stop per cancellare il bus ai fini di ulteriori comunicazioni e le connessioni I²C ingresso-uscita vengono ripristinate. L’LTC4307 è dotato di un pin ENABLE che può comandare la riconnessione del bus dopo una condizione di guasto; ciò potrebbe essere utile nel caso di tentativo manuale, con il master, di sbloccaggio del bus. Per i progettisti di schede che desiderano più controllo sui bus bloccati, buffer più avanzati come l’LTC4309 sono dotati di un pin FAULT per indicare quando è stato rilevato un bus bloccato, oltre a un pin DISCEN per disabilitare completamente la funzione di disconnessione ingresso-uscita del circuito di ripristino del bus bloccato.

Figura 5 – Il circuito di ripristino del bus bloccato presente nell’LTC4309 disconnette bus bloccati e utilizza un clock automatico per eseguire il ripristino (LTC4307 senza pin FAULT)

Conclusione

L’LTC4307 è solo uno dei vari dispositivi proposti da Linear Technology a dimostrare che, sebbene i requisiti PICMG 3.0 possano essere soddisfatti dal popolare LTC4300A, i progettisti dovrebbero approfittare dei vantaggi che nuovi buffer per bus oggi assicurano ai sistemi AdvancedTCA. Oltre a dividere un bus di grandi dimensioni, altrimenti non gestibile, in numerosi bus che possono essere gestiti, l’LTC4307 agevola la progettazione del collegamento in serie di più buffer di questo tipo, al tempo stesso offrendo la vitale accelerazione del tempo di salita, necessaria per garantire che i sistemi a bassa tensione siano a norma PICMG 3.0. Inoltre, una miriade di altre funzionalità – come il ripristino di bus bloccati, la protezione contro la scarica elettrostatica e la precarica delle linee I²C – consente ai progettisti di tenere conto di imprevisti malfunzionamenti temporanei del sistema e di promuovere il funzionamento ininterrotto. Tirando le somme: i buffer per bus possono essere acquistati semplicemente per l’isolamento capacitivo che offrono, ma i progettisti di sistemi AdvancedTCA ora sono più sicuri che tali buffer aiuteranno significativamente l’IPMC corrispondente nella gestione di un’interfaccia IPMB funzionale.

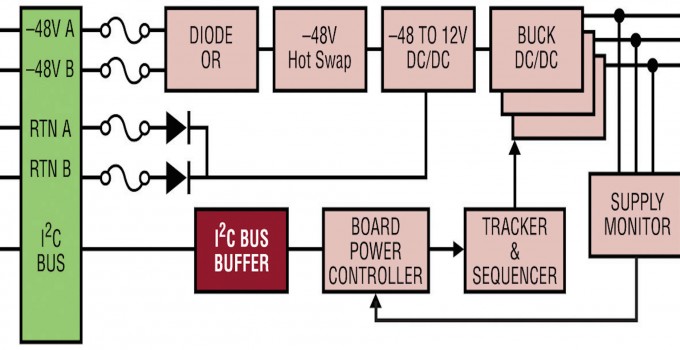

L'immagine principale rappresenta uno schema a blocchi della catena del segnale e della corrente di alimentazione di un sistema AdvancedTCA.

La definizione che abbiamo dato in precedenti commenti, e che è stata confermata anche da altri progettisti elettronici, è che Linear Technlogy è la Ferrari dei semiconduttori. Non credo sia un caso che abbia tralasciato il mercato dei microcontroller per dedicarsi al condizionamento di segnale. Una sola cosa ma fatta bene!

Questo articolo dimostra che lo è anche nella gestione del bus I2C.