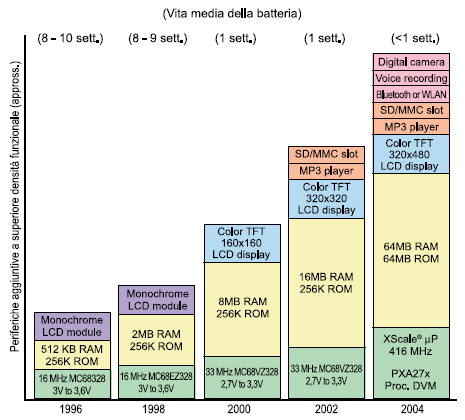

Le innovazioni portate ai progetti dei sistemi elettronici hanno visto una crescita esponenziale per l’alta integrazione dei core dei processori delle ultime generazioni di PDA, telefoni intelligenti e cellulari. Dal punto di vista della progettazione di sistema, l’aumento del numero di funzioni aggiunte è quasi raddoppiato ogni due anni inseguendo il vorace appetito di funzioni innovative da parte dei consumatori con una sempre più richiesta di bassi consumi. In questo articolo vedremo una rassegna di utili considerazioni sulla progettazione dei sistemi di alimentazione: dalla scelta della batteria di backup, alla scelta tra regolatori lineari e DC-DC converter.

Introduzione

In accordo alla teoria originale di Moore il costo totale per rendere funzionale un particolare sistema deve essere minimizzato. Per rispondere a questa sfida di progetto, mantenendo i costi, lo sforzo dei progettisti viene ammortizzato ‘ri-utilizzando’ i progetti esistenti costruendovi sopra nuove funzioni o aggiungendone. Oggi le soluzioni SoC (System-on-a-Chip) pesano enormemente sulla ricerca delle risposte a queste sfide. Funzionalità aggiuntive come i display LCD a colori con retro-illuminazione, sottosistemi audio, funzioni di fotocamera, comunicazioni su WLANs, Bluetooth®, ed altre funzioni RF/analogiche integrate per le applicazioni di fascia alta, hanno tutte portato al limite i requisiti del punto di vista energetico. In figura 1 viene mostrato il percorso evolutivo della crescita del numero di funzioni e delle aspettative di vita della batteria.

LE CLASSICHE MODALITÀ ‘POWER-SAVING’

Le modalità di risparmio-energetico erano solitamente pre-programmate all’interno del processore e comprendevano livelli quali burst, sleep e stand-by. Per il profilo di un PDA il sistema può processare una funzione richiesta dall’utente (come un input sullo schermo tattile) e quindi entrare in modalità stand-by fino al successivo input dal touch-screen. Durante il periodo di stand-by solo lo schermo LCD rimane attivo mentre il processore è programmato per ‘fare un sonnellino’ da cui viene risvegliato per mezzo di un interrupt. Nella modalità burst, in applicazioni di ‘data polling’, la più alta frequenza operativa del processore (il caso peggiore per il consumo di energia) può essere similmente abbassata riducendo il duty-cycle della CPU. Allo stesso modo la modalità burst può essere disabilitata durante un interrupt. Quando la batteria raggiunge il livello critico inferiore e viene spenta, il processore può essere programmato per entrare in modalità sleep durante la quale tutte le funzionalità, ad esclusione dell’RTC (real-time clock), sono in uno stato di inattività. Per mantenere correttamente la data svolgere le funzioni legate allo scorrere del tempo l’RTC consuma meno di 1 µA. Quindi il risparmio energetico viene svolto unicamente dal codice firmware del processore.

CONSIDERAZIONI DI PROGETTO PER CONSERVARE L’ENERGIA

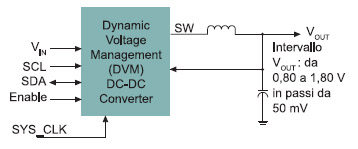

Mentre i processori applicativi sono stati la panacea per le soluzioni SoC, le considerazioni per valutare i progetti ‘a basso consumo’ fanno oggi riferimento alle prestazioni misurate in milliwatt per Megahertz (mW/MHz). Alcuni di questi processori applicativi possono avere un minimo di 0,08 mW/MHz e arrivare fino a 0,42 mW/MHz. Per supportare ulteriori caratteristiche di risparmio energetico si possono prevedere display LCD intelligenti che abbiano una memoria interna per mantenere l’immagine ed un controllore indipendente che possa far risparmiare cicli di CPU scaricandola del rinfresco dell’immagine sul display. Altri sistemi vengono realizzati con processi di produzione a 0,13 micron, riducendo quindi la potenza agli I/O e abbassando nel contempo la tensione al core e controllando le correnti di dispersione. Altre tecniche comprendono la riduzione del duty-cycle della CPU e la frequenza per mezzo del software di gestione della potenza. L’architettura PXA27x XScale di Intel basato sul core ARM è un esempio dell’impiego di queste tecniche che scala ‘al volo’ e direttamente sia la tensione che la frequenza con un passaggio intelligente a diversi livelli di modalità ‘a basso consumo’ pur mantenendo le necessarie prestazioni applicative. Con le sue sei modalità operative-normal, idle, deep idle, standby, sleep e deep sleep – il PXA27x consente risparmi energetici significativi. Implementando diversi domini energetici separati, che possono essere accesi o spenti in modo indipendente, l’architettura del PXA27x richiede fino a 10 domini energetici. Riducendo la tensione di ingresso al core e la frequenza operativa, il processore può arrivare a ridurre i consumi fino ad almeno due volte. Normalmente i processori hanno una dissipazione di potenza che è proporzionale al quadrato della tensione di ingresso al core e la relativa frequenza. Mentre la soluzione del PXA27x ha dei meriti relativamente al risparmio energetico, le soluzioni offerte dagli IC di gestione della potenza (PMIC – Power Management IC) sono gravate da una lunga lista di livelli di tensioni di alimentazione da soddisfare: 1,1V, 1,3V, 1,8V, 2,5V e 3,3V. Per alimentare il core e per supportare la scalabilità dinamica della tensione il PMIC richiede in aggiunta una uscita di tensione programmabile che possa andare da 0,85V a 1,55V. L’intervallo programmabile deve avere passi del valore da 50 mV a 100 mV (vedi Figura 2).

Figura 2. Gestione intelligente della potenza per pilotare la tensione del core di processori applicativi

Con un comune bus I2C verso i registri programmabili il PMIC semplifica l’interfaccia verso la maggior parte dei processori.

SCEGLIERE LA BATTERIA RICARICABILE DI BACKUP

Le popolari batterie agli ioni di Litio (Li-Ion) a singola cella portano un valore nominale di 3,6V ed un intervallo effettivo da 2,7V ai 4,2V a piena carica. Altri tipi di batteria, che sono usati nei progetti di sistemi portatili, comprendono le batterie ai polimeri di Litio (Li-Pol), quelle a bottone al biossido di Litio-Manganese (Li-MnO2) e le batterie al Nickel-Idruro metallico (Ni-MH). Le batterie agli ioni di Litio offrono il miglior rapporto di densità energetica per unità di peso ma richiedono normalmente qualche forma di circuito di protezione legato alla loro volatilità. Le batterie Li-Pol hanno profili geometrici sottili e non pongono problemi di infiammabilità. Telefoni intelligenti e cellulari hanno una maggiore flessibilità di design meccanico per utilizzare le batterie ad alta densità che non le sottili dimensioni di un PDA.

LA SCELTA DEI DISPOSITIVI PER LA GESTIONE DELLA POTENZA

Dopo aver valutato la lista dei requisiti richiesti alla potenza, vediamo due tipi principali di topologie:

- Regolatori LDO (Low-dropout) programmabili per i carichi digitali e analogici e un LDO fisso per la tensione della batteria di backup;

- Regolatroi DC-DC switching programmabili sia per i carichi più elevati che per quelli più leggeri.

Nel caso di uscite multiple con bassi livelli di tensione di ingresso e basse correnti di uscita, la scelta migliore è integrare diversi LDO in un chip singolo usando la tecnologia CMOS. Gli LDO dovrebbero tipicamente supportare 100 mV di caduta di tensione. Per pilotare la circuiteria RF l’LDO dovrebbe essere anche in grado di supportare un basso livello di rumore di uscita come 100 µVRMS per una data banda passante. Ci dovrebbe anche essere una funzione di abilitazione/disabilitazione (enable/disabile) per ogni LDO. Quando l’LDO è disabilitato la corrente di quiescenza dovrebbe stare nei valori di pochi µA al fine di estendere la vita della batteria. La scelta di un regolatore switching DC-DC a configurazione buck, con alta efficienza e capacità di pilotare alte correnti, fornisce l’approccio più equilibrato per alimentare sistemi portatili. Per minimizzare gli assorbimenti e massimizzare la vita della batteria, è utile scegliere dispositivi PMIC che supportino efficienze di circa il 90% o superiori. Per ottenere questo il dispositivo PMIC deve minimizzare le perdite di commutazione per mezzo di rettificatori sincroni. Questo è fattibile utilizzando i MOSFET interni anziché impiegando i più convenzionali ma meno efficienti diodi Schottky. Il dispositivo MOSFET ha una propria caduta di tensione diretta elevata, dovuta al diodo interno, ma utilizzando un diodo Schottky in parallelo si riducono le perdite per la caduta diretta. Naturalmente nelle applicazioni portatili è stan dard avere il MOSFET integrato nel PMIC. Il regolatore switching di tipo buck richiede di conservare sull’uscita la sua capacità di pilotaggio in corrente gestendo il suo duty-cycle. Quando il regolatore switching pilota carichi elevati può utilizzare una modalità PWM ad una frequenza fissa. Ma quando il carico si fa più leggero il regolatore può commutare ad una frequenza inferiore usando configurazioni PFM (Pulse Frequency Modulation) o modalità di ‘pulse skip-ping’ (omissione di impulsi). Il regolatore buck dovrebbe essere in grado di operare ad un duty cycle del 100% per supportare un controllo della tensione di uscita con bassa caduta anche quando la tensione di ingresso scende al suo valore minimo possibile. Come nello scenario LDO i regolatori switching buck necessitano della funzione enable/disable. Un’altra funzione critica è il carica-batteria con a bordo il monitoraggio della stessa e la commutazione automatica tra la batteria di backup e l’LDO che alimenta il VCC-BATT. Fortunatamente sono disponibili soluzioni di gestione della potenza che soddisfano la maggior parte delle funzioni sopra descritte. Le più recenti proposte del mercato offrono soluzioni del tipo SoC per la potenza (per esempio l’LP3970) comparate a soluzioni precedenti che richiedevano più PMIC e non supportavano una gestione dinamica della tensione.

ESIGENZE AGGIUNTIVE NEL PROGETTO DI SISTEMI DI POTENZA

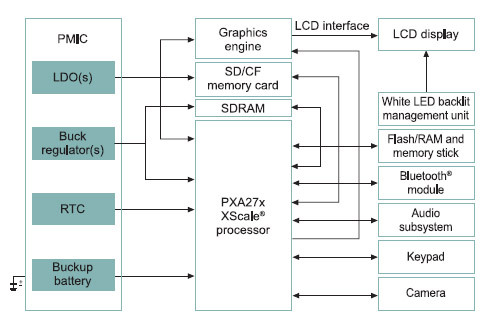

I processori normalmente supportano altre periferiche esterne come SRAM, Bluetooth, WLAN/802.11x, interfacce per fotocamere, memorie stick, interfacce USB, elaboratori grafici esterni, display LCD con retro-illuminazione (come mostrato in Figura 3).

Figura 3. Considerazioni di progetto per la potenza di un processore e delle relative periferiche di sistema

Organizzando le necessità addizionali per la parte di alimentazione di queste periferiche, il progettista può allora eseguire una scelta intelligente circa la possibilità o meno che il regolatore DC-DC switching o l’LDO debbano alimentare anche le funzionalità aggiuntive.

Con l’avvento dell’IoT e del Wearable la progettazione a basso consumo è diventata essenziale per la vita di un dispositivo elettronico. Facilitata soprattutto dalla crescita in termini di efficienza energetica della microelettronica.