All'interno della Rubrica Firmware Reload potrete trovare una infinità di articoli tecnici appartenenti alla passata rivista cartacea Firmware, con temi di interesse per makers e professionisti. Ecco una nuova mini serie di articoli di questa rubrica. Per farsi un’idea delle prestazioni di massima del sottosistema di alimentazione dei propri circuiti stampati non si deve necessariamente spendere una fortuna. Bisogna però mettere in conto alcune limitazioni e problemi.

Richiamiamo brevemente la problematica Power Integrity, rimandando il lettore interessato ad approfondire alla serie di articoli richiamata in Riferimento 1 ed alla biografia ivi citata, presenti nella Puntata successiva. Le richieste relative alle prestazioni del sistema di alimentazione di una moderna applicazione digitale o mista analogico/digitale (Power Distribution Network, PDN nel seguito) si sono fatte più stringenti che in passato. A questo concorrono principalmente le caratteristiche dei circuiti integrati moderni, ma anche esigenze di affidabilità e costo. Le conseguenze di eccessive fluttuazioni nelle tensioni di alimentazione locali ad un circuito integrato, particolarmente CMOS, sono molteplici. Possiamo citare la generazione e propagazione di rumore elettrico nel sistema, le violazioni delle temporizzazioni, incertezze nelle commutazioni (jitter), rischio di emissioni elettromagnetiche abbastanza elevate da far fallire le prove di compatibilità (ed impedire l’ottenimento delle certificazioni indispensabili alla commercializzazione del prodotto), ed infine la riduzione dell’affidabilità, nel tempo, del prodotto stesso. Osserviamo di conseguenza la crescita dell’importanza delle tecniche di Power Integrity e la loro applicazione in ambiti sempre più ampi. Naturalmente, le applicazioni embedded a singolo microcontrollore avranno esigenze ben diverse da quelle di una scheda madre di un server per applicazioni di rete. Le tecniche e gli strumenti disponibili vanno quindi dosati e proporzionati adeguatamente alla fascia di complessità, al costo sostenibile ed al livello di affidabilità desiderato. La cassetta degli attrezzi Power Integrity comprende sostanzialmente il regolatore di tensione, la distribuzione di massa, l'alimentazione sul circuito stampato ed i condensatori di disaccoppiamento e filtraggio. Nulla di nuovo, si potrebbe dire. In realtà, il primo elemento caratterizzante il paradigma Power Integrity sta nel considerare tutti questi componenti insieme, con i loro effetti del secondo ordine quali le antirisonanze, cooperanti a costituire un sistema, la PDN appunto. In particolare, viene sottolineata la necessità di pensare il PCB come un componente avente funzioni fondamentali nel garantire la qualità di segnali ed alimentazioni, piuttosto che come ad un mero supporto alle connessioni tra i componenti attivi e passivi della scheda. Avere una alimentazione stabile di elevata qualità, poco rumorosa e capace di erogare picchi di corrente quando richiesto, senza uscire dai limiti di specifica, non è certo una esigenza nuova.

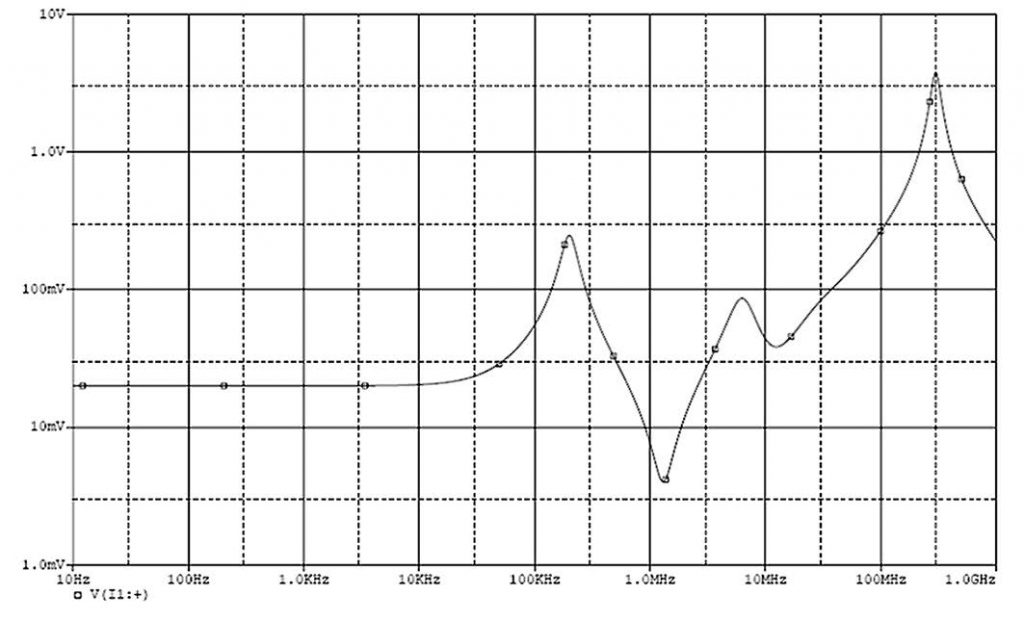

Questo è da sempre il primo requisito di ogni progetto elettronico, si tratti di un circuito integrato, una scheda o un sistema. Le caratteristiche dei circuiti logici apparsi negli ultimi anni rendono però qualità e prestazioni del sistema di alimentazione particolarmente critici e bisognosi di un’attenta progettazione. Le tensioni di alimentazione sono andate gradualmente riducendosi per limitare la potenza dissipata e rispettare le caratteristiche elettriche di strutture integrate sempre più piccole. Siamo quindi passati in pochi anni dai classici 5 V ad 1,2 V ed ormai anche a tensioni inferiori al Volt. Le tolleranze ammesse sono spesso passate dal tradizionale +/- 10 % a +/- 5 %, parallelamente con un sensibile aumento delle correnti assorbite e delle frequenze di commutazione, quindi della banda passante richiesta al sistema di alimentazione. Il margine di tensione si è così ridotto da 500 mV a 50 mV. La maggiore criticità del margine disponibile impone tecniche di progettazione e verifica prima della costruzione dei prototipi più attente e sofisticate che in passato, in particolare, coinvolgendo programmi di simulazione (CAD). Tali verifiche richiedono l’uso di programmi sofisticati e costosi, come indicato nell’articolo in riferimento 1. Molte piccole e medie aziende hanno difficoltà ad avere accesso a tali programmi, la cui disponibilità è spesso limitata anche in grandi aziende. Pur in presenza di varie forme di flessibilità da parte dei fornitori di CAD, il progettista hardware difficilmente ha modo di usare simulazioni della propria PDN. Certamente senza pretendere lo stesso livello di precisione ed accuratezza, l’uso di alcuni programmi freeware può consentire una serie di analisi “what if” utili quanto meno ad uno sgrossamento della problematica di progettazione e di confronto tra soluzioni diverse. Tipicamente c’è un prezzo “non monetario” da pagare, consistente nella limitazione dello stesso strumento a disposizione, in termini di dimensioni del progetto analizzabile, nella performance di simulazione, nel tempo necessario alla predisposizione dell’ambiente di simulazione stesso e nel rischio di introdurre errori dovuti all’intervento manuale, dove invece gli strumenti commerciali lavorano in modo automatico. Abbiamo già dettagliatamente descritto in un articolo precedente uno di questi programmi, il PDN_Tool di ALTERA, vedi riferimento 2. Il PDN_Tool consente di ridimensionare la rete di condensatori di filtro ed analizzarne il comportamento in frequenza. Richiamiamo brevemente l’attenzione sulla risposta in frequenza di una rete capacitiva, un esempio semplificato è visibile in Figura 1.

Figura 1: Comportamento in frequenza di una rete di disaccoppiamento con regolatore di tensione (semplificata)

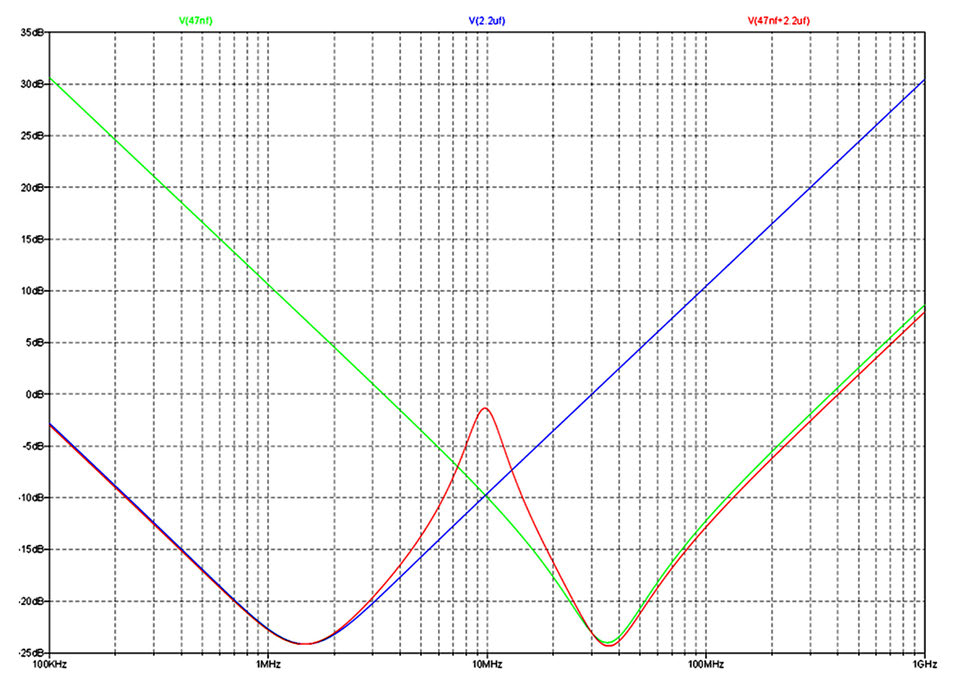

In pratica, si determina un picco di impedenza dovuto a risonanze parallele (anti risonanza), ad ogni passaggio da un comportamento positivo ad un comportamento induttivo, corrispondente all’incrocio delle differenti risposte in frequenza degli elementi costitutivi della rete in esame. La Figura 2 illustra graficamente tale fenomeno.

Figura 2: Impedenza totale (rosso) risultante dal parallelo di un condensatore ceramico da 47 nF (verde) ed uno da 2,2 uF (blu)

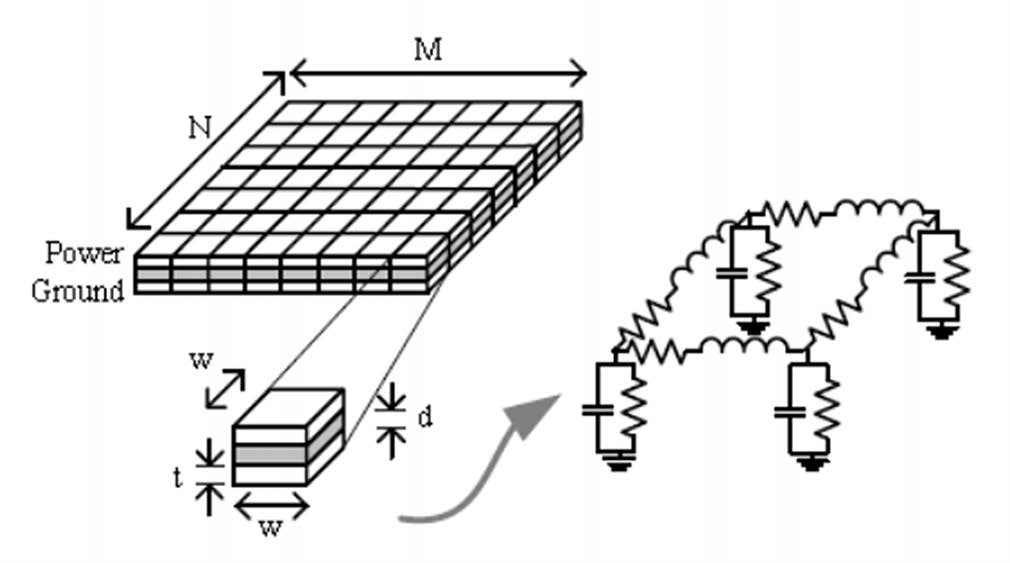

Il PDN_Tool consente di costruire tali curve di risposta ed ottimizzarne il comportamento, almeno a frequenze medie e basse, riducendo al minimo i picchi e mantenendo l’intero profilo al di sotto di un valore limite desiderato (“target impedance”). Il PDN_Tool è basato su un foglio di calcolo Excel; risultati analoghi sono ottenibili, con un pò di fatica aggiuntiva, attraverso i vari programmi SPICE, anche freeware, disponibili in rete, quali LT-SPICE. Un livello di sofisticazione superiore, sempre utilizzando tecnologie SPICE, si può ottenere discretizzando i piani di alimentazione e massa in un certo numero di celle elementari rappresentate da un circuito equivalente RLC (vedi Figura 3).

Figura 3: Discretizzazione PCB

Articolo pubblicato sulla rivista Firmware: Anno 2015 - Numero 109-110