In questo articolo metteremo a confronto alcune delle FPGA dei produttori più conosciuti, il tutto per capire quale, dal punto di vista energetico, garantisce un consumo di potenza inferiore.

Il problema del consumo di potenza per le logiche programmabili sta diventando sempre più importante, tanto che i maggiori produttori hanno creato dei prodotti dedicati a mantenere bassi i consumi. Nel seguito dell’articolo metteremo a confronto sei prodotti utilizzando i dati dichiarati dal datasheet, dai tool di previsione dei consumi e i dati ottenuti da rilevazioni sul campo. Il tutto per decidere quale FPGA è il prodotto leader nei bassi consumi.

CONTRIBUTI AL CONSUMO DI POTENZA

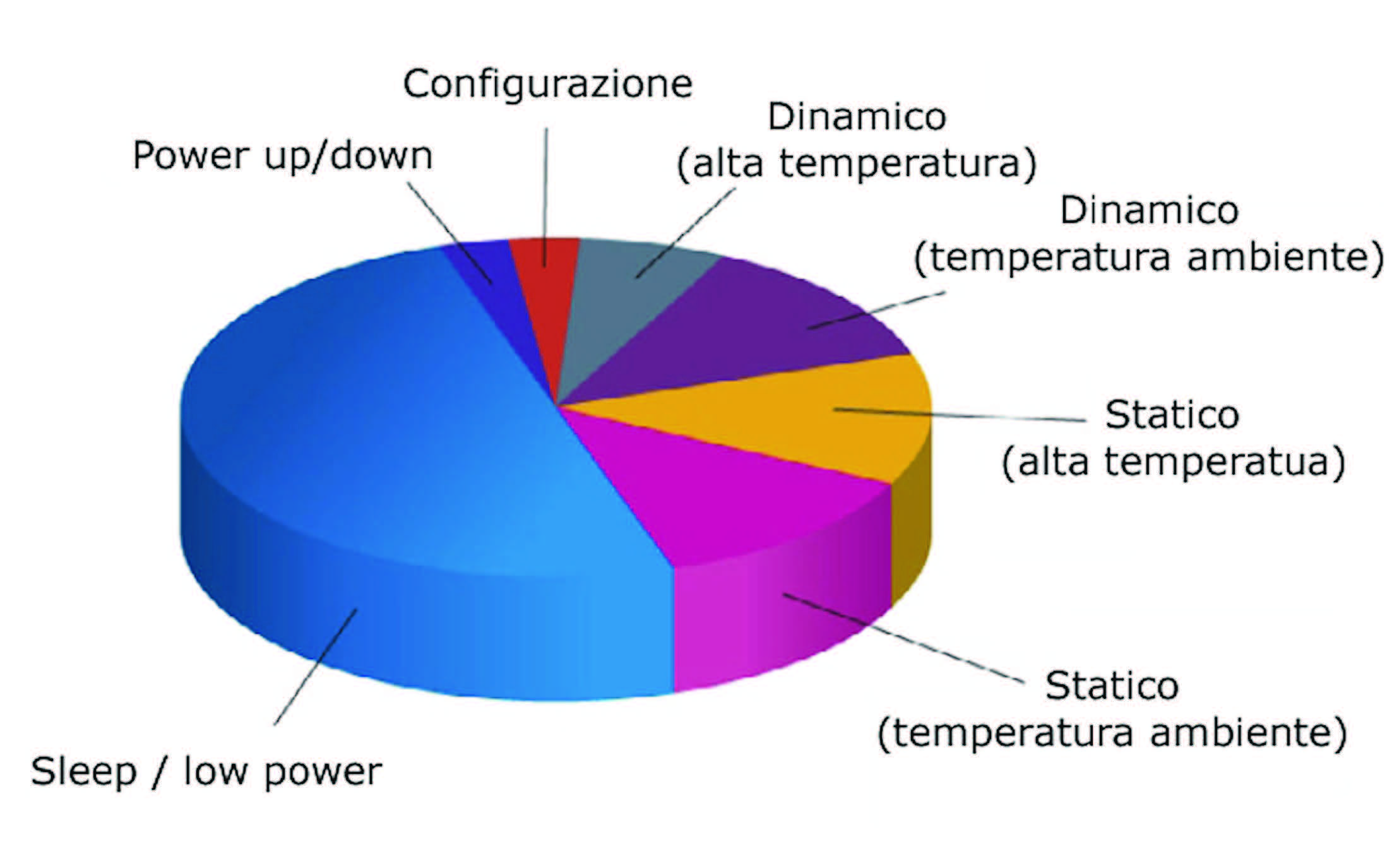

Ci sono essenzialmente cinque tipologie di consumi distinti che insieme concorrono a determinare il consumo complessivo di potenza di un dispositivo FPGA. Queste componenti di seguito elencate sono visibili in figura 1.

Figura 1: consumo di potenza, suddiviso per le sue componenti, nel tempo.

Le varie componenti del consumo di potenza sono:

# La potenza consumata al Power-up; detta anche potenza di inrush, è quella che consuma il dispositivo quando viene alimentato.

# La potenza consumata in configurazione; è la potenza richiesta durante il caricamento dell’FPGA, subito dopo il power-up. Ovviamente è una componente specifica per i dispositivi SRAM-based.

# La potenza statica; è la potenza consumata dall’FPGA dopo l’alimentazione e la configurazione, ma prima di diventare operativa (per esempio quando il clock non è ancora attivo).

# La potenza dinamica (o potenza attiva); è la quantità di potenza consumata dal dispositivo quando diventa operativo.

# La potenza di Sleep, (o potenza in risparmio energetico); alcuni dispositivi offrono modalità di basso consumo o di sleep, in molti casi questa potenza differisce da quella statica.

INTRODUZIONE AL CONFRONTO DEI CONSUMI

La potenza statica e la potenza dinamica sono state valutate considerando diversi dispositivi offerti da costruttori di logiche programmabili. Per applicazioni a batteria, il dispositivo rimane per un lungo periodo in attesa, per esempio è il caso di dispositivi portatili che quando non vengono utilizzati entrano in modalità statica. In questa fase il consumo di potenza statico incide nel bilancio complessivo dei consumi, la corrente assorbita dalla batteria in tale fase determina la vita del dipositivo (prima di dover essere ricaricato). Per questa ragione valutare la potenza statica è uno degli obbiettivi primari. La potenza dinamica è stata valutata per più frequenze operative per tutti i dispositivi in test. Per semplificare il confronto ci si focalizza solamente sulla potenza di core dell’FPGA, che determina il contributo principale al consumo di potenza per i dispositivi programmabili. Il contributo dato dagli I/O non è stato considerato, così come non sono stati analizzati i consumi derivanti dall’inrush e dalla configurazione. Le informazioni utili per il confronto sono tare prese da tre fonti:

# I datasheet dei costruttori.

# Dai tool di stima del consumo offerti dai costruttori.

# Attraverso una misurazione diretta su una scheda appositamente creata.

LA SCHEDA DI CONFRONTO

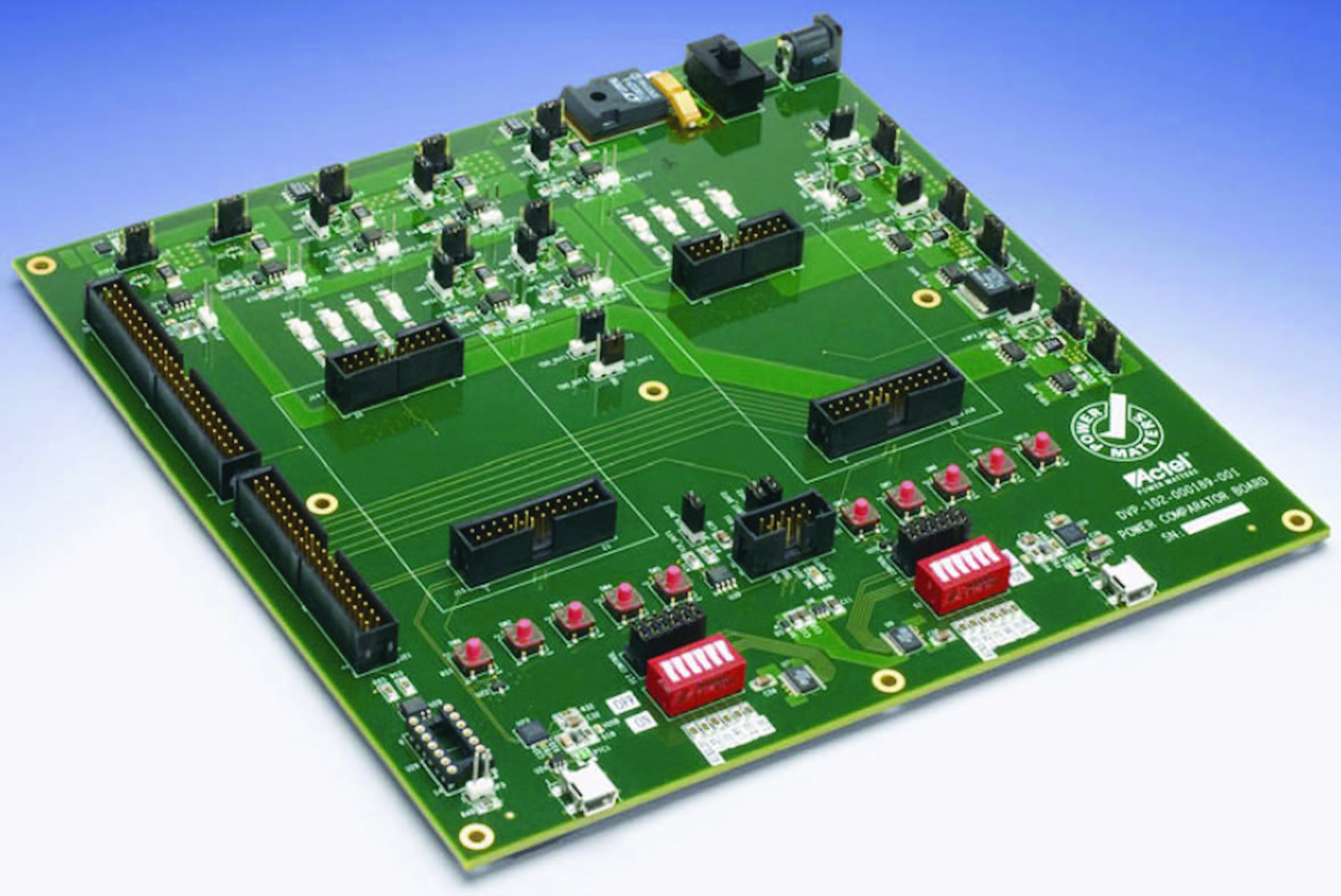

Per effettuare il confronto sui consumi non poteva essere utilizzata una scheda offerta dai produttori delle logiche programmabili, ogni scheda sarebbe stata diversa dalle altra, progettata con differenti configurazioni. Per valutare alla pari tutti i dispositivi era necessario utilizzare una scheda dedicata a questa attività. Il design della scheda consente di confrontare due dispositivi nelle medesime condizioni operative. La scheda è visibile in figura 2.

Figura 2: scheda di confronto.

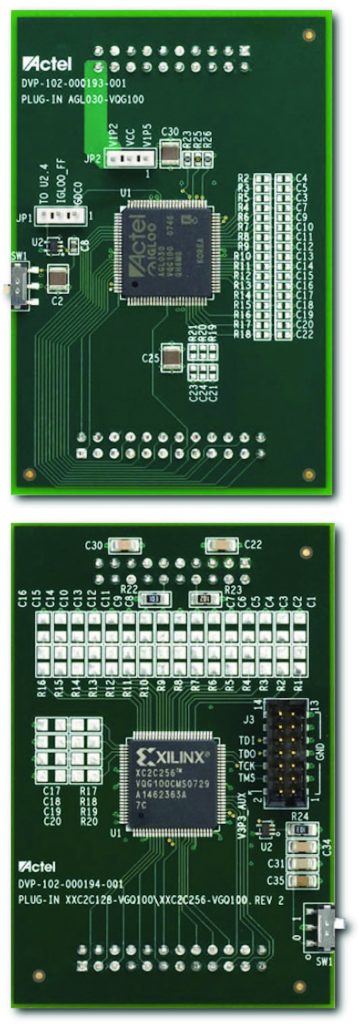

Sulla scheda sono disponibili due socket con una interfaccia semplicissima, in grado di ospitare due schede figlie che devono essere semplicemente inserite (figura 3).

Figura 3: schede figlie per due dei dispositivi sotto test.

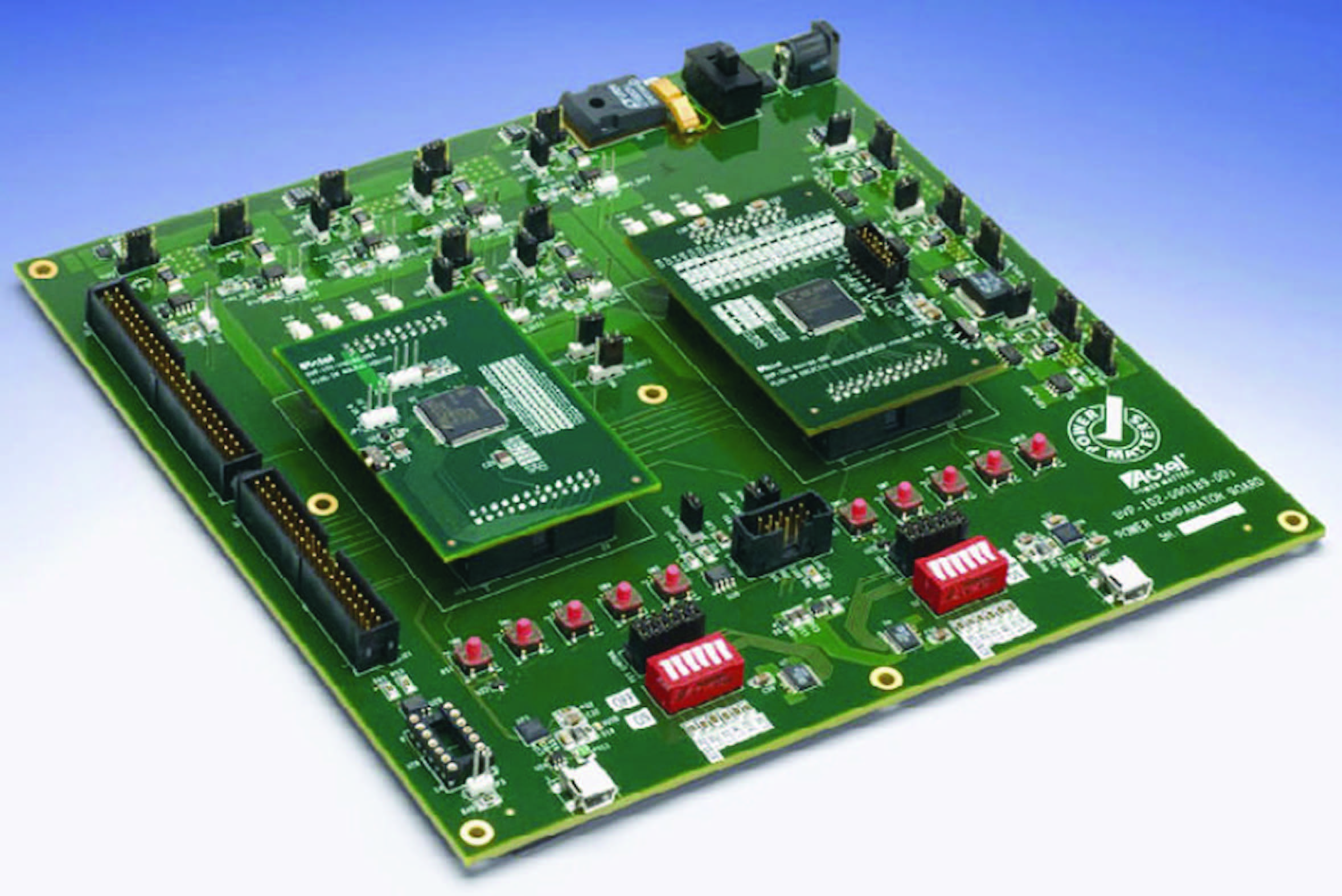

La scheda base ha differenti configurazioni per le tensioni di alimentazione che possono essere selezionate singolarmente per ogni socket. Questo permette di confrontare dispositivi predisposti per differenti alimentazioni. La scheda base ha un alloggiamento anche per diversi oscillatori che possono essere utilizzati per modificare la frequenza del clock fornito alle schede figlie. Ogni scheda figlia è stata appositamente progettata per l’FPGA o la CPLD da valutare. Alimentazioni, clock e I/O sono stati collegati ai pin preposti di ogni singolo dispositivo. In figura 4 si possono vedere due dispositivi in test.

Figura 4: due dispositivi sotto test.

I DISPOSITIVI ANALIZZATI

Per i test sono stati definiti due diversi gruppi: i dispositivi a bassa densità, quelli con circa 30 mila gate (circa 256 macrocelle o 300 logic elements) e quelli ad alta densità, approssimativamente 600 mila gate (circa 6000 logic elements equivalenti). Ovviamente trovare densità simili per diversi produttori non è cosa facile, i valori selezionati sono legati anche al fatto che la maggior parte dei venditori li supporta. I dispositivi a bassa densità messi a confronto sono AGL030, EPM240Z, XC2C256 rispettivamente di Actel, Altera e Xilinx, mentre quelli di media densità sono AGL600, EP3C5, XC3S400AN delle stesse case madri.

ANALISI DELLA POTENZA STATICA

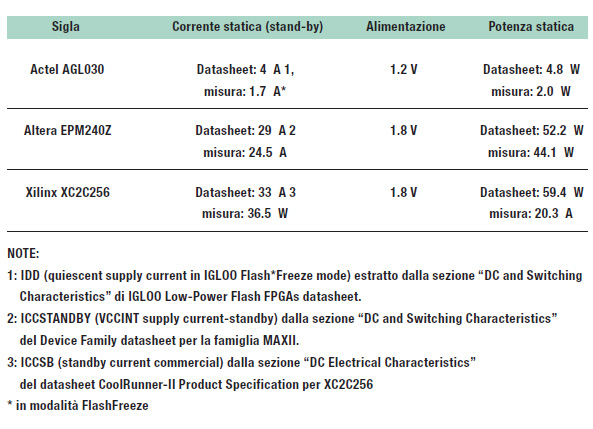

Il confronto sulla potenza statica è immediato, ogni produttore pubblica il consumo di corrente statico o in standby del dispositivo sul datasheet. La successiva moltiplicazione per la tensione di alimentazione ci fornisce il valore in potenza desiderato. Partiamo dai dispositivi a bassa densità, i valori rilevati dai datasheet sono riportati in tabella 1 e confrontati direttamente con quelli misurati utilizzando la scheda di test.

Tabella 1: potenza statica per i dispositivi a bassa densità, valori ricavati dai datasheet e misurati

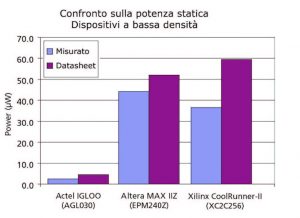

Dal confronto dei datasheet è possibile osservare come l’FPGA IGLOO di Actel consumi meno di 5uW, mentre le altre abbaino valori dichiarati 10 volte superiori. Anche misurando il consumo utilizzando la scheda di test il risultato non cambia moltissimo, i risultati ottenuti sono riportati su grafico in figura 5, la differenza è netta.

Figura 5: confronto sul consumo di potenza statica per i dispositivi a bassa densità.

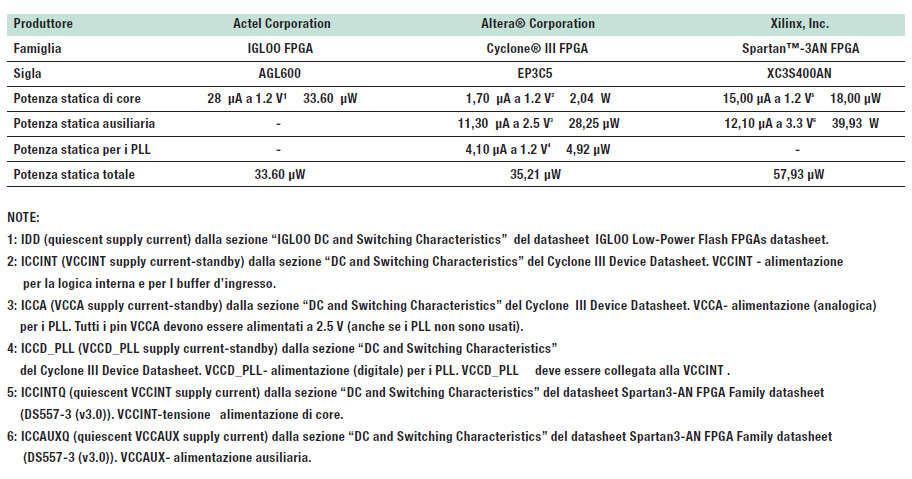

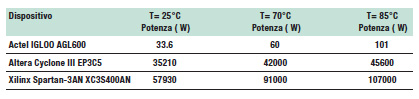

Passiamo ora ai dispositivi ad alta densità, procediamo come in precedenza. In tabella 2 sono messi a confronto i valori presi dai datasheet.

Tabella 2: Potenza statica per i dispositivi ad alta densità, valori ricavati dai datasheet.

Ottenere un confronto sperimentale attraverso la scheda di test non è cosa facile, perciò ci limitiamo a considerare i valori dichiarati. Infatti a seconda del dispositivo sono presenti più tensioni di alimentazione, il contributo di tutte deve essere sommato per arrivare a quello complessivo. Come si può vedere anche tra i dispositivi dotati di alta densità le FPGA IGLOO della Actel spiccano per i bassi consumi dichiarati. Per l’FPGA di Altera è necessario sommare il contributo delle tre alimentazioni di core, dei PLL e dell’analogica. Per l’FPGA della Xilinx necessario contemplare sia il consumo sulla tensione di core sia sulla tensione ausiliaria. Si può vedere che l’EP3C5 consuma 1000 volte più di potenza statica del dispositivo Actel e l’XC3S400AN ben 1700 volte tanto.

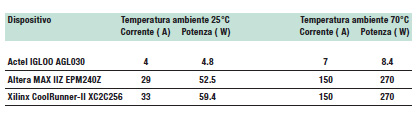

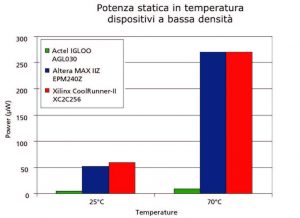

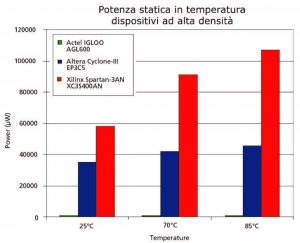

ANALISI DELLA POTENZA STATICA IN TEMPERATURA

Una analisi completa dovrebbe valutare anche l’impatto che la temperatura produce sul consumo statico. Utilizzando i dati presi dai datasheet e dai vari strumenti di previsione dei consumi è possibile valutare i consumi dei dispositivi a bassa densità in corrispondenza di una temperatura ambiente di 25°C e di 70°C (solo per il dispositivo Actel si è usato il tool di stima software). I dati sono riportati in tabella 3.

Tabella 3: Potenza statica in temperatura per i dispositivi a bassa densità.

In tabella 4 invece i valori del consumo statico dei dispositivi ad alta densità, ottenuto dai rispettivi tool di stima delle singole case produttrici: IGLOO Power Calculator per Actel, PowerPlay Early Power Estimator per Altera e Xpower Estimator per Xilinx.

Tabella 4: Potenza statica in temperatura per i dispositivi ad alta densità.

Riportando i risultati in grafico ben si comprende la differenza di consumo tra i dispositivi Actel e i prodotti della concorrenza (figura 6 e 7).

Figura 6: confronto sul consumo di potenza statica in temperatura per i dispositivi a bassa densità. Dati ottenutidai datasheet e dai tool di stima.

Figura 7: confronto sul consumo di potenza statica in temperatura per i dispositivi ad alta densità. Dati ottenuti dai tool di stima.

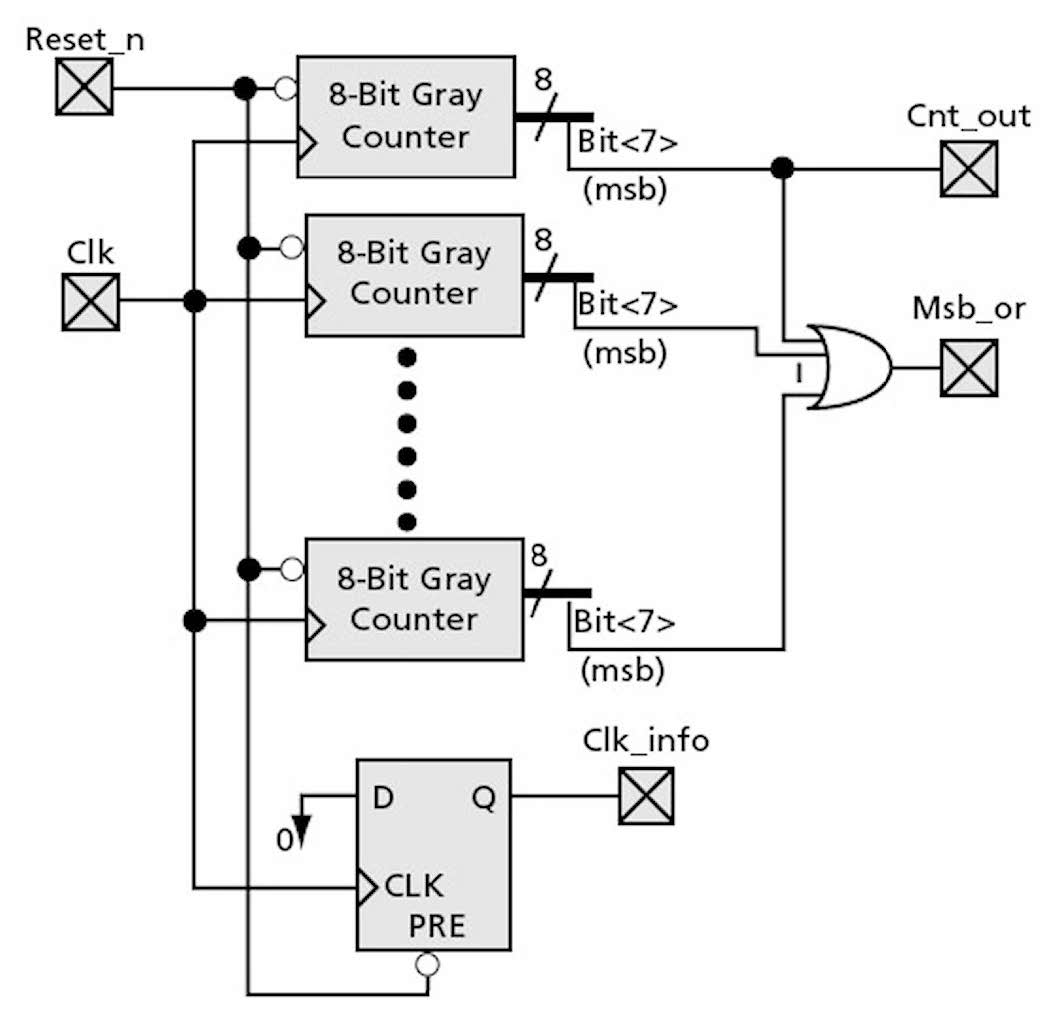

ANALISI DELLA POTENZA DINAMICA

Per valutare la potenza dinamica facciamo uso dei tool di stima messi a disposizione dei vari produttori di silicio, in più per i dispositivi a bassa densità valutiamo anche attraverso la scheda di test le differenze di corrente dinamica. Poiché il consumo dinamico è legato al tipo di programmazione, ossia alla logica che si va ad implementare, lo stesso progetto è stato utilizzato per tutti i dispositivi. Si tratta di un contatore a 8 bit in codice Gray, instanziato più volte fino a riempire il dispositivo. È stato scelto questo contatore poiché è un misto di logica sequenziale e combinatoria. Mediamente si arriva ad ottenere un 50% di registri e un 50% di logica combinatoria. In figura 8 lo schema del progetto caricato sui vari dispositivi.

Figura 8: progetto del contatore Gray a 8 bit.

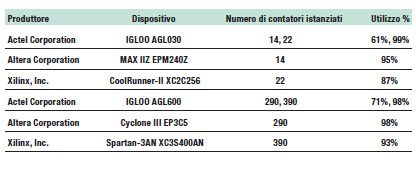

Poiché non tutti i dispositivi hanno dimensioni identiche a seconda del confronto, fatto tra due dispositivi alla volta, un numero identico di contatori sono stati istanziati. Per esempio il dispositivo Altera MAX IIZ EPM240Z permette di instanziare 14 contatori con un occupazione del 95%. Gli stessi contatori nel dispositivo Actel IGLOO AGL030 occupano un 65% della logica disponibile. I dati ottenuti per tutti i dispositivi sono riportati in tabella 5.

Tabella 5: Logica e occupazione per i dispositivi in test per la misura del consumo dinamico.

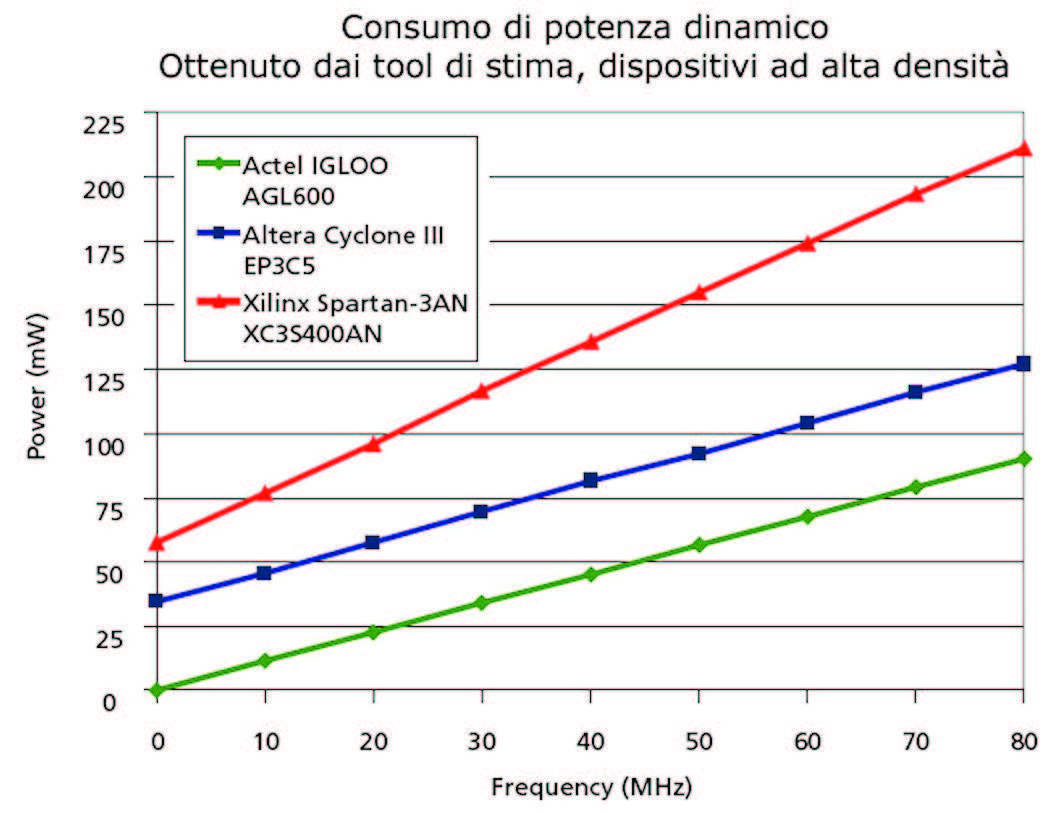

I tool di stima sono strumenti utilizzati in una fase antecedente la sintesi, perciò sono utili solamente per avere un idea di quello che potrebbe essere il consumo nel momento in cui il dispositivo diventa operativo, per questo si basano su calcoli sommari e richiedono a loro volta parametri molto generici. Ovviamente l’altro fattore che incide sul consumo dinamico è la frequenza operativa del dispositivo, perciò a passi di 10MHz abbiamo rilevato i valori proposti fino alla frequenza di 80MHz. Il risultato è che i dispositivi Actel sia nel gruppo di prodotti a bassa densità che ad alta densità spiccano sulla concorrenza. In figura 9 è visibile il confronto per i dispositivi ad alta densità.

Figura 9: confronto sul consumo di potenza dinamica per i dispositivi ad alta densità. Dati ottenuti dai tool di stima.

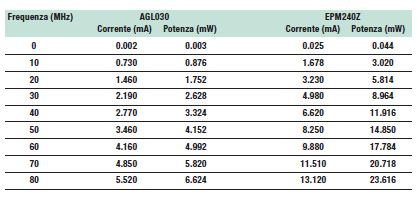

Dopo l’analisi della potenza dinamica eseguita con i tool di stima non resta che vedere se nella realtà questi dati sono effettivamente rispettati. Almeno per i dispositivi a bassa densità. Partiamo confrontando la FPGA Actel IGLOO AGL030 e la CPLD Altera MAX IIZ EPM240Z. In entrambe sono instanziati 14 contatori. Le misure sulla scheda di test portano ai valori di tabella 6.

Tabella 6: Potenza dinamica misurata per i dispositivi AGL030 e EPM240Z.

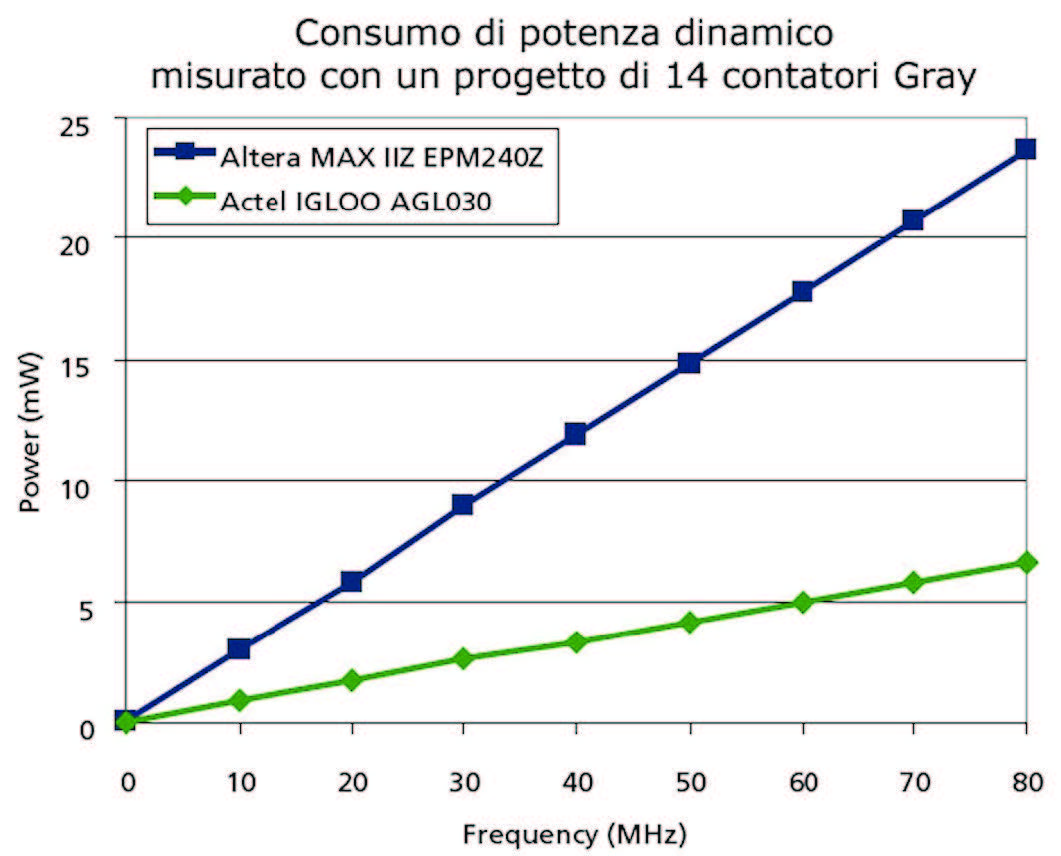

In figura 10 i risultati messi su grafico, il consumo dinamico del dispositivo Actel è nettamente inferiore alla CPLD Altera.

Figura 10: confronto sul consumo di potenza dinamica per i dispositivi AGL030 e EPM240Z. Dati misurati.

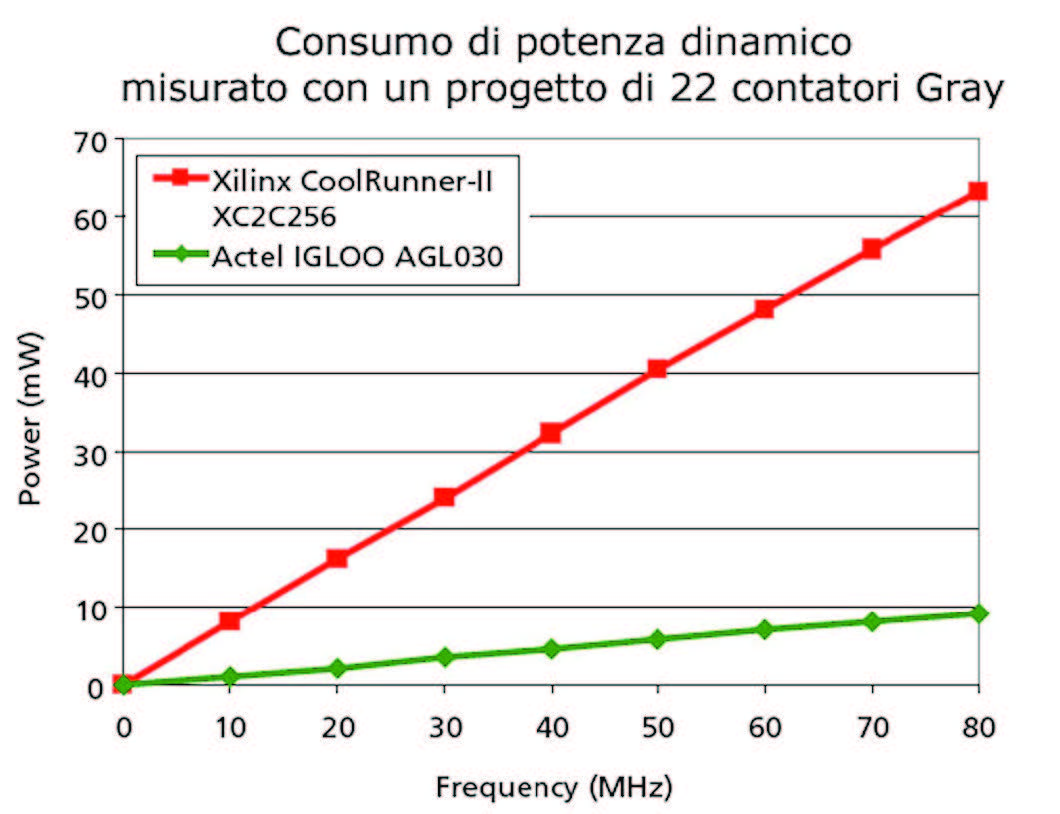

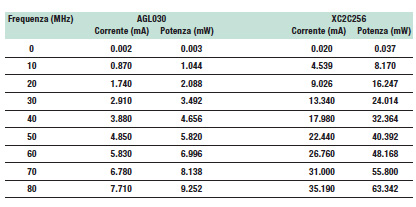

Con lo stesso principio mettiamo a confronto i dispositivi Actel IGLOO AGL030 e la CPLD Xilinx CoolRunner-II XC2C256. in questo confronto i8 contatori istanziati sono stati 22. In tabella 7 i dati rilevati, in figura 11 gli stessi dati messi su grafico.

Figura 11: confronto sul consumo di potenza dinamica per i dispositivi AGL030 e XC2C256. Dati misurati.

Tabella 7: Potenza dinamica misurata per i dispositivi AGL030 e XC2C256.

CONCLUSIONI

Dai risultati ottenuti non c’è dubbio la regina delle FPGA a basso consumo è sicuramente la famiglia IGLOO di Actel. Sia per quel che riguarda la potenza statica che per la potenza dinamica i dispositivi Actel hanno dominato la concorrenza arrivando a risultati da 10 a 1700 volte migliori.

Il mercato delle FPGA è in continua crescita e la competizione tra i produttori di questi dispositivi è sempre più serrata. Marchi storici come Actel e Altera sono stati acquisiti da Microsemi e Intel, rispettivamente. Xilinx, il marchio che nel 1985 ha realizzato la “prima” FPGA detiene tuttora un buon settore di mercato.

I circuiti FPGA hanno un ampio sviluppo nel mercato dell’elettronica e recentemente hanno trovato impiego anche nel mining delle criptovalute. Nell’ultimo ventennio il numero di porte logiche dei dispositivi FPGA è aumentato in modo esponenziale.

Sempre più spesso nella progettazione di dispositivi elettronici, oltre alle funzioni proprie del dispositivo è sentita la valutazione dei consumi.

L’avvento di nuove batterie non ha fermato la corsa ad avere dispositivi con consumi, sopratutto in fase di stand by quasi nulli.