Sul blog di Elettronica Open Source puoi leggere non solo tutti gli articoli Premium riservati agli abbonati Platinum 2.0 e inseriti nella rivista Firmware 2.0 (insieme ad articoli tecnici, progetti, approfondimenti sulle tecnologie emergenti, news, tutorial a puntate, e molto altro) ma anche gli articoli della Rubrica Firmware Reload. In questa Rubrica del blog abbiamo raccolto gli articoli tecnici della vecchia rivista cartacea Firmware, che contengono argomenti e temi evergreen per Professionisti, Makers, Hobbisti e Appassionati di elettronica. In questo articolo vedremo come proteggere i propri dispositivi USB-enabled da danni ESD.

Introduzione

I continui progressi tecnologici nel settore dei semiconduttori hanno consentito la riduzione delle geometrie di linea dei circuiti integrati moderni, permettendo di migliorarne le prestazioni, ridurre i consumi e aumentare il livello di integrazione. Ciò, tuttavia, ha finito per ridurre anche la robustezza dei circuiti stessi ai danni per scariche elettrostatiche (ESD). Nella maggior parte dei casi si rende quindi necessario proteggere le linee di ingresso/uscita del proprio circuito mediante appositi dispositivi addizionali. Nelle applicazioni più semplici si possono tranquillamente impiegare diodi zener o di clamping, varistori e soppressori di transienti discreti, etc. Ma quando il rate di commutazione del segnale della linea aumenta significativamente, diventa importante evitare che questi introducano una distorsione del segnale tale da pregiudicare il corretto funzionamento dell’interfaccia. Un problema di questo tipo è in particolare piuttosto frequente con i dispositivi USB per i quali la specifica 2.0, ad esempio, raccomanda una capacità massima sulla linea di 10 pF, includendovi il contributo della capacità del transceiver stesso, del connettore e delle piste sul circuito stampato; lo stesso diagramma ad occhi (Figura 1) raccomandato dallo standard presenta alcune criticità sotto questo aspetto. Per questo, sono disponibili sul mercato diversi dispositivi integrati progettati appositamente per la protezione delle porte USB. Di seguito, in particolare, sono presentate le soluzioni offerte da Texas Instruments.

![Figura 1. Il diagramma a occhi raccomandato dall’USB 2.0 è critico per l’implementazione di soluzioni di protezione ESD delle linee ( da [1])](https://it.emcelettronica.com/wp-content/uploads/2019/11/Il-diagramma-a-occhi-raccomandato-dalUSB-2.jpg)

Figura 1: Il diagramma a occhi raccomandato dall’USB 2.0 è critico per l’implementazione di soluzioni di protezione ESD delle linee

USB 2.0

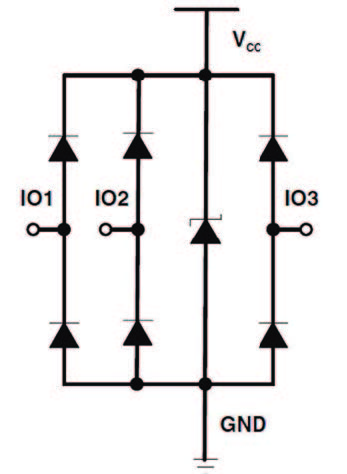

Il TPD3E001/4E001 (Figura 2), ad esempio, è un array di diodi clamping a 3 / 4 canali ideale per applicazioni USB 2.0 OTG.

Figura 2: Schema a blocchi del TPD3E001

Il dispositivo è caratterizzato per protezione ESD fino a ±15kV, in base al modello HBM (Human-Body Model), o ±8kV e ±15kV se si adottano invece le raccomandazioni Contact Discharge e Air-Gap Discharge della specifica IEC 61000-4-2. Ha una capacità di ingresso di soli 1,5 pF e corrente di leakage massima di 1 nA. Dispone di ingresso di alimentazione dedicato (con assorbimento di soli 1 nA) che può essere connesso sia alla tensione di sistema che ad una linea accessoria. Nel primo caso, il dispositivo opera come soppressore di transienti per swing di segnale oltre Vcc + Vf, dove Vf è la tensione inversa del diodo (tipicamente compresa tra 650 mV e 950 mV); nel secondo caso, invece, è in grado di tollerare elongazioni del segnale fino a 10 V. I TPD3E001/4E001 sono disponibili in package DRL, DRY e TQFN e specificati per l’intervallo di temperatura esteso compreso tra -40°C e +85°C. Per applicazioni che richiedano supporto per interfaccia con USB charger oltre che connettività USB 2.0, sono disponibili invece i modelli TPD4S012 e TPD4S014. Il primo dispone di 4 canali ESD clamping per soppressione di transiente sulle linee dati (D+, D- e ID) e su quella di alimentazione. La tolleranza sulle linee dati è fino a 6V mentre su quella di alimentazione è fino a 20 V. La capacità di ingresso delle linee dati è inferiore a 1 pF. Caratteristiche simili ma funzionalità più avanzate sono pure offerte dal TPD4S014, il cui schema a blocchi è riportato in Figura 3.

![Figura 3. Schema a blocchi del TPD4S014 (da [2])](https://it.emcelettronica.com/wp-content/uploads/2019/11/Schema-a-blocchi-del-TPD4S014-da-2-1024x593.jpg)

Figura 3: Schema a blocchi del TPD4S014

Come per i modelli precedenti sono disponibili i 3 diodi di clamping per la protezione delle linee D+, D- e ID del bus USB; le specifiche sono in accordo alla normativa IEC61000-4-2 level 4. Gli ingressi D+ e D- sono caratterizzati da capacità (verso massa) di soli 1,6 pF mentre per l’ingresso ID la capacità è standard (19 pF). In aggiunta alla protezione della linea dati, vi è poi anche una protezione "attiva" della linea di alimentazione, con un nFET interno che consente di commutare la tensione di uscita in presenza di fault (over-voltage o under-voltage) della linea di ingresso; l’ingresso VBUS del dispositivo è connesso alla tensione presente sul connettore mentre l’uscita VBUS_OUT alimenta l’elettronica locale alla scheda. Il tempo di spegnimento è di 8 us; la tensione di under-voltage è (massimo) intorno a 3V mentre quella di over-voltage (massimo) intorno a 6,5 mentre il dispositivo stesso è specificato per sopportare una tensione di ingresso massima fino a 30V. Sono disponibili un ingresso (EN) di controllo diretto di abilitazione della tensione di uscita e un’uscita (ACK) di stato dedicata per la segnalazione della condizione di fault. Al power-up, un oscillatore interno consente di ritardare l’accensione del FET interno fino a che la tensione di ingresso non sia stabilizzata (oltre la soglia di under-voltage). Allo stesso modo, in condizione di fault, un filtro di deglitch (di durata fino a 16 ms) consente di rimuovere eventuale rumore che, in condizione di fault, sovrapposto alla tensione di ingresso, potrebbe riportare in on l’uscita di alimentazione. Oltre che per over-voltage e under-voltage, è presente pure protezione per over-temperature; in condizioni normali, infatti, quando il FET è in conduzione, tutta la corrente assorbita dai circuiti a valle fluisce attraverso il dispositivo provocandone il riscaldamento (il FET ha una resistenza VDS di massimo 220 m). La protezione da over-temperature è attivata (spegnendo la tensione di uscita) per temperatura di die del dispositivo superiore a 145 °C.

USB 3.0

Per applicazione USB 3.0 Super Speed (6 Gbps) sono disponibili presso Texas Instruments i dispositivi TPD2EUSB30/ 2EUSB30A /4EUSB30 che offrono protezione da impulsi di corrente fino a 5 A e di durata fino a 8/20 μs in accordo alla normativa IEC 61000-4-5 (lightning). La capacità differenziale massima (pin-to-pin) è di 0,05 pF mentre quella verso massa di soli 0,7 pF. La tensione di break down per i TPD2EUSB30 e TPD4EUSB30 è di 7 V mentre vale 4,5 V per il TPD2EUSB30A. I TPD2EUSB30 e TPD2EUSB30A sono integrati in package space saving DRT (1 mm × 1 mm) mentre il TPD4EUSB30 ha case di tipo DQA (1 mm × 2.5 mm). Il pinout è organizzato in modo da evitare l’introduzione di skew sulle linee dati per la connessione di queste al dispositivo. Tutti i componenti sono specificati per operare nell’intervallo esteso di temperatura compreso tra -40 °C e +85 °C.

STANDARD PER QUALIFICA ESD DI COMPONENTI ELETTRONICI

Esistono diverse raccomandazioni per la qualifica ESD di dispositivi e sistemi elettronici. Il modello Human Body Model (HBM) definito dagli Standards IEC/EN 61340-3-1 o MIL-STD 883 si riferisce, ad esempio, all’utilizzo di dispositivi non alimentati, nel caso di montaggio o test. Il test è eseguito connettendo al DUT (Device Under Test) un capacitore da 100 pF, caricando e scaricando questo attraverso una resistenza da 1,5 k; sono previste 4 diverse tensioni di prova comprese tra 0,5 kV e 4 kV con altrettante correnti di picco (e una curva di corrente del tipo mostrato in Figura 4).

![Figura 4. Andamento della corrente di prova per ESD test per MIL-STD 883 (da [2])](https://it.emcelettronica.com/wp-content/uploads/2019/11/Andamento-della-corrente-di-prova-per-ESD.jpg)

Figura 4: Andamento della corrente di prova per ESD test per MIL-STD 883

I dispositivi sono quindi classificati in classe 0, 1A, 1B, 1C e 2, a seconda del valore della tensione di soglia di failure. La normativa IEC 61000-4-2 si riferisce invece ai dispositivi alimentati. In questo caso sono usati per test un condensatore da 150 pF e resistenza di 330. L’andamento della corrente di prova è riportato in Figura 5; sono previsti 4 diversi livelli con tensioni di prova comprese, nel caso di Contact Discharge, tra 2 kV e 8 kV e, nel caso di qualifica per Air-Gap Discharge, tra 2 kV e 15 kV.

![Figura 5. Andamento della corrente di prova per ESD test per IEC 61000-4-2 (da [2])](https://it.emcelettronica.com/wp-content/uploads/2019/11/Andamento-della-corrente-di-prova-per-ESD2.jpg)

Figura 5: Andamento della corrente di prova per ESD test per IEC 61000-4-2