I sistemi basati su FPGA stanno riscuotendo un crescente successo. Mentre parecchi progettisti preferiscono le architetture basate su FPGA per la loro flessibilità, grazie alla quale è possibile aggiungere caratteristiche o apportare modifiche attraverso il codice, la progettazione di un alimentatore idoneo comporta la risoluzione di alcuni problemi. Il primo è quello relativo alla presenza di più terminali di alimentazione.

Introduzione

Gli FPGA richiedono, come minimo, una tensione per l’alimentazione del core e una (o più) tensioni per l’alimentazione dei gruppi di I/O. Comunque, i sistemi basati su FPGA possono richiedere altri terminali per l’alimentazione di memorie DDR (Double Data Rate), transceiver, integrati per il livello fisico (PHY – Physical Layer) di Ethernet o microcontrollori. Oltre a ciò, questi terminali di tensione devono avere specifiche caratteristiche, come ad esempio uscite inferiori a 1,25 V, rampa monotonica durante l’accensione (ramp-up), sequenzializzazione, tempi di salita controllati e così via. Mentre i produttori di semiconduttori sono continuamente impegnati a proporre alternative integrate e di semplice uso, molte volte spetta al progettista sfruttare le caratteristiche disponibili e intervenire sul circuito proposto sul datasheet per realizzare la soluzione ottimale. Nel corso dell’articolo verranno esaminati alcuni regolatori a più uscite che possono venire impiegati come alimentatori single chip per FPGA, oltre alle modalità di realizzazione di uscite inferiori a 1,25 mediante i regolatori di bandgap disponibili.

ALIMENTATORI SU CHIP SINGOLO

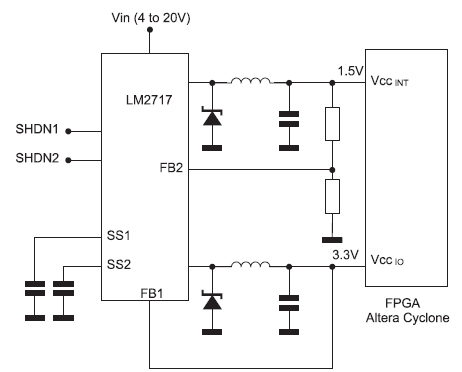

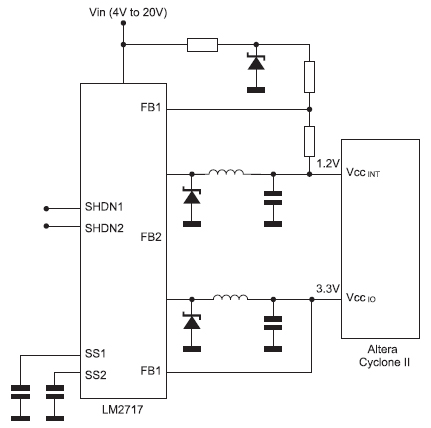

Nella figura 1 viene riportato un diagramma semplificato di un circuito per l’alimentazione di un FPGA (come ad esempio un dispositivo della serie Cyclone di Altera) con un alimentatore single chip.

Figura 1: alimentatore a commutazione integrato doppio LM2717 utilizzato per fornire una tensione di 1,5 V per il core e una di 3,3 V per gli I/O a un FPGA della serie Cyclone

Il regolatore a commutazione a doppia uscita LM2717 viene impostato per fornire una tensione di 1,5 V a 2 A (3,2 A di picco) al core e 3,3 V a 1,5 A (2,2 A di picco) agli I/O. LM2717 è una soluzione su chip singolo di media potenza contraddistinto dalle doti di semplicità e flessibilità necessarie per implementare un sistema di alimentazione compatto, caratterizzato da un’efficienza superiore al 90% e capace di soddisfare le specifiche di parecchi sistemi digitali a più terminali, tra cui FPGA, che utilizzano numerose sorgenti: 5 V, 12 V o adattatori di rete che operano nell’intervallo compreso tra 4 a 20 V. LM2717 è dotato di un’uscita regolabile e di una fissa a 3,3 V, grazie alla quale è possibile ridurre gli ingombri e aumentare la precisione della tensione di uscita mediante l’implementazione di resistori di impostazione della tensione interni su questa uscita. LM2717-ADJ è una versione di LM2717 che permette di regolare entrambe le uscite, caratteristica particolarmente apprezzata nel caso sia necessaria una tensione di I/O differente.

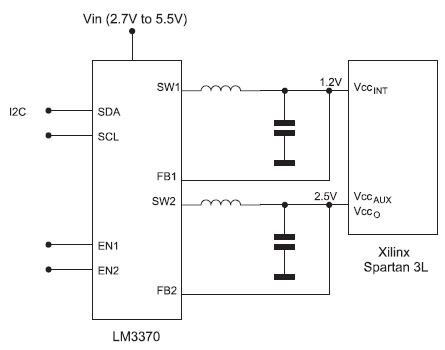

LM2717 prevede pin di abilitazione individuali (SHDN1 e SHDN2) al fine di attivare ciascuna uscita in un momento specifico o in una sequenza predeterminata nel caso ciò fosse richiesto dal sistema o nel momento in cui è necessario fornire potenza a FPGA differenti. Allo stesso modo, singoli pin di soft start (SS1 e SS2) permettono a LM2717 di impostare differenti tempi di ramp-up per ciascuna tensione di uscita al fine di soddisfare le specifiche imposte dal costruttore per i singoli FPGA e altri core di tipo digitale. Nella figura 2 viene riportato lo schema relativo a un FPGA realizzato in tecnologia da 90 nm a bassa dissipazione con core a 1,2 V alimentato da LM3370, un regolatore buck sincrono doppio in grado di fornire una corrente di 600 mA per canale.

Figura 2: alimentatore a commutazione sincrono doppio LM3370 impiegato per fornire una tensione di 1,2 V al core e di 2,5 V agli I/O e a VCCAUX a un FPGA a bassa dissipazione di Xilinx

La tensione relativa a un canale può essere regolata da 1 a 2 V in passi da 50 mV (ideale quindi per il core), mentre l’altro canale può essere programmato per un’uscita da 1,8 a 3,3 V (adatta quindi per gli I/O). Caratteristiche quali pin di abilitazione singoli, soft-start interno, risposte rapide ai transitori, flag di POR (Power-On-Reset) per ciascuna uscita fanno di questo circuito integrato una soluzione single chip ottimizzata per l’alimentazione di FPGA a bassa potenza e altri core digitali caratterizzati dalla presenza di più terminali.

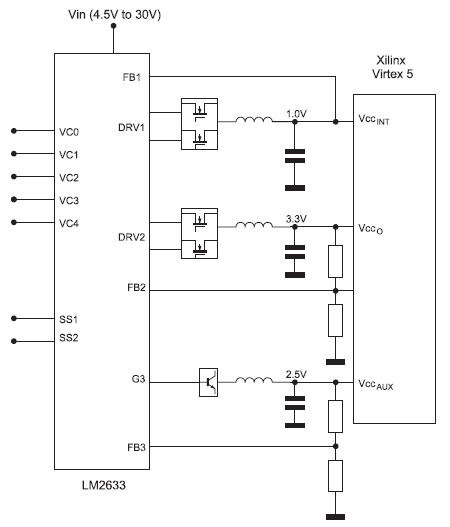

LM3370 può essere utilizzato come componente “pronto all’uso” grazie alla disponibilità di tensioni di uscita pre-programmate e di pin di alimentazione individuali. La presenza di un’interfaccia I2C compatibile consente all’utente di apportare modifiche ai diversi parametri dell’integrato anche in maniera dinamica per conferire un maggior grado di flessibilità. Questi parametri comprendono impostazione della tensione di uscita (per canale), abilitazione dell’uscita (per canale), selezione della modalità di commutazione, abilitazione della modalità a divisione di spettro (spread spectrum) e selezione dell’intervallo di frequenza della divisione di spettro. Nel diagramma semplificato di figura 3 viene schematizzata la realizzazione dell’alimentazione di un FPGA a elevata potenza a tre terminali.

Figura 3: il controllore di regolazione triplo LM2633 – che integra due regolatori buck sincroni e uno lineare - fornisce a un FPGA della serie Virtex 5 di Xilinx le seguenti tensioni: 1 V per il core, 3,3 V per gli I/O oltre a una tensione ausiliaria di 2,5 V

In questo caso, il controllore LM2633 fornisce una tensione di 1 V al core di un FPGA Virtex 5 di Xilinx, 3,3 V agli I/O e una tensione ausiliaria di 2,5 V (VCCAUX). Circuito integrato a tripla uscita, LM2633 è un esempio di come sia possibile sfruttare la tecnologia esistente per soddisfare nuove necessità, al di fuori del contesto per il quale era stato realizzato. Due delle tre uscite di LM2633 utilizzano un’architettura buck a rettificazione sincrona per garantire la massima efficienza in presenza di carichi di valore medio/alto (da 5 a 15 A per canale), mentre è disponibile un controllore LDO per una terza uscita a bassa potenza. Una delle uscite del regolatore a commutazione è caratterizzata da un intervallo di tensione compreso tra 0,9 e 2 V, ideale per l’alimentazione del core dei dispositivi digitali. Il range di tensione della seconda uscita del regolatore a commutazione, variabile tra 1,25 e 6 V, è adeguato per I/O, memorie e altre carichi. Per garantire maggiori livelli di precisione e di affidabilità, l’uscita a bassa tensione è programmabile attraverso una parola digitale parallela a 5 bit che può essere cablata oppure collegata a un processore per la riduzione (scaling) dinamica della tensione. Nelle applicazioni dove è richiesto un controllore buck sincrono doppio con uscite inferiori a 1,25 V, LM2657 rappresenta una valida alternativa ospitata in un package con ridotto numero di pin. Laddove sono richieste una potenza ridotta e la presenza di tre o quattro terminali, LP3906 rappresenta un’ottima soluzione in quanto rende disponibili due uscite a commutazione sincrone da 1,5 A e due uscite LDO a 300 A in un unico package.

TENSIONI DI VALORE SEMPRE INFERIORE

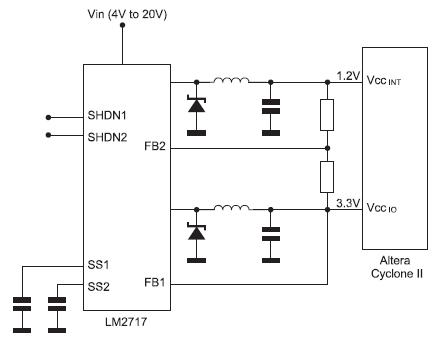

Come si evince dai precedenti esempi, la maggior parte degli attuali FPGA richiedono tensioni del core di valore pari a 1,5, 1,2 o anche inferiori (come ad esempio gli FPGA della famiglia Virtex 5 da 65 nm che richiedono una tensione del core di 1,0 V). Molti dei regolatori attualmente in commercio dispongono di un riferimento di bandgap di 1,25 V. Nelle figure 4 e 5 vengono riportati esempi di utilizzo di integrati come LM2717 con riferimenti di bandgap di 1,25 V per l’alimentazione di carichi digitali con tensioni inferiori a quelle di bandgap (sub-bandgap). L’operazione basilare del convertitore di tensione resta lo stesso, ma il modo in cui il partitore di tensione resistivo viene utilizzato per programmare la tensione di uscita del regolatore è differente.

In ogni circuito di regolazione ad anello chiuso la tensione di uscita, dopo essere stata ridotta mediante un partitore resistivo, viene confrontata con un riferimento interno. Se il riferimento è di 1,25 V, il campione normalizzato della tensione di uscita, che è introdotto nel regolatore attraverso il pin FB, deve essere impostato in modo da uguagliare questo valore al fine di mantenere la regolazione. In un sistema tradizionale, questo partitore di tensione FB è posizionato tra l’uscita (che si trova al potenziale più elevato) e la massa (che invece si trova al potenziale più basso) poiché la tensione di FB (1,25 V) si trova all’interno di questo intervallo. Nel caso di un sistema che richiede una tensione di uscita inferiore al valore di riferimento interno, è ancora necessario fornire una tensione di adattamento (1,25 V) al pin FB, anche se questo valore non è compreso tra VOUT (che è ora inferiore) e la massa. In questa situazione è necessario posizionare il partitore di tensione tra VOUT (che è a potenziale più basso) e una tensione ausiliaria il cui valore sia superiore a 1,25 V (che rappresenta quindi il potenziale più elevato). Nel circuito di figura 4 vengono utilizzati l’FPGA a 1,20 V Cyclone II di Altera e LM2717 per realizzare la configurazione più semplice, quella in cui la tensione più elevata è quella a 3,3 V del terminale.

Figura 4: in questa configurazione circuitale il terminale a 3,3 V viene utilizzato come tensione ausiliaria per la generazione della tensione del core di valore inferiore a 1,25 V

Per quest’ultimo è necessario predisporre opportuni accorgimenti per quel che riguarda il filtraggio e la stesura del layout (ad esempio è consigliato l’uso di un condensatore di disaccoppiamento ceramico posto in prossimità del punto in cui l’estremità inferiore del partitore resistivo incontra il terminale a 3,3 V) poiché la regolazione dell’uscita con valore inferiore alla tensione di bandgap dipenderà dalla stabilità di questo terminale.

Anche la sequenzializzazione è importante, in quanto il terminale a 3,3 V deve essere presente per garantire un’adeguata regolazione prima che venga attivata l’uscita della tensione del core. In parecchi FPGA, la tensione di alimentazione del core di 1,2 o 1,0 V deve essere stabile all’interno di tolleranze pari a ± 50 mV o ± 60 mV, ragion per cui tutti i transitori, le ondulazioni e le variazioni di tolleranza devono essere mantenute entro questi limiti. Nella figura 5 viene riportato un metodo alternativo per ottenere un’uscita di valore inferiore alla tensione di bandgap che prevede il ricorso a un generatore indipendente per un terminale ausiliario, rappresentato in questo caso da un riferimento di tensione a basso costo (Zener di precisione) come ad esempio LM4040CIM3-2,5 (0,5%) o LM4040DIM3-2,5 (1%).

Figura 5: in questa configurazione viene utilizzato il riferimento di tensione LM4040 per la generazione della tensione del core di valore inferiore a 1,25 V

Un approccio di questo tipo evita l’accoppiamento incrociato tra i potenziali transitori dell’uscita a 3,3 V e la regolazione all’uscita a 1,20 V. In questo modo il terminale a 3,3 V può essere alimentato dopo quello a 1,2 V, oppure essere disattivato in ogni momento senza per questo disturbare la regolazione dell’uscita a 1,2 V. L’accuratezza di questa uscita dipende dalla regolazione della linea del riferimento di tensione selezionato. Poiché la precisione della tensione del core è un fattore di primaria importanza, la scelta del riferimento di tensione adatto è basilare.

A proposito di FPGA, è iniziato un corso sul VHDL https://it.emcelettronica.com/vhdl-for-beginners-entita-e-architetture