Il presente articolo introduce l’architettura della Memory Management Unit di un processore SPARC-V8 compatibile; l’unità è progettata per un’implementazione single-chip in grado di gestire applicazioni multiuser/multitasking con supporto per contesti multipli e protezione a livello di pagina.

La maggior parte delle applicazioni multiuser/multitasking richiede un’unità di gestione della memoria (Memory Management Unit) che supporti una modalità di indirizzamento virtuale per la protezione delle pagine e la riduzione dei problemi di frammentazione. Il primo sistema operativo ad introdurre una funzionalità del genere è stato il MULTICS (Multiplexed Information and Computing Service) sul finire degli anni 60’. SPARC (Scalable Processor ARChitecture) è un processore RISC introdotto da Sun MicroSystem nel 1985; l’architettura è completamente aperta e non proprietaria. La specifica V8 è stata rilasciata nel 1990 e standardizzata come IEEE 1754-1994; successivamente è stata definita la versione V9 che prevede una estensione a 64-bit. Lo standard non richiede espressamente l’utilizzo di MMU ma definisce linee guida per la realizzazione di una soluzione single-chip; indica una architettura hardware (SRMMU – SPARC V8 Reference MMU) di riferimento e descrive l’organizzazione in memoria principale delle tabelle per la traduzione degli indirizzi. Leon-3 è una implementazione VHDL di un processore SPARC-V8 distribuita da Gaisler Research sotto licenza GNU/GPL; il modello è derivato da una descrizione RTL sviluppata all’interno di un programma di ricerca dell’Agenzia Spaziale Europea. Leon-3 supporta una implementazione della SRMMU in accordo allo standard. Di seguito è riportata una introduzione all’architettura della SRMMU ed alla sua implementazione in Leon-3.

L’architettura SRMMU

Le caratteristiche principali della MMU per un processore SPARC-V8 compatibile, secondo quanto specificato in appendice allo standard, sono le seguenti:

➤ indirizzo virtuale a 32 bit;

➤ indirizzo fisico a 36 bit;

➤ dimensione di pagina 4 Kbyte;

➤ traduzione degli indirizzi virtuali su 3 livelli;

➤ supporto per map lineare degli indirizzi fino ad un’area di dimensione 4 GBytes;

➤ gestione hardware delle condizioni di miss in accessi alla cache delle tabelle di traduzione degli indirizzi;

➤ supporto per contesti multipli;

➤ protezione a livello di pagina.

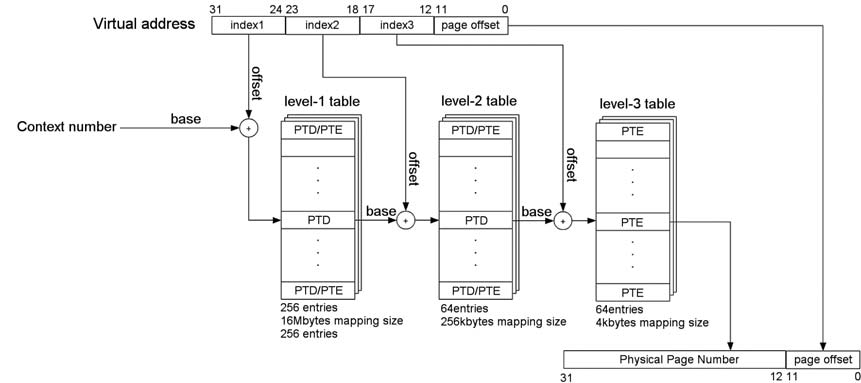

La figura 1 mostra uno schema di principio della procedura di traduzione degli indirizzi.

Figura 1: schema di traduzione degli indirizzi virtuali in un processore SPARC-V8.

L’indirizzo fisico della pagina (bit [35:12]) è calcolato in base al contesto associato al processo in esecuzione ed alla parte alta (bit [31:12]) dell’indirizzo virtuale; la locazione all’interno della pagina selezionata (bit [11:0]) è invece direttamente indirizzata dalla parte bassa dell’indirizzo virtuale. Per individuare l’indirizzo fisico di pagina viene utilizzata una struttura di tabelle di traduzione su tre livelli. Il Context Number definisce l’indirizzo base nella memoria principale dove risiede la radice di questa gerarchia di tabelle da utilizzare per il contesto corrente (associato ad esempio al processo in esecuzione); le tabelle possono contenere ad ogni locazione:

➤ PTD (Page Table Descriptor), che definiscono l’indirizzo base all’interno della memoria principale dove risiede la tabella associata al livello successivo;

➤ PTE (Page Table Entries), che definiscono i 24 bit di peso maggiore dell’indirizzo fisico ed includono informazioni di vario genere sull’area indirizzata, tra le quali la possibilità di mantenere la pagina in cache o il permesso ad accedere ad essa.

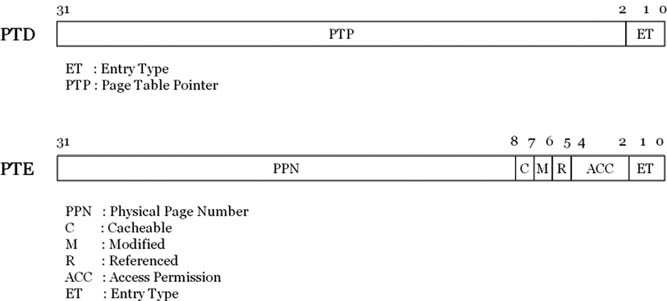

Il formato dei PTD e PTE è riportato in figura 2.

Figura 2: schema Formato di PTD e PTE.

Nel caso di PTD i campi I1, I2 ed I3 dell’indirizzo virtuale rappresentano l’offset a cui puntare all’interno della tabella al successivo livello per completare la traduzione degli indirizzi; nel caso di PTE selezionano, invece, la pagina all’interno dell’area indirizzata. A seconda del livello a cui si trovano, infatti, i PTE individuano aree di memoria di dimensioni diverse (root : 4 GByte – livello 1 : 16 MByte – livello 2 : 256 KByte – livello 3 : 4 KByte); l’indirizzo PPN contenuto in un PTE è allineato rispetto a questi limiti. Nel caso, ad esempio, di un PTE in tabella al secondo livello, il PPN contenuto deve avere uguali a zero i 6 bit di peso minore così da puntare ad un’area di 64 pagine di 4 KByte ognuna; la pagina da selezionare all’interno di questa area è indicata dal campo I3 dell’indirizzo virtuale. Per evitare eccessive penalità legate agli accessi in memoria principale per la scansione delle tabelle, l’architettura SPARCV8 prevede che la MMU integri una cache interna dedicata per i PTE; tale cache è denominata Page Description Cache (PDC) o più spesso Translation Looka- side Buffer (TLB). Nel caso di miss in TLB, la MMU inizia la procedura di table walk che ricerca il PTE scandendo le tabelle in memoria principale; qualora non esista o quando indirizzi una pagina per la quale non si goda delle dovute autorizzazione di accesso viene segnalata una condizione di errore (trap) al processore. Dal punto di vista software, la MMU implementa i seguenti registri interni (cui il processore accede come verso ogni altra periferica):

➤ control register, che consente ad esempio di specificare implementazione e numero di versione della MMU, o di abilitare/disabilitare l’unità;

➤ context table pointer, che rappresenta l’indirizzo base nella memoria principale dove risiede la tabella con i Context Number definiti per l’applicazione in esecuzione;

➤ context register, che consente di specificare quale dei possibili spazi virtuali eventualmente definiti deve essere considerato come quello corrente; indirizza quindi nella Context Table Pointer la locazione da cui prelevare il Context Number da utilizzare per accedere alla radice della gerarchie di tabelle per la traduzione degli indirizzi;

➤ fault status register, che fornisce indicazioni sul tipo di eccezione segnalato dalla MMU al processore;

➤ fault address register, che contiene l’indirizzo di memoria di virtuale che ha generato l’eccezione segnalata.

La MMU supporta, inoltre, le seguenti istruzioni privilegiate di flush (che consente di rimuovere contenuti della TLB in accordo a criteri specifici) e probe (che consente di leggere un PTE dalla TLB o dalla memoria principale).

Un’implementazione RTL open-source

La figura 3 mostra uno schema di principio dell’architettura della MMU progettata per il processore Leon-3 in accordo alle raccomandazioni dello standard SPARC-V8 introdotte in precedenza.

![Figura 3: architetture della MMU di Leon-3 (da [2])](https://it.emcelettronica.com/wp-content/uploads/2017/06/architetture-della-MMU-di-Leon-3-da-2.jpg)

Figura 3: architetture della MMU di Leon-3 (da [2])

La MMU integrata può essere configurata in fase di sintesi per supportare due unità distinte od una condivisa; in questo caso eventuali richieste simultanee sui bus indirizzi e dati, vengono opportunamente serializzate con, tuttavia, conseguente stallo della pipeline. La TLB della MMU ha una struttura di tipo direct-mapped, full-way associative; l’algoritmo di sostituzione è configurabile in fase di sintesi come random o LRU. Il numero di locazioni in TLB è configurabile tra 2 e 64 in funzione delle risorse disponibili. Nell’architettura proposta, come mostrato in figura 3, l’MMU viene richiamata in presenza di una condizione di miss in accesso alla cache per la traduzione degli indirizzi virtuali o come oggetto delle istruzioni privilegiate di flush/probe; la MMU inizia quindi le operazioni di confronto in TLBCAM per verificare l’esistenza dell’indirizzo richiesto in TLB. In caso di miss, viene iniziata la procedura di table walk accedendo alla memoria principale mediante interfaccia master sul bus AMBA AHB. Al termine della ricerca della PTE, tag e dati relativi vengono memorizzati in TLBCAM e memoria interna in base all’algoritmo di sostituzione selezionato; la sincronizzazione della memoria è opportunamente gestita. L’MMU restituisce, infine, verso la cache l’indirizzo fisico (utilizzato per l’inizializzazione del write-buffer o del buffer istruzioni) od il PTE nel caso di istruzioni di probe.

Conclusioni

La natura aperta dello standard SPARC e l’esistenza di una implementazione open source (il processore Leon-3) ne fanno una interessante soluzione per scopi didattici e di ricerca. Nel presente articolo in particolare, sono state discusse le caratteristiche generali e i dettagli implementativi della MMU per la gestione in hardware della traduzione degli indirizzi virtuali nelle applicazioni multiuser/multitasking.