La particolarità principale di questo transceiver vocale consiste nel fatto che grazie all’uso di un transceiver RF digitale permette di realizzare un canale audio full-duplex tramite un canale radio half-duplex.

Il transceiver può funzionare infatti alternativamente come ricevitore o come trasmettitore, generalmente su frequenze diverse. Inoltre, dato che il bit rate massimo supportato dal transceiver è inferiore a quello necessario per un canale voce full-duplex, sviene utilizzata una compressione software dell’audio tramite un algoritmo DPCM implementato dal microcontrollore.

I COMPONENTI PRINCIPALI DEL TRANSCEIVER

I componenti principali dell’apparato sono il microcontrollore C8051F330 prodotto da Silicon Laboratories e Il transceiver digitale CC1020 di Texas Instruments.

LA MCU C8051F330

Il microcontrollore C8051F330 prodotto da Silicon Laboratories, è basato su una CPU compatibile 8051, la nota CPU standard industriale di Intel. Questa CPU ad 8 bit con architettura Harvard (la memoria programma e quella dati utilizzano bus separati) è dotata dell’ampio set di modalità di indirizzamento caratteristico dei processori CISC. L’implementazione di Silicon Laboratories presenta in aggiunta un’architettura a pipeline che permette alla CPU di eseguire la maggior parte delle istruzioni in 1 o 2 cicli di clock, contro gli usuali 12 (pari ad un ciclo macchina) delle CPU 8051 standard. Di conseguenza, il throughput massimo arriva a 25 MIPS alla velocità di clock di 25 MHz. La memoria RAM è pari a 768 Byte, mentre la memoria programma è una Flash di 8 KB. Completano la dotazione della MCU le usuali periferiche di comunicazione come UART ed SPI, oltre alle interfacce ADC e DAC con 10 bit di risoluzione, utilizzate in questa applicazione. Le periferiche possono essere direzionate sui pin esterni della MCU tramite una crossbar.

IL TRANSCEIVER DIGITALE CC1020

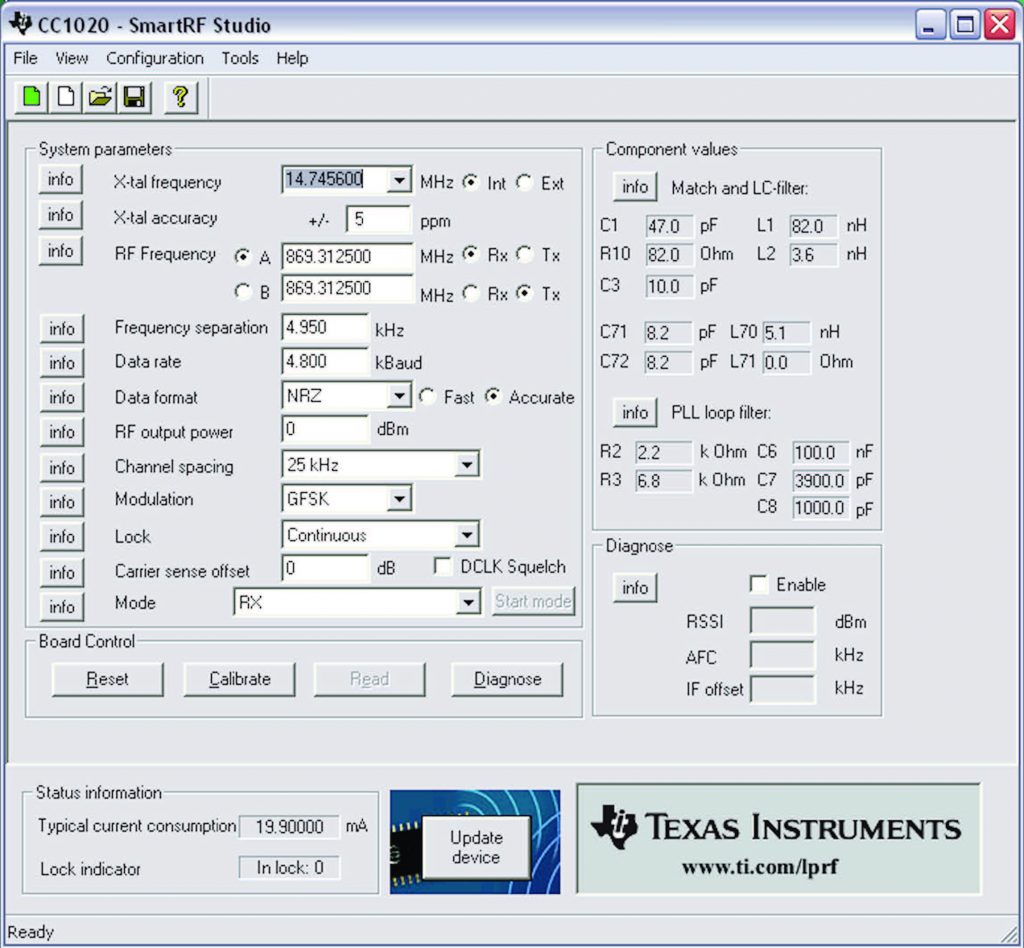

Il chip CC1020 è un transceiver UHF digitale funzionante nelle due bande ISM e per dispositivi Short Range comprese tra 402-470 MHz e 804-940 MHz. La distanza tra i canali può essere di 12.5 o 25 kHz. Il CC1020 supporta diversi tipi di modulazione, tra cui FSK ed ASK (nella variante On-Off Keying, OOK). Il segnale digitale in ingresso può essere nel formato NRZ (Non-Return-to-Zero), codificato Manchester o senza codifica: in questo caso si parla di transparent UART, ma il sincronismo dev’essere garantito da un circuito esterno. A seconda del tipo di codifica usata, il bit rate può arrivare ad un massimo di 153.6 kbps (utilizzando la codifica NRZ). Il CC1020 comprende al suo interno alcuni registri di configurazione e controllo: allo startup è infatti necessario configurarlo opportunamente in funzione delle caratteristiche di funzionamento dell’applicazione, come frequenza di funzionamento, tipo di modulazione, bit rate, settaggio del PLL, potenza d’uscita. I valori adatti da inserire nei registri possono essere ricavati, se necessario, tramite la utility SmartRF Wizard, scaricabile dal sito di Texas Instruments. Tramite la stessa utility SmartRF Wizard è possibile anche ricavare i valori adatti dei componenti per il filtro del PLL, per i filtri di accoppiamento RF ed altri filtri opzionali. In figura 1 è riportata l’interfaccia di SmartRF.

Figura 1: SmartRF Wizard per la configurazione del transceiver CC1020.

Il CC1020 si collega ad un micro esterno tramite due interfacce digitali (più altri segnali di controllo): un’interfaccia dati per i dati ricevuti o da trasmettere (pin DIO e DCLK), ed un’interfaccia di controllo utilizzata per configurare i registri del chip. Quest’interfaccia di controllo è compatibile con una classica SPI a 4 fili, ma anche l’interfaccia di segnale può essere usata, con alcuni accorgimenti, con una SPI, come vedremo nell’applicazione in oggetto.

L’HARDWARE

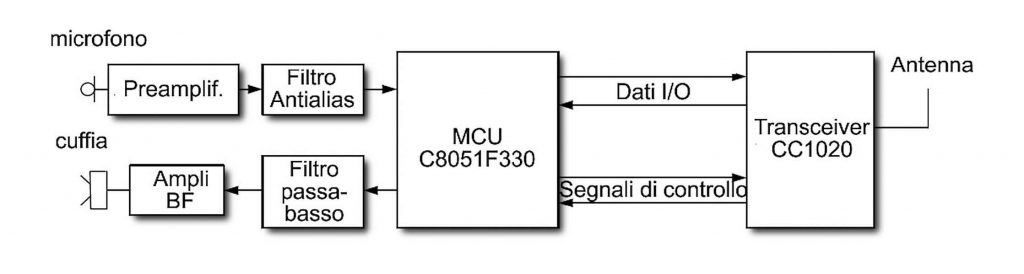

In figura 2 è riportato lo schema a blocchi dell’apparato. Il segnale audio ricevuto dal microfono viene innanzitutto amplificato in modo da utilizzare al massimo la scala dell’ADC del microcontrollore, tra 0 e 2.43V.

Figura 2: schema a blocchi del transceiver wireless.

Prima di subire la conversione, il segnale viene inoltre filtrato da un filtro anti-aliasing a 3 poli (18 dB/ottava) con frequenza di taglio di 4 KHz. Il segnale viene campionato alla frequenza di 8kHz e convertito in un valore a 10 bit dal modulo ADC del micro. Tramite un algoritmo DPCM viene quindi compresso in un valore su 4 bit ed inviato ad un buffer per la trasmissione. Nel paragrafo dedicato all’analisi del firmware vedremo in maniera più approfondita il funzionamento del compressore/decompressore DPCM. Il segnale così digitalizzato è inviato all’ingresso dati DIO del CC1020 per la trasmissione radio. In ricezione, il segnale ricevuto dall’RX del CC1020 viene ricavato tramite lo stesso pin DIO, che risulta quindi multiplexato tra le funzioni di trasmissione e ricezione. Il microcontrollore immagazzina i dati ricevuti in un buffer apposito, quindi li decomprime tramite l’algoritmo di decompressione DPCM. A questo punto si ottiene nuovamente il segnale quantizzato su 10 bit. Il segnale digitale viene poi convertito in analogico dal DAC del micro, quindi filtrato tramite un filtro passa-basso di Butterworth a 5 poli (30 dB/ottava) per eliminare le componenti dovute alla frequenza di campionamento. Amplificato in potenza dall’IC tipo TPA4861, è infine reso disponibile per l’ascolto tramite un piccolo speaker.

INTERFACCIA DATA I/O E CONTROLLO TRA MCU E CC1020

Il micro comunica con il Transceiver CC1020 tramite due interfacce digitali: un’interfaccia Dati gestita tramite il modulo SPI, ed un’interfaccia di controllo gestita in software. L’interfaccia dati del CC1020 è quella che rende disponibile il segnale digitale in ricezione tramite il pin DIO. Nella cosiddetta modalità Slave (vedremo più avanti) il clock dell’SPI è fornito dal CC1020, ed ha un valore di 153.6 KHz corrispondente al bit rate di 153.6 kbps. Questo è come sappiamo il bit rate massimo supportato dal CC1020. Il pin di ingresso dati del modulo SPI (MOSI) e quello di uscita dati (MISO) dello stesso modulo sono collegati insieme al pin DIO del CC1020. L’uso alternativo dei due pin dell’SPI è controllato configurando opportunamente le porte del micro a seconda che sia in ricezione o trasmissione. In trasmissione quindi, viene usata la stessa interfaccia SPI. Dato che non è usato il pin NSS (Slave Select) è necessario eseguire il data framing in software, tramite una Sync Word, per allineare i byte di dati. Vedremo questo più in dettaglio nel corso dell’analisi del firmware. L’interfaccia di controllo del CC1020 è utilizzata nella fase di configurazione e calibrazione. Viene implementata in software come un’interfaccia bit-banged, dato che non richiede un uso particolarmente critico in termini di tempistiche (al contrario dell’interfaccia dati). Potete trovare lo schema completo dell’apparato nell’AN147 di Silicon Laboratories.

INIZIALIZZAZIONE DEL CC1020

Come già accennato, allo startup è necessario configurare opportunamente il CC1020 in funzione delle caratteristiche dell’apparato, come frequenza di funzionamento, bit rate, settaggio del PLL, ecc. L’inizializzazione è eseguita dalla procedura CC1020_Init() del firmware. Il bit rate di 153.6 kb/sec è il massimo ottenibile dal CC1020, utilizzando la codifica NRZ. Successivamente alla configurazione, è necessario calibrare il modulo CC1020 seguendo una particolare procedura descritta nel suo datasheet. Questa procedura è necessaria per calibrare il VCO ed il PLL in funzione di variazioni della tensione di alimentazione, della temperatura o del processo di fabbricazione del chip. è necessario ripetere questa procedura solo per ampie variazioni della tensione di alimentazione (maggiori di 0.25 V) o per variazioni di temperatura superiori ai 40°C. Anche questa procedura è implementata dalla funzione CC1020_Init() del firmware.

MASTER MODE E SLAVE MODE ENDPOINT

Una volta terminate le procedure di configurazione e calibrazione del CC1020, il canale di comunicazione è attivo e pronto per trasmettere e ricevere dati. Nella comunicazione tra due apparati del genere, uno viene designato come Master e l’altro come Slave. Il primo apparato che capta un segnale audio di livello abbastanza elevato (il livello di soglia è definito tramite il parametro Audio_QuietThreshold) viene designato come Master. Sarà allora responsabile della temporizzazione dei dati e della sincronizzazione nella commutazione da RX a TX degli apparati. Il Master inizia quindi a trasmettere un pacchetto dati, dettagliato più avanti. L’altro apparato viene designato come Slave: il transceiver viene configurato nella modalità ricezione, e attende di ricevere un pacchetto dati. L’apparato Slave inoltra sincronizza periodicamente il suo clock con quello del Master, come vedremo. La trasmissione e la ricezione dei pacchetti sono implementate tramite delle state-machine.

TRASMISSIONE DI UN PACCHETTO DATI E FORMATO DEL PACCHETTO

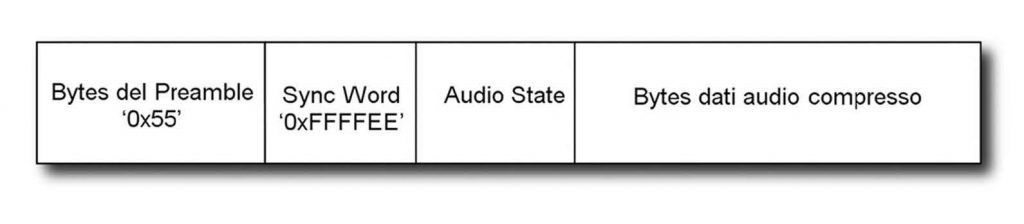

La trasmissione di un pacchetto è iniziata dopo che il transceiver viene configurato in modalità trasmissione. È necessario attendere che il transceiver sia calibrato e con il PLL agganciato. In figura 3 è riportato il formato di un pacchetto dati: la trasmissione inizia con un Preamble, un certo numero di bytes del valore ‘0x55’.

Figura 3: formato del pacchetto dati.

Questo valore è quello suggerito nel datasheet del CC1020 e serve per calibrare il data slicer (il componente che distingue gli zeri dagli uno). Il numero di bytes che costituiscono il Preamble è definito dalla costante TX_NumBytesPreamble (valore di default pari a 8). Dopo il preambolo, è trasmessa un Sync Word, costituita da 24 bit con valore ‘0xFFFFEE’. La Sync Word è necessaria per allineare l’interfaccia SPI ai byte ricevuti. Quindi viene trasmesso un byte Audio State, che indica se il segnale audio captato ha un valore superiore o meno a quello di soglia. Infine sono trasmessi i byte dati costituiti dall’audio digitalizzato e compresso. Il numero di byte dati da trasmettere in ogni pacchetto è definito dalla costante RXTX_BytesOfData (valore di default 200).

RICEZIONE DI UN PACCHETTO DATI

In ricezione il transceiver è configurato in questa modalità, quindi il firmware attende la ricezione dei byte del Preamble. Una volta ricevuto un numero di byte minimo, definito dalla costante RX_MinBytesPreamble (valore di default 2), attende la ricezione della Sync Word. Come già accennato, questa word è necessaria per allineare l’interfaccia SPI al byte. Ricevuto il primo byte ‘0xFF’ della Sync Word, l’interfaccia SPI del micro viene disabilitata, ed al suo posto viene abilitata un’interfaccia del tipo ‘edge capture’ sensibile ai fronti del segnale, che utilizza il segnale DIO del CC1020 come input. Il firmware è configurato in maniera da attivare un interrupt al primo fronte di discesa: ciò avviene alla ricezione della prima parte del byte ‘0xEE’ della sync word (ovvero ‘11101110’ in binario). Nella routine di interrupt si attende la ricezione del secondo fronte di discesa al termine dei restanti 4 bit ‘1110’, quindi si predispone il pin collegato al segnale DCLK del CC1020 per la rilevazione del successivo fronte di salita del clock. A questo punto viene nuovamente riabilitata l’interfaccia SPI che risulta così allineata al successivo byte (che corrisponde al byte Audio State). Vengono allora ricevuti i restanti byte di dati, come definito dalla costante RXTX_BytesOfData. Alla fine della ricezione del pacchetto dati, se l’apparato è stato designato come Slave, procede alla resincronizzazione del clock. Ricordiamo che il clock è infatti generato dall’apparato Master. La re-sincronizzazione può essere necessaria ad esempio a causa di differenze dei clock dei due apparati o della mancata ricezione di pacchetti dati.

SINCRONIZZAZIONE DELL’ADC E DEL DAC

In ogni caso, l’apparato ricevente, che sia il Master o lo Slave, esegue una routine per la sincronizzazione del sample rate: questa routine serve per gestire in maniera ottimale i buffer di trasmissione e ricezione. In trasmissione, alla fine dell’invio di ogni pacchetto, la dimensione del buffer di trasmissione viene confrontata con un valore teorico UTXFIFO_TARGET: se il buffer contiene troppi campioni, il sample rate dell’ADC viene diminuito, al contrario se ne contiene troppo pochi il sample rate viene aumentato. Queste variazioni sono dovute a differenze nei clock del micro e del transceiver. Analogamente, in ricezione l’output rate del DAC viene variato confrontando la dimensione del buffer di ricezione con una dimensione teorica URXFIFO_TARGET. Ciò può rivelarsi necessario a causa piccole differenze nei clock dei due apparati in comunicazione.

TERMINAZIONE DEL PACCHETTO

Al termine del time slot assegnato alla trasmissione/ricezione di un pacchetto dati, la state machine entra nello stato RXTX_TimeOutState. In questo stato viene esaminata la variabile TimeOut_EntryMode che indica se la trasmissione/ricezione è avvenuta o meno con successo: a seconda di ciò stabilisce se continuare a trasmettere o ricevere un pacchetto dati nel successivo time slot.

COMPRESSIONE E DECOMPRESSIONE DEL SEGNALE AUDIO

Dato che il bit rate massimo supportato dal CC1020 è pari a 153.6 kbps, il throughput teorico massimo è di circa 19.2 kB/sec, vale a dire due canali audio (uno in ricezione e l’altro in trasmissione) con un flusso dati di 9.6 kB/sec ciascuno. Ciò senza considerare l’overhead dovuto all’intestazione di ciascun pacchetto dati, come abbiamo visto in precedenza (figura 3). Alla frequenza di campionamento di 8 kHz (standard per la digitalizzazione della voce) con 10 bit di dati per campione, il flusso di dati è pari a 10 kB/s. È quindi necessario ridurre in qualche modo la banda necessaria per trasmettere i dati: ciò viene ottenuto tramite una compressione DPCM (Differential Pulse Code Modulation).

L’ENCODER DPCM

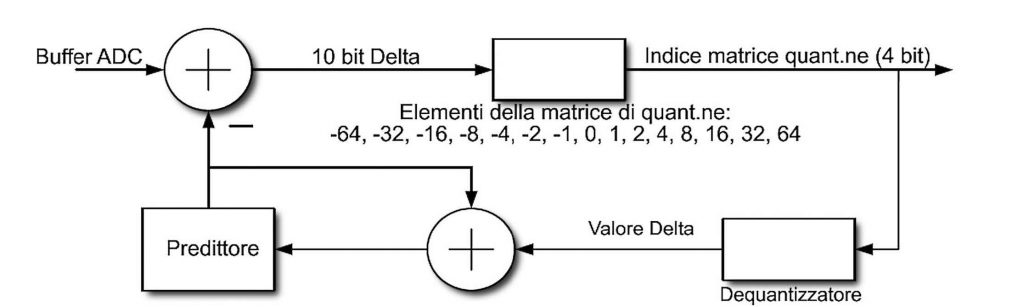

In trasmissione, il segnale audio campionato alla frequenza di 8 kHz e quantizzato su 10 bit dal modulo ADC del microcontrollore, viene elaborato dal compressore (o encoder) DPCM in modo da codificare ogni campione con solo 4 bit, riducendo così la banda necessaria da 10 kB/s a 4 kB/s. In figura 4 è riportato lo schema di funzionamento dell’encoder DPCM.

Figura 4: schema di funzionamento dell’encoder DPCM.

L’encoder confronta il campione attuale con il valore in uscita da un predittore (determinato dal campione precedente), quindi codifica solamente la differenza tra i due valori. Poiché la differenza è un valore statisticamente relativamente piccolo, è possibile codificarlo utilizzando un numero inferiore di bit, 4 invece di 10 nel nostro caso. Un’ulteriore vantaggio nell’accuratezza della codifica si ottiene scegliendo di codificare la differenza usando una scala non lineare –esponenziale nel nostro caso come riportato nello schema: in tal modo è possibile seguire con maggiore accuratezza sia segnali che variano lentamente nel tempo che segnali con brusche variazioni. L’uscita del quantizzatore è in realtà l’indice della matrice di quantizzazione, rappresentato da un valore su soli 4 bit anziché 10 del segnale originario. Ad ogni ciclo di campionamento, il valore delta viene riportato al predittore: questo delta viene quindi sommato al valore attuale memorizzato dal predittore per ottenere il valore aggiornato in uscita dallo stesso che sarà usato al ciclo successivo. E così via ad ogni campionamento del segnale. In definitiva, la compressione DPCM è un tipo di compressione lossy che permette di ottenere dei discreti risultati confrontando il campione attuale con il valore ricavato dal predittore. Basandosi su un predittore, quindi, permette di ottenere una significativa riduzione del numero di bit necessari per quantizzare il segnale fintanto che l’algoritmo di predizione sia efficace. La compressione ottenibile con questa tecnica è relativamente modesta se confrontata con tecniche più sofisticate (come ad esempio i codec GSM), ma la DPCM è particolarmente facile da implementare e richiede poche risorse computazionali, per cui risulta adeguata in simili applicazioni embedded.

IL DECODER DPCM

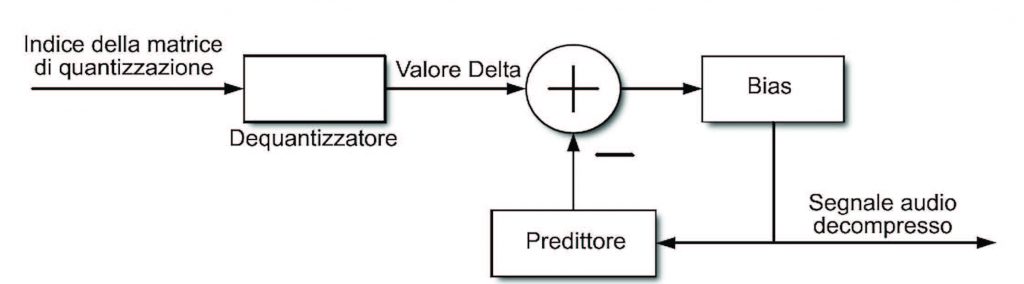

In figura 5 è riportato lo schema di funzionamento del decoder DPCM. Il dequantizzatore ricava il valore delta a partire dall’indice della matrice di quantizzazione, quindi ricostruisce il valore del segnale sommandogli il valore contenuto nel predittore.

Figura 5: schema di funzionamento del decoder DPCM.

Il valore risultante viene traslato tramite un valore di bias in modo da tendere verso un valore medio, compensando così eventuali errori nella ricezione dell’indice della matrice. Il valore ricostruito viene infine riportato al predittore così da aggiornarne il valore per il ciclo successivo. Si noti che i valori compressi su 4 bit vengono impacchettati due alla volta in un singolo byte per essere trasmessi, per cui in ricezione da un byte ricevuto sono ricavati due campioni su 10 bit.