La tecnica del pin sharing per interfaccia I2C analizzata nei dispositivi C8051F30x.

I C8051F30x sono dispositivi dotati di periferica analogica per la conversione A/D a 8 bit. Le caratteristiche principali di questi dispositivi possono essere riassunti nel seguente modo:

» 8 bit ADC con tempo di S/H fino a 500 ksps;

» comparatori programmabili;

» oscillatore interno di 24.5 Mhz;

» periferica digitale: 8 I/O port 16 bit programmabile;

» microprocessore High speed 8051;

» interfaccia 2-Wire (I2C).

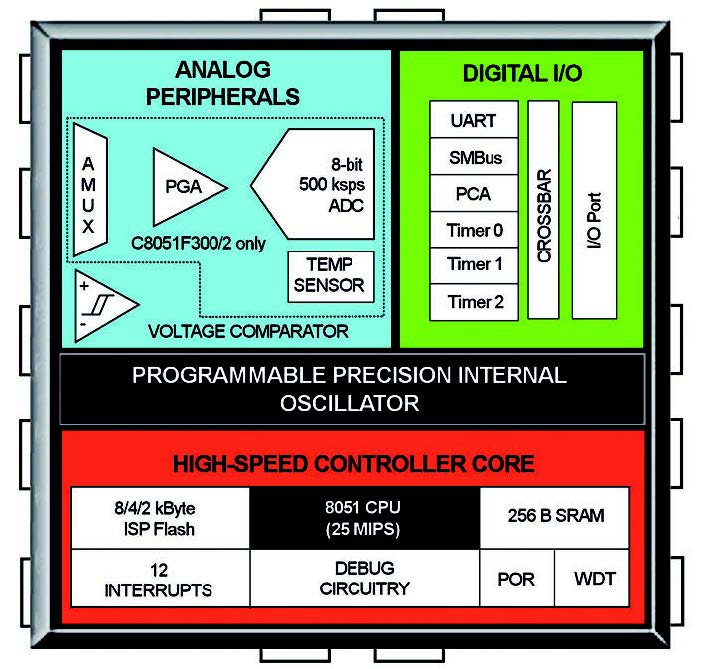

In figura 1 lo schema a blocchi del dispositivo descritto.

Figura 1: C8051F30x.

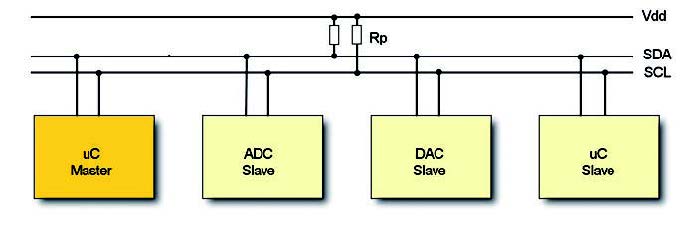

I2C, acronimo di Inter Integrated Circuit (figura 2), è un sistema di comunicazione seriale bifilare utilizzato tra circuiti integrati.

Figura 2: Bus I2C.

E’ composto da almeno un master ed uno slave. Il bus è stato sviluppato dalla Philips nel 1982 e dopo la realizzazione di centinaia di componenti e sistemi negli anni ‘80, nel 1992 è stato rilasciata la prima versione del protocollo che ha subìto diversi aggiornamenti ed ha generato bus simili, uno dei quali SMBUS. Il protocollo hardware dell’I2C richiede due linee seriali di comunicazione:

- SDA (Serial Data line) per i dati

- SCL (Serial Clock Line) per il clock (per la presenza di questo segnale l’I2C è un bus sincrono).

Va aggiunta una connessione di riferimento e una linea di alimentazione a cui sono connessi i resistori di pull-up che può anche non essere condivisa da tutti i dispositivi (le tensioni tipiche usate sono +5 V o +3,3 V anche se sono ammesse tensioni più basse o più alte). Il C8051F30x include una interfaccia 2-Wire (I2C) che permette la programmazione veloce del processore e il debugging del sistema. Il bus opera utilizzando 2 pin: un pin bidirezionale per dati (C2D) e un segnale di clock (C2CK). Per abilitare alcune funzioni del dispositivo I2C resistori esterni devono essere usati per isolare il traffico dei dati dal dispositivo esterno connesso al bus. La configurazione di isolamento (pin sharing), che vedremo successivamente, dipende dal tipo di operazione che l’utente richiede associata ai pins /RST a P0.7. Durante la comunicazione, questi pins sono utilizzati dall’interfaccia I2C.

Il 2-Wire Interface

L’I2C ha 7 bit di indirizzo e quindi 128 possibili indirizzi diversi (detti nodi). Di questi però 16 sono riservati quindi i dispositivi che possono essere collegati sullo stesso bus sono al massimo 112. Le velocità di trasmissione nel modo standard sono di 100 kbit/s e 10 kbit/s velocità del lowspeed mode ma nulla impedisce di scendere a velocità più basse. Revisioni del I2C hanno introdotto dispositivi con velocità di 400 kbit/s (detto fast mode e 3,4 Mbit/s detto High Speed mode). Anche le possibilità di indirizzamento di dispositivi sono state ampliate a 10 bit. Il massimo numero di nodi oltre ad essere limitato dal numero di indirizzi possibili diversi è limitato dalle capacità parassite introdotte da ciascun dispositivo. La capacità totale presentata da SDA e da SCL deve essere limitata a 400 pF (i resistori di pull-up dovranno essere dimensionati su questo dato, cioè la massima capacità dovuta alla somma dei dispositivi connessi, oltre al limite della corrente che ogni dispositivo può assorbire al livello logico basso). Ogni dispositivo collegato a queste linee è dotato di un indirizzo univoco, di 7 o 10 bit e può agire sia da master che da slave, secondo le funzioni previste al suo interno. Il master si occupa di iniziare la trasmissione e di generare la tempistica del trasferimento, mentre lo slave è quello che riceve una richiesta. Entrambe le due categorie possono assumere il ruolo di trasmittente o ricevente. Le modalità di trasferimento dati possono essere riassunte come segue:

- A trasmette dati a B

- 1- A(master) spedisce l’indirizzo di B(slave) sul bus

- 2- A (master-transmitter) trasmette i dati a B (slave-receiver)

- 3- A termina il trasferimento

- A vuole ricevere dati da B

- 1- A (master) spedisce l’indirizzo di B(slave) sul bus

- 2- B (slave-transmitter) spedisce i dati ad A (master-receiver)

- 3- A termina il trasferimento

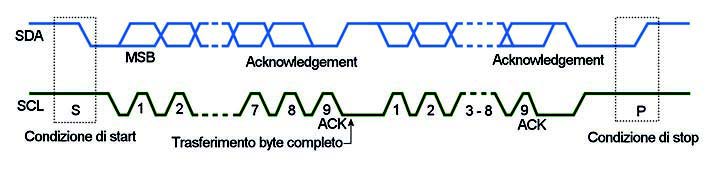

Un esempio di trasmissione completa utilizzando il protocollo i2c è quello che compare in figura 3.

Figura 3: andamento dei segnali SDA e SCL.

In particolare si fa riferimento a dispositivi con indirizzo lungo sette bit. La trasmissione inizia con la generazione di un segnale di start, immesso sulla linea dal master, dopo un controllo sull’occupazione del bus. La condizione di start consiste nel lasciare la linea “scl” allo stato “alto”, mentre la linea “sda”, subisce una transizione dallo stato ‘1’ allo stato ‘0’. Nella figura 3 è rappresentata la condizione di start nella parte a sinistra. Dopo la generazione del segnale di start inizia la trasmissione dei dati vera e propria. Il primo byte trasmesso è quello composto dall’indirizzo dello slave con l’aggiunta di un ulteriore valore che indica al ricevente quale è l’operazione a lui richiesta. In base allo standard previsto dal protocollo questo bit può assumere due valori con i seguenti significati:

- ‘0’: ricezione dati;

- ‘1’: trasmissione dati;

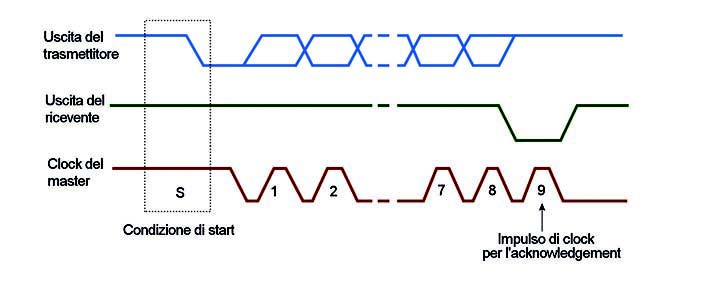

L’ordine di trasmissione dei bit è quello dal più significativo al meno significativo. Le successive comunicazioni seguono sempre quest’ultimo criterio. Dopo la trasmissione d’ogni byte chi trasmette ha l’obbligo di lasciare la linea “sda” allo stato “alto”, in modo da permettere a chi riceve dei dati, di darne conferma tramite il meccanismo dell’acknowledgement: esso consiste nell’abbassare la linea “sda” in corrispondenza del nono impulso presente sulla linea “scl”. Un esempio del processo appena esposto lo si può vedere nella figura 4 così come è presente nella figura 3. Se l’acknowledgement non venisse generato, chi ha iniziato la trasmissione può interrompere la comunicazione utilizzando la condizione di stop. Un dispositivo può non generare il segnale di acknowledgement ad esempio, quando è inabilitato a ricevere, perché sta eseguendo delle funzioni in real-time, oppure quando non può più immagazzinare altri dati. Il segnale di stop è sempre generato dal master, come pure quello dello start. Esso consiste nel far variare la linea sda dallo stato “basso” a quello “alto” in corrispondenza del periodo “alto” della linea “scl”. Un esempio di questa condizione è visibile nella parte a destra della figura 4.

Figura 4: andamento dei segnali SDA e SCL.

Pin sharing

Analizziamo alcune configurazioni. La richiesta di isolamento dipende dalla direzione del segnale associato al pin: input, output o bidirezionale.

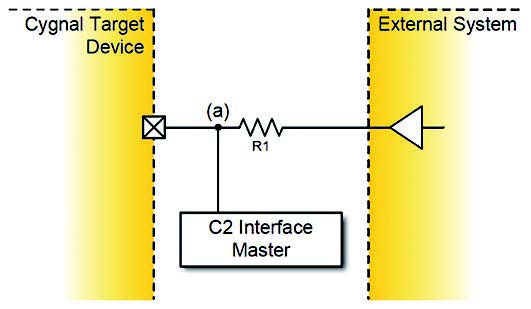

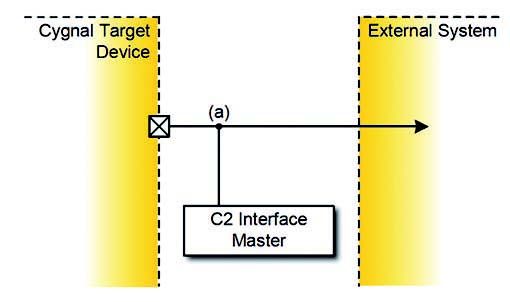

Input

Un pin è considerato un ingresso se il “target device” controlla la logica di livello del pin. In questo caso una sola resistenza è richiesta (figura 5).

Figura 5: pin sharing: input.

Il C2 interface Master controlla la logica di livello al nodo a durante la comunicazione I2C; la resistenza di isolamento assicura nessun conflitto tra il master I2C e il dispositivo esterno.

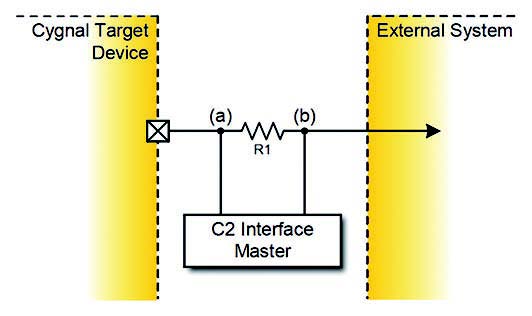

Output

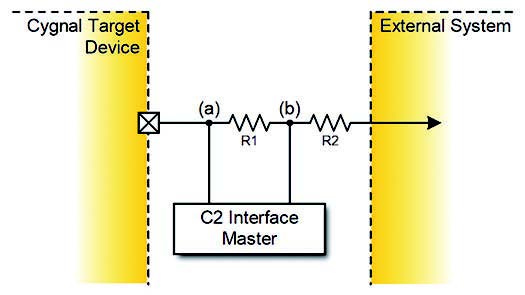

Un pin è considerato una sola uscita se il dispositivo esterno guida la logica del livello del pin. La tipica configurazione è visualizzata in figura 6.

Figura 6: pin sharing: output.

In questa configurazione la logica del livello vista dal sistema esterno non deve cambiare durante la comunicazione C2. L’interfaccia master può comunicare con il “target device” al nodo a mentre la resistenza R1 assicura che il si stema esterno non è disturbato.

Bidirezionale

Un pin è considerato bidirezionale se sia il “target device” che il sistema esterno possono controllare la logica di livello del pin. In questo caso sono richieste 2 resistenze di isolamento (figura 7).

Figura 7: pin sharing: bidirezionale caso 1.

La configurazione assicura che la logica di livello vista dal dispositivo esterno non cambia durante la comunicazione C2. Se è permesso il cambiamento della logica durante la comunicazione, la configurazione di pin sharing può essere eseguita con una sola resistenza (figura 8).

Figura 8: pin sharing: bidirezionale caso 2.