In questo articolo verrà descritto il modulo per la gestione del clock presente nella famiglia di microcontrollori AVR XMEGA di Microchip/Atmel, contraddistinti da un ottimo compromesso tra prestazioni e potenza assorbita.

XMEGA occupa un ruolo di primaria importanza all’interno della nota famiglia di microcontrollori AVR di Atmel, essendo caratterizzata da un ottimo compromesso tra assorbimento di corrente e livello di prestazioni offerte. I microcontrollori AVR XMEGA, a 8 e 16bit, si distinguono per le seguenti caratteristiche:

# tecnologia di tipo picoPower in grado di assicurare basso assorbimento di potenza;

# frequenza di clock fino a 32 MHz con alimentazione a 1,6 V;

# controllore DMA a 4 canali e sistema per la gestione degli eventi, il quale permette alle singole periferiche di inviare eventi (“signal”) direttamente ad altre periferiche, senza coinvolgimento da parte della CPU;

# convertitori ADC e DAC ad alta velocità con risoluzione di 12 bit (ADC a 2Msps e DAC a 1 Msps);

# motore integrato per la crittografia (supporta sia AES con chiave a 128-bit che DES con chiave a 64-bit), temporizzatori e contatori, interfacce di comunicazione ad alta velocità (USART, SPI, e Two Wire Interface, compatibile con I2C);

# sistema accurato e flessibile per la gestione del clock, dotato anche di protezione automatica verso i guasti del clock;

# elevato grado di compatibilità con gli altri componenti della famiglia AVR (tinyAVR e megaAVR), basati tutti sullo stesso core RISC AVR.

IL CLOCK SYSTEM DI AVR XMEGA

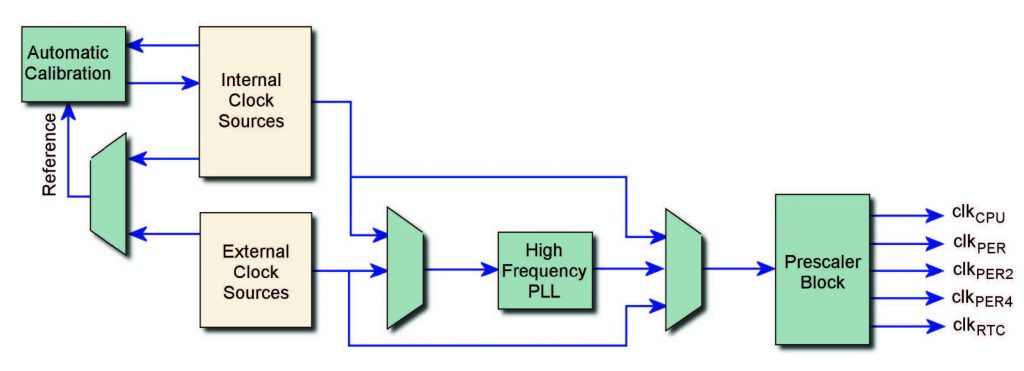

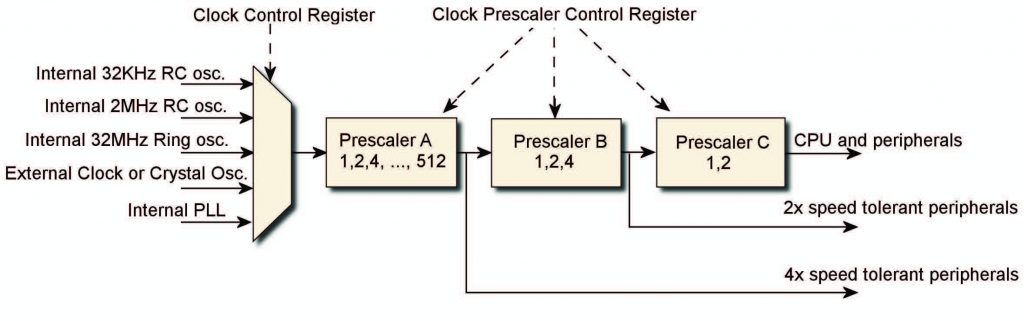

La famiglia XMEGA dispone di un sistema flessibile per la gestione del clock il quale consente di variare dinamicamente sia la frequenza che la sorgente del clock: il progettista dispone in questo modo di uno strumento potente con il quale può scegliere di volta in volta il giusto compromesso tra prestazioni e assorbimento di potenza. Tra le principali caratteristiche del Clock System ricordiamo la presenza di un PLL interno e di un prescaler tramite i quali è possibile aumentare o diminuire dinamicamente la frequenza di clock (sia per la CPU che per le periferiche), un circuito per il rilevamento dei guasti dell’oscillatore esterno, ed un oscillatore interno di tipo RC (sono disponibili le frequenza 32 KHz, 32MHz, e 2MHz) con un accuratezza fino a ±1% sia in temperatura che in tensione. L’oscillatore interno RC a 2MHz rappresenta l’oscillatore selezionato di default dall’hardware allo start-up e, a differenza degli oscillatori al quarzo o dei risonatori ceramici esterni, inizia ad oscillare in tempi molto ridotti con un’elevata precisione. Questa scelta consente di mandare subito in esecuzione il codice applicativo (dando il tempo necessario all’eventuale oscillatore esterno di portarsi a regime), e selezionare poi il clock definitivo tramite esplicite istruzioni nelfirmware (per diversi tipi di applicazioni, comunque, la scelta di default è di per sè già sufficiente ed in tal caso non è più necessario eseguire una differente programmazione del clock). La frequenza di clock può essere variata run-time agendo sul PLL e sui prescaler. Tramite il PLL interno, ad esempio, il segnale di clock può essere moltiplicato per un fattore da 1x fino a 31x, mentre il prescaler può essere impostato da 1x fino a 2048x. Sono inoltre presenti un modulo DFLL per effettuare la calibrazione run-time degli oscillatori interni, e la funzionalità “External Clock Source Failure Monitor” per rilevare eventuali malfunzionamenti o guasti relativi ai clock esterni (quando ciò avviene, il sistema seleziona automaticamente l’oscillatore interno a 2MHz). In figura 1 è mostrato lo schema a blocchi dell’XMEGA Clock System con evidenziati i componenti funzionali. Verranno ora analizzate le diverse sorgenti di clock e le opzioni di configurazione da applicare per poterle impiegare come sorgenti principali di clock.

Figura 1: schema a blocchi di XMEGA Clock System.

SORGENTI DI CLOCK INTERNE

Sono disponibili cinque diverse sorgenti di clock interne (incluso il PLL), da un oscillatore RC a 32 kHz e basso consumo fino a un oscillatore ad anello a 32 MHz con funzione di auto-calibrazione. Alcune sorgenti di clock possono inoltre essere impiegate come frequenza di riferimento per il PLL interno, in modo tale da generare frequenze anche superiori.

OSCILLATORE RC A 32 KHZ (ULP32K)

Questo oscillatore viene solitamente utilizzato per funzioni di sistema come cicli di ritardo, watchdog timer, real-time counter. Questa sorgente è l’unica a non poter essere impiegata come sorgente di clock di sistema, principalmente per via dell’accuratezza non elevata (30%). Questo oscillatore viene automaticamente abilitato dall’hardware quando necessario. La sua caratteristica rimarchevole è il basso assorbimento di potenza (Ultra Low Power).

OSCILLATORE RC CALIBRATO A 32 KHZ (RC32K)

E’ un oscillatore calibrato in fabbrica alla frequenza di 32,768 kHz con un’accuratezza pari a 1% alla tensione di 3V e temperatura di 25°C. Il valore di calibrazione viene automaticamente caricato nel registro RC32KCAL a seguito di ogni reset, ed è accessibile all’utente sia in lettura che in scrittura. Questo oscillatore può essere utilizzato direttamente come sorgente di clock di sistema ma anche (diviso tramite un prescaler interno fino a 1,024 kHz) come sorgente per il modulo real-time counter. Inoltre è utilizzabile come riferimento per la funzione di auto-calibrazione degli oscillatori interni a 2 e a 32 MHz.La configurazione di questo oscillatore viene attuata tramite il bit. L’abilitazione viene eseguita agendo sull’apposito bit RC32KEN del registro di controllo OSC.CTRL, mentre il bit di stato RC32KRDY del registro di stato OSC.STATUS indica quando l’oscillatore è pronto (stabile) per essere impiegato come sorgente di clock di sistema.

OSCILLATORE RC CALIBRATO A 2 MHZ (RC2M)

E’ un oscillatore RC calibrato in fabbrica alla frequenza di 2 MHz con un’accuratezza pari a 1% a 3V e 25°C. Il valore di calibrazione viene caricato nell’apposito registro interno ad ogni reset e può essere successivamente modificato dalla funzione di auto-calibrazione. L’oscillatore RC2M può essere utilizzato direttamente come sorgente di clock oppure tramite il PLL per generare frequenze anche superiori. L’abilitazione viene eseguita agendo sull’apposito bit (RC2MEN) del registro di controllo OSC.CTRL, mentre il bit di stato RC2MRDY del registro di stato OSC.STATUS va controllato per determinare quando l’oscillatore è stabile e pronto per l’utilizzo.

OSCILLATORE AD ANELLO CALIBRATO A 32 MHZ (R32M)

La calibrazione a 32 MHz è anch’essa eseguita durante la fabbricazione a 3V e 25°C e può essere modificata tramite la procedura di auto-calibrazione. Valgono le stesse considerazioni fatte relativamente all’oscillatore RC2M. L’abilitazione dell’oscillatore avviene tramite il bit R32MEN del registro di controllo OSC.CTRL, mentre il bit di stato R32MRDY indica quando esso è pronto per l’utilizzo come clock di sistema.

SORGENTI DI CLOCK ESTERNE

Sono disponibili diverse sorgenti di clock esterne, le quali utilizzano tutte i pin XTAL1 e XTAL2; ciò implica che solamente una tra queste sorgenti può essere attivata volta per volta. Un’eccezione è rappresentata dal Real-time Counter Oscillator che utilizza i pin TOSC1 e TOSC2 con un quarzo esterno come sorgente del modulo Real-time Clock e può venire impiegato direttamente come sorgente di clock di sistema.

QUARZI E RISONATORI CERAMICI (XOSC)

I pin XTAL1 e XTAL2 costituiscono l’ingresso e l’uscita, rispettivamente, di un amplificatore invertente che funge da oscillatore on-chip usando quarzi o risonatori ceramici esterni con frequenze da 0,4 a 16 MHz. L’oscillatore XOSC può essere configurato per una delle seguenti opzioni:

# oscillatore al quarzo da 32,768 kHz e basso assorbimento;

# quarzo o risonatore con frequenza 0,4 – 2 MHz;

# quarzo o risonatore con frequenza 2 – 9 MHz;

# quarzo o risonatore con frequenza 9 – 12 MHz;

# quarzo o risonatore con frequenza 12 – 16 MHz.

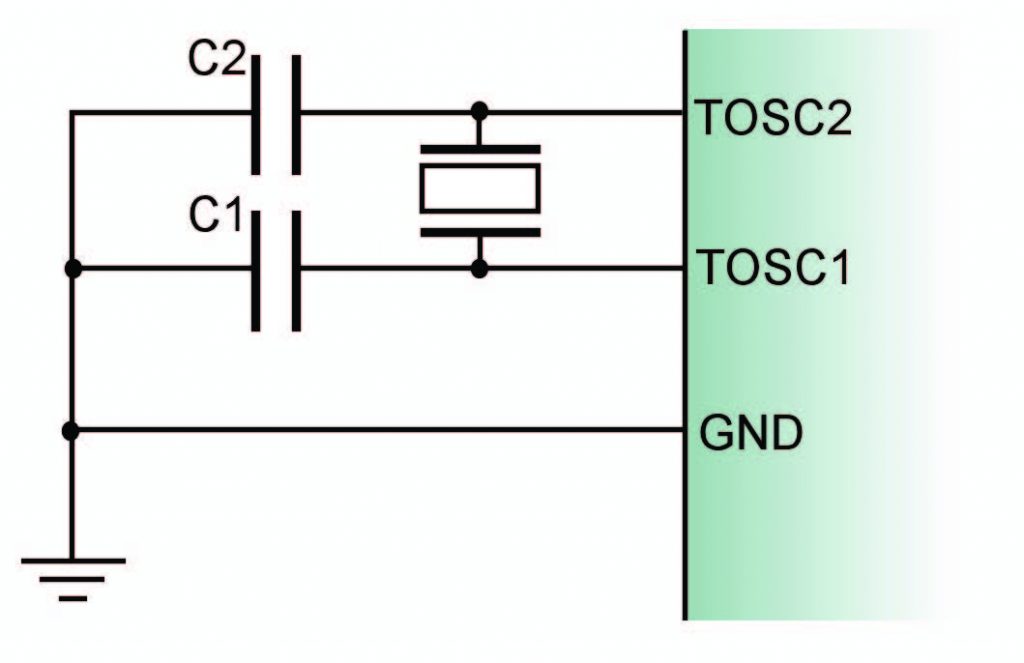

La selezione del tipo di oscillatore esterno, come pure il tempo di start-up avviene agendo sull’insieme di bit XOSCSEL del registro di controllo OSC.XOSCCTRL; l’abilitazione è resa possibile dal bit XOSCEN del registro di controllo OSC.CTRL, mentre il bit di stato XOSCRDY del registro OSC.STATUS permette di conoscere quando l’oscillatore ha raggiunto la stabilità. L’abilitazione deve essere l’ultima operazione eseguita, preceduta perciò dalla fase di configurazione: l’hardware non accetta infatti un cambiamento di configurazione mentre esso si trova già abilitato. In figura 2 è mostrato lo schema di collegamento di un oscillatore al quarzo esterno, mentre in figura 3 è indicato il collegamento sui pin TOSC1,2 di un oscillatore al quarzo esterno da 32,768 kHz.

Figura 2: connessione di un oscillatore al quarzo.

Figura 3: oscillatore esterno da 32,768 kHz.

CLOCK ESTERNO

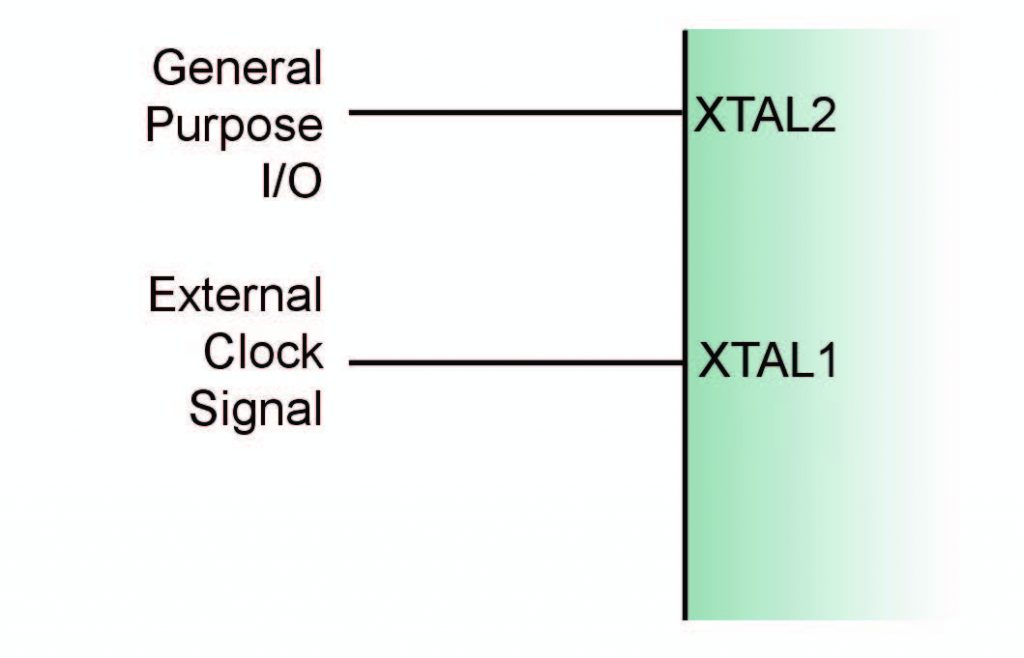

Per utilizzare un clock esterno, occorre collegarlo al pin XTAL1 e disabilitare l’oscillatore al quarzo on-chip. La selezione avviene impostando opportunamente i bit XOSCSEL nel registro OSC.XOSCCTRL, e viene sempre adottato un tempo di start-up pari a 6 cicli di clock prima di riportare l’oscillatore come stabile tramite il bit XOSCRDY del registro OSC.STATUS. Per ottenere un corretto funzionamento, la frequenza di clock non deve cambiare più del 2% tra un ciclo e l’altro; in caso contrario, l’XMEGA andrà tenuto in reset durante il tempo di variazione. In figura 4 è indicato lo schema di collegamento relativo al clock esterno il pin XTAL2 può essere utilizzato in tal caso come general purpose I/O).

Figura 4: collegamento di un clock esterno.

PLL PER FREQUENZE ELEVATE

Se è necessario ottenere frequenze più elevate, può essere utilizzato un PLL per moltiplicare una sorgente di clock per un fattore compreso tra 1 e 31. Le possibili sorgenti di clock sono le seguenti:

# oscillatore interno RC a 2 MHz;

# oscillatore ad anello a 32 MHz diviso internamente per quattro;

# oscillatore al quarzo esterno da 0,4 – 16 MHz;

# clock esterno.

Prima di abilitare il PLL, occorre accertarsi che la sorgente di clock in ingresso sia stabile. Si tenga presente che una volta abilitato, il PLL richiede 64 cicli del clock di riferimento prima di stabilizzarsi, e non è possibile modificare “on-the-fly” la configurazione del PLL (occorre prima disabilitarlo e poi modificare le impostazioni). Il circuito PLL accetta un riferimento di frequenza minima pari a 0,44 MHz, mentre non è possibile superare il valore massimo di 200 MHz.

SELEZIONE DEL CLOCK DI SISTEMA E PRESCALER

Tutte gli oscillatori interni calibrati, le sorgenti di clock esterne (XOSC) e l’uscita del PLL possono essere utilizzate com sorgente del Clock System, Al fine di offrire la massima flessibilità e versatilità possibile, l’XMEGA Clock System contiene un MUX in grado di selezionare una tra le sorgenti di clock del PLL (si veda al proposito la figura 5).

Figura 5: selezione del clock di sistema e prescaler

Il blocco prescaler può essere configurato per dividere il segnale di clock per un fattore tra 1 e 2048 prima di inviarlo alla CPU e alle periferiche. Può inoltre generare un segnale con frequenza pari a due o quattro volte quella della CPU per tutte quelle perfieriche che operano a frequenze maggiori della CPU (come ad esempio il modulo EBI che lavora a una frequenza doppia della CPU). Come visibile in figura 5, l’uscita del MUX passa attraverso tre stadi prescaler: il primo stadio A può dividere per un fattore da 1 a 512, mentre gli stadi B e C possono essere configurati sia per lasciare passare inalterato il segnale, che per dividerlo fino a un fattore 4. Il prescaler C è inoltre in grado di dirigere il segnale in uscita anche verso la CPU, oltre che alle perfiferiche. La configurazione di default successiva al reset prevede che sia selezionato l’oscillatore interno RC da 2 MHz e che questo passi senza essere diviso attraverso tutti gli stadi del prescaler. Lo stadio A ben si presta a dividere la frequenza anche per un fattore elevato, al fine di ridurre sensibilmente l’assorbimento di potenza, mentre gli stadi B e C sono adatti a generare un segnale di clock una, due, o quattro volte pari alla frequenza della CPU per le periferiche. L’impostazione del prescaler può essere modificato in qualunque momento, essendo l’hardware progettato per consentire una transizione regolare tra le due frequenze.

LOCK DELLA CONFIGURAZIONE

Dopo aver configurato il clock in base alle specifiche esigenze dell’applicazione, è possibile “bloccare” l’impostazione corrente fino al successivo reset al fine di evitare una riprogrammazione accidentale ed indesiderata. Se però la funzione di rilevamento dei guasti dell’oscillatore esterno è stata abilitata, un eventuale failure dello stesso forzerà lo “sblocco” della configurazione del Clock System.

MODALITÀ SLEEP

La famiglia di microcontrollori XMEGA dispone delle seguenti modalità di funzionamento sleep:

# idle: tutte le periferiche funzionano normalmente, il firmware non viene eseguito, qualunque periferiche può risvegliare il dispositivo, sia il DMA che il sistema di gestione degli eventi sono attivi;

# power save: l’RTC è attivo, ed il dispositivo può essere risvegliato dal real time clock, dagli interrupt esterni, dal TWI Address Match e dal watchdog timer; power down: nessun clock è attivo ed il firmware non viene eseguito. Il dispositivo può essere risvegliato dagli interrupt esterni, dal TWI Address Match e dal watchdog timer;

# standby: è come il power down, solo che l’oscillatore è mantenuto attivo per accelerare il wake-up;

# extdended standby: è come il power save, solo che l’oscillatore è mantenuto attivo per accelerare il wake-up.

Tutti gli oscillatori vengono disabilitati nelle modalità sleep power-down e sleep power-save, ad eccezione del Real-time Counter che rimane abilitato anche in modo Power-save in modo tale da mantenere attiva la sorgente di clock per l’RTC. Se però l’utilizzo dell’RTC non è richiesto, è consigliabile selezionare la modalità sleep power-down. Nelle modalità sleep Standby ed Extended Standby, come anche in modo idle, invece, gli oscillatori vengono mantenuti attivi, permettendo alla CPU di uscire dallo stato sleep senza ritardi aggiuntivi.

CIRCUITO PER IL RILEVAMENTO DEI GUASTI

Quando si utilizzano sorgenti di clock estene, esiste sempre una piccola probabilità che la sorgente si guasti. Come misura precauzionale, il Clock System di XMEGA dispone di un circuito che controlla continuamente la sorgente esterna di clock ed adotta le opportune azioni nel caso questa si interrompa. Se la sorgente esterna rappresenta la sorgente primaria di clock, in caso di guasto il circuito commuta automaticamente sull’oscillatore RC interno a 2 MHz e genera un NMI (di tipo XOSCF). Se invece la sorgente esterna è abilitata ma non selezionata come sorgente di clock primaria, questa verrà disabilitata e generato comunque un NMI. Il circuito di rilevamento dei guasti utilizza l’oscillatore ULP per monitorare la sorgente esterna, ed interviene se la frequenza scende sotto a 32 kHz. Quando questa funzionalità viene abilitata, è necessario implementare un’opportuna routine di risposta all’interrupt NMI.

CALIBRAZIONE AUTOMATICA DEGLI OSCILLATORI INTERNI

La calibrazione automatica run-time dell’oscillatore RC a 2 MHz e dell’oscillatore ad anello a 32 MHz avvengono tramite l’utilizzo di due Digital Frequency-locked Loop (DFLL) che possono essere configurati individualmente per impiegare come riferimento sia l’oscillatore inerno RC a 32 kHz che un oscillatore esterno al quarzo da 32 kHz. Quando si entra in modalità sleep, il loop di calibrazione viene interrotto per poi riprendere dallo stesso stato quando si esce nuovamente dalla modalità sleep. Se inoltre un DFLL viene disabilitato, viene mantenuto il corrente valore di calibrazione fino al momento in cui il DFLL viene nuovamente abilitato.

La possibilità di disporre di diverse sorgenti di clock è un vantaggio considerevole per il progettista, il cui può scegliere volta per volta la soluzione più adatta alle specifiche esigenze dell’applicazione e ai requisiti di precisione imposti.

La famiglia di microcontrollori XMEGA possiede molti vantaggi, come nuove periferiche evolute, un set di istruzioni esteso e bus dati interno a 16 bit.