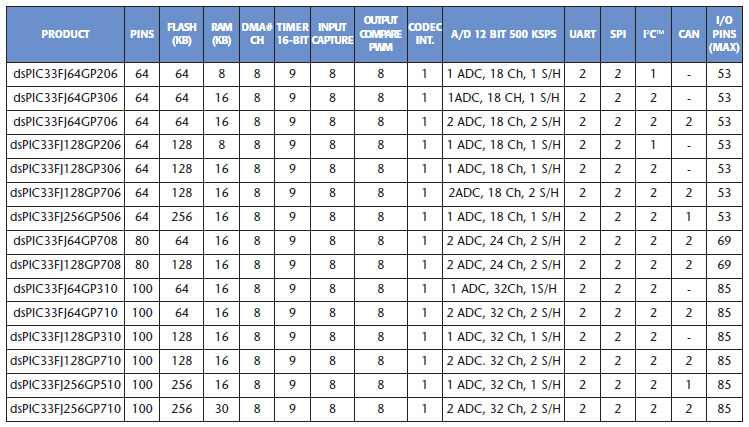

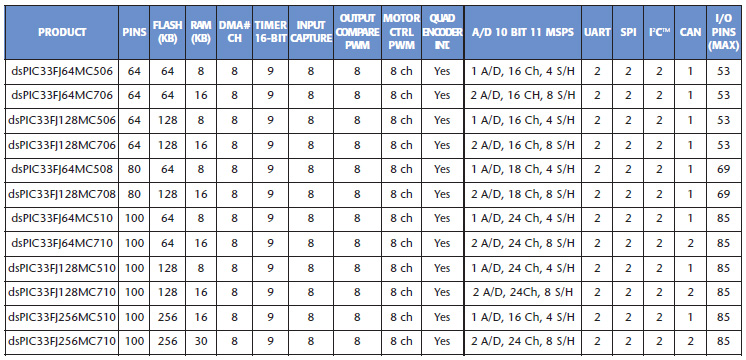

Una analisi dettagliata dell’architettura interna del DSC (Digital Signal Controller) dsPIC33F di Microchip: un single chip con funzioni DSP ad elevate prestazioni per controllo industriale e sistemi audio. I DSC integrano al loro interno un potente microcontrollore 16bit e un DSP. La famiglia dsPIC33F comprende due categorie, la prima con una periferica CODEC per applicazioni audio o di riconoscimento vocale. La seconda comprende una periferica PWM a otto canali e si adatta ad applicazioni industriali per controllo motore o sistemi di conversione di potenza. Le tabelle 1 e 2 elencano i dettagli delle due famiglie con i principali IC.

Introduzione

I dsPIC33F raggiungono velocità di 40Mips, la dimensione della memoria flash può arrivare a 256Kbyte mentre la memoria RAM a 30KByte. Tutti i dispositivi includono le periferiche di comunicazione più comuni come UART SPI e I2C. Su alcune versioni sono presenti 1 o 2 periferiche CAN configurabili secondo la specifica 1.2, 2.0A, 2.0B. Completano la dotazione il convertitore A/D completamente configurabile per acquisizione a 10 o 12 bit con un massimo di 32 ingressi, l’oscillatore interno e un controller DMA con bus dedicato, per il trasferimento dati tra periferiche e memoria RAM senza impegnare la CPU. L’alimentazione del dsPIC33F è a 3.3V ma gli ingressi digitali sono 5V tolerant.

LE CARATTERISTICHE PRINCIPALI

La CPU

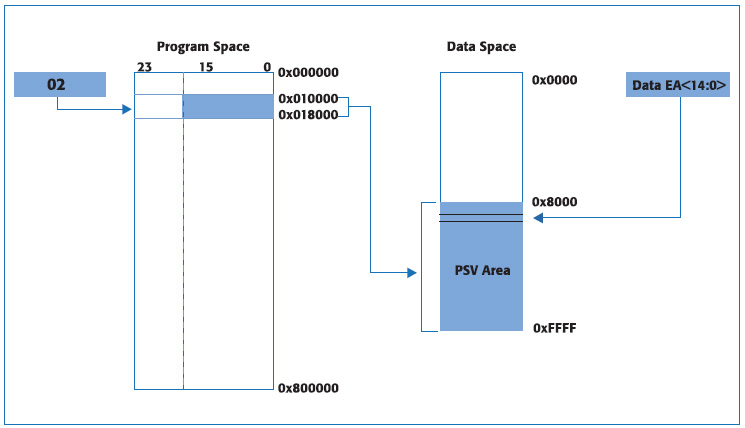

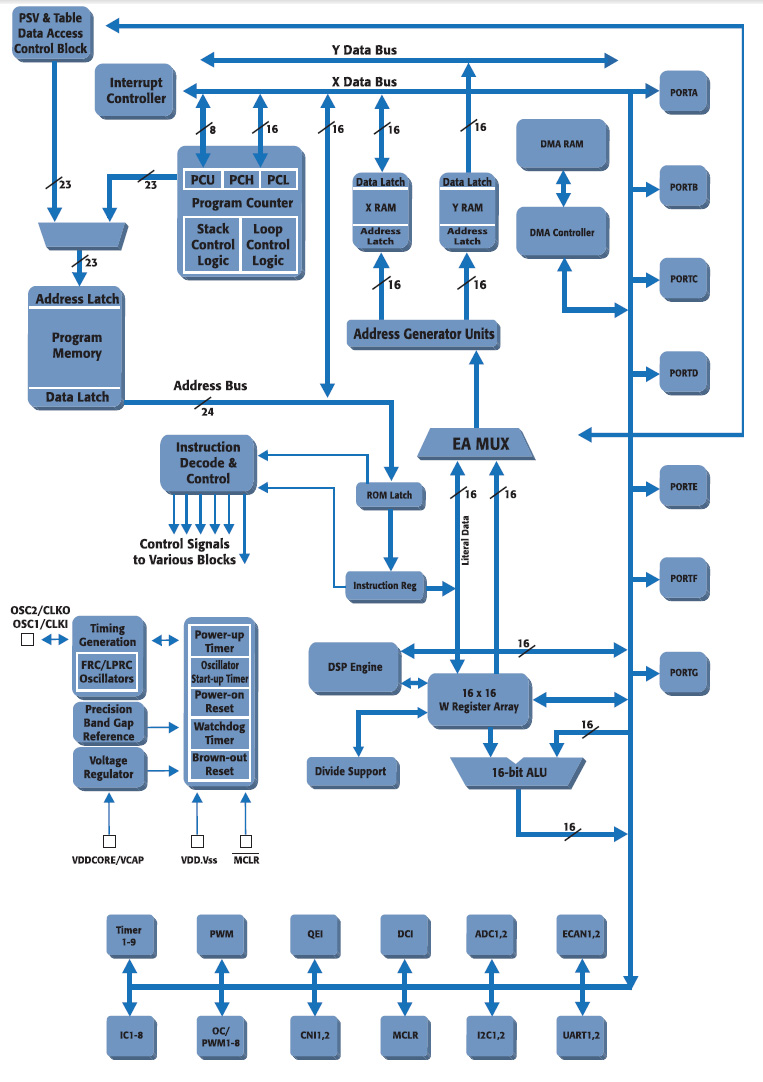

Il dsPIC33F è un dispositivo con architettura Harvard modificata: memoria dati (RAM) e programma (Flash) sono separate ed accessibili mediante due bus distinti. Lo spazio indirizzabile nella memoria flash è di 4Mb con accesso a 24bit. In realtà l’allineamento delle word è a 32bit ma il byte alto della upper word non è implementato. I 2MB inferiori sono disponibili per l’indirizzamento di memoria programma mentre i 2MB superiori sono riservati per l’accesso a registri di configurazione del dispositivo. L’architettura Harvard modificata consente la presenza di dati anche all’interno della memoria programma. L’accesso a questi dati può avvenire in due modi: utilizzando le instruction table oppure modificando la mappatura dello spazio dati. Le instruction table sono istruzioni dedicate per la lettura/scrittura delle word della memoria flash. Queste istruzioni sono utilizzate anche nella programmazione della memoria flash. La mappatura della memoria invece abilita la visibilità di una pagina della memoria flash nei 32Kbyte superiori dello spazio dati. Questa tecnica permette di accedere a dati statici o tabelle di setup memorizzate nella memoria flash. L’accesso a 24bit nello spazio programma si ottiene unendo un registro di pagina a 8 bit, che rappresenta la parte alta dell’indirizzo e definisce la pagina di 16Kword di flash visibile nello spazio dati, con i 15bit inferiori dell’indirizzo dello spazio dati. Un’altra interessante caratteristica del dsPIC33F è la possibilità di programmare la memoria flash in-circuit con una semplice interfaccia tre pin Data/Clock/Reset.

La memoria RAM è invece accessibile a 16bit per uno spazio totale di indirizzamento a 64Kbyte. I 32Kbyte inferiori sono riservati alla memoria RAM, i 32Kbyte superiori sono riservati per il program memory visibility descritto in precedenza. Per l’accesso al data space ci sono due blocchi d’indirizzamento indipendenti X e Y che permettono alla CPU l’accesso simultaneo a due operandi. In un solo ciclo la CPU del dsPIC33F può accedere in lettura alla memoria programmi e in lettura/scrittura alla memoria dati. La CPU include anche un motore DSP costituito da un moltiplicatore 17x17 bit in grado di svolgere moltiplicazioni con e senza segno, un barrel shifter che può eseguire lo shift di una word in un ciclo e un’unità somma/sottrazione a 40bit con due accumulatori. Rispetto al suo predecessore dsPIC30F sono stati introdotti dei nuovi bit per il controllo dell’errore di overflow nel calcolo aritmetico, nelle operazioni di shift o divisione. Contrariamente a quanto avviene per i bit d’errore della CPU questi bit di stato una volta attivati restano attivi anche se si eseguono nuove operazioni matematiche. Solo cancellando il flag MATHERR la condizione di errore viene rimossa. Il flag MATHERR può generare un trap interrupt per attivare una procedura di recovery dall’errore.

Il DMA

Il DMA controller permette di trasferire dati in diverse modalità tra la RAM del dsPIC33F e le periferiche utilizzando un bus dedicato che non interferisce con la CPU. Le modalità di trasferimento sono:

- One-shot block transfer che trasferisce un singolo blocco dati;

- Continuous block transfer che trasferisce un determinato buffer in modo ciclico riprendendo dallo start address una volta raggiunto il termine del buffer;

- PingPong transfer che utilizza alternativamente due buffer distinti mappati sulla ram DMA per il trasferimento dei dati.

Il controller include otto canali configurabili separatamente per diverse modalità di trasferimento dati. In caso di collisione il canale con numero più basso guadagna l’accesso alle risorse. Il DMA controller e la CPU condividono una dual port RAM da 2Kbyte che permette l’accesso contemporaneo ai dati. Il bit DMAFLT segnala condizioni di errore o collisione nell’accesso alla RAM da parte del DMA e della CPU (figura 3).

L’Interrupt controller

La tabella di interrupt del dsPCI33F è formata da 118 vettori di interrupt e 8 vettori non mascherabili associati ai trap flag che sono attivati in presenza di un errore. Il DSC implementa 67 interrupt diversi. Gli interrupt possono essere abilitati singolarmente e ad ogni vettore è possibile associare 8 livelli di priorità gestita poi dall’interrupt controller. La priorità zero disabilita l’interrupt mentre la priorità 7 rappresenta la priorità massima. Se ci sono due o più interrupt contemporanei con la stessa priorità il vettore di indice più basso viene eseguito per primo. I trap interrupt non sono mascherabili e occupano i primi vettori della tabella di interrupt. Ogni trap interrupt è associato ad una condizione di errore. Nel dsPIC33F sono stati implementati i seguenti trap:

- Oscillator fault

- Address error

- Stack error

- Math error

- DMA error

La routine associata alla trap qualora sia inutilizzata deve comunque cancellare l’error flag che ha generato la trap. Il circuito di clock Ci sono quattro sorgenti possibili per il clock del DSC:

- un oscillatore RC interno denominato FRC (Fast RC oscillator) con frequenza nominale a 7.37MHz;

- un oscillatore primario in grado di accettare in ingresso quarzi fino a 40MHz oppure un segnale di clock esterno;

- un oscillatore secondario a cui può essere collegato un quarzo a 32KHz o un risonatore ceramico (quest’ultima soluzione è adatta per applicazioni low power).

- Un secondo oscillatore RC interno denominato LRC (Low RC oscillator) con frequenza di 32.768KHz.

Per rendere più flessibile la scelta della frequenza di sistema le uscite dell’FRC e dell’oscillatore primario possono essere applicati ad un PLL in grado di generare frequenze tra 25 e 160MHz partendo da una frequenza d’ingresso compresa tra 1,6MHz e 16MHz. L’uscita dell’oscillatore o del PLL viene poi divisa per 4 per ottenere la frequenza di sistema (figura 4 e 5).

Periferiche di comunicazione

Come accennato all’inizio il DSC include moltissime periferiche di comunicazione. Tutti i modelli della famiglia dsPIC33F includono due UART, due periferiche SPI e due periferiche I2C. In alcuni modelli (tabelle 1 e 2) sono presenti anche una o due periferiche CAN. La UART è full duplex con il controllo hardware del flusso di comunicazione mediante pin dedicati RTS/CTS. La UART è bufferizzata con due FIFO a quattro livelli sia per la trasmissione che per la ricezione. Il baudrate può raggiungere 1Mbit con clock di sistema a 16Mips. L’hardware della periferica include anche la logica per comunicazione secondo lo standard IrDA. Le linee RX e TX della porta in modalità IrDA si collegano direttamente al trasmettitore e ricevitore a infrarossi. Le due periferiche SPI possono funzionare sia in modalità master che slave. I dati transitano in un doppio buffer di ricezione/trasmissione e possono essere trasferiti a 8bit o 16bit. Anche per questa periferica è possibile prevedere il trasferimento in DMA da e per la RAM del dsPIC33F. In modalità master il clock per la periferica SPI è ricavato dal clock di sistema del DSC tramite un doppio prescaler in cascata che consente di ottenere fino a 20 frequenze diverse. Anche le periferiche I2C sono completamente configurabili per funzionamento salve o multimaster, indirizzamento a 7 o 10 bit, frequenza di clock a 100KHz o 400KHz. La logica hardware dell’interfaccia include anche il controllo per bus multimaster che termina automaticamente la comunicazione quando rileva un conflitto sul bus I2C e un registro di mask per l’indirizzo slave che permette di assegnare alla periferica un range d’indirizzi anziché ad un indirizzo univoco. La periferica CAN è presente solo su alcuni modelli del DSC. Il modulo CAN supporta CAN1.2, CAN2.0A e CAN2.0B passivo/attivo. La periferica è analoga a quella del dsPIC30F.

Convertitore analogico digitale

Nel DSC possono essere presenti 1 o 2 periferiche di conversione analogica digitale. Le caratteristiche del convertitore sono: convertitore SAR con velocità di conversione a 1,1Msps per la risoluzione a 10bit e 500Ksps per la versione a 12bit. Gli ingressi analogici dipendono dal modello del DSC considerato e variano da 18 a 32 configurabili sia come single ended che come differenziali. Quando si configura il convertitore per funzionamento a 10bit è possibile utilizzare quattro circuiti di sample&hold per quattro acquisizioni contemporanee.

Power saving

Il dsPIC33F include tre modalità di funzionamento in basso consumo: sleep, idle e doze. Le prime due sono le condizioni classiche presenti in ogni microcontrollore. La modalità sleep ferma l’oscillatore del micro riducendo pertanto i consumi al minimo mentre la modalità idle mantiene l’oscillatore acceso bloccando solamente l’attività della CPU. In modalità doze invece, si riduce di un fattore prestabilito solamente il clock della CPU, che non viene fermata, lasciando inalterato il clock delle periferiche. In questo modo è possibile mantenere la completa funzionalità delle periferiche di comunicazione o di acquisizione A/D riducendo però i consumi della CPU.

Sistemi di sviluppo e librerie software

Il dsPIC33F è supportato dall’IDE integrato MPLAB che comprende assemblatore e linker. Per utilizzare il linguaggio C è necessario il compilatore ANSI MPLABC30 acquistabile separatamente. L’IDE MPLAB comprende anche dei tools molto utili come il simulatore e il VDI (Visual Device Initializer) che permette di configurare in modo visuale tutte le periferiche del DSC generando poi automaticamente il software di inizializzazione del componente. Completa anche la dotazione di librerie software fornite gratuitamente che includono funzioni matematiche trigonometriche, filtri FIR, IIR, calcolo vettoriale, FFT. Altre librerie per la gestione segnale vocale e crittografia dei dati sono invece disponibili a pagamento.

La serie di questi MCU trova spazio anche nel controllo motori, cosi come lo sviluppo di algoritmi di filtraggio dati. Il 16 bit permette buone performance cosi come il core DSP che sfrutta le potenzialita’ matematiche.