La famiglia LPC2000 è una serie di microcontrollori (NXP) basati su una CPU a 16/32 bit ARM7tdmi-s™; sono progettati per l’uso in una vasta gamma di applicazioni che richiedono elevate prestazioni con basso consumo di energia.

L’architettura del LPC2000 consiste in una CPU a 16/32 bit ARM7TDMIS ™ con emulazione in tempo reale e supporto di traccia embedded. Un’interfaccia di memoria estesa a 128 bit e un’architettura unica dell’acceleratore permettono l’esecuzione di codici a 32 bit a frequenza di clock massima. Per le applicazioni con dimensioni di codice critiche, la modalità alter nativa a 16 bit Thumb™ riduce il codice di oltre il 30% con penalizzazione minima delle prestazioni. Grazie al loro formato molto piccolo e al basso consumo di energia, questi microcontrollori sono ideali per le applicazioni in cui la miniaturizzazione è un requisito fondamentale. Le caratteristiche principali dei controllori LPC2000 possono essere riassunte nel modo seguente:

➤ processore ARM7DMI-S 16/32 bit;

➤ RAM statica su chip fino a 8/16/32/40/64 kB;

➤ programmazione su sistema (ISP) e programmazione su applicazione (IAP) tramite software bootloader integrato su chip;

➤ controllore di interrupt vettorizzato con priorità e indirizzi di vettore configurabili;

➤ l’interfaccia embedded ICE-RT abilita punti di arresto e di controllo. Le routine di servizio di interrupt possono continuare ad essere eseguite, mentre il debug delle operazioni a priorità alta è eseguito dal software integrato su chip RealMonitor™;

➤ l’interfaccia Embedded Trace Macrocell permette una tracciatura in tempo reale ad alta velocità non intrusiva dell’esecuzione di istruzione;

➤ interfacce seriali multiple.

La CPU ARM7 utilizza la tecnologia pipeline per l’esecuzione delle istruzioni. La pipeline è una tecnologia utilizzata dai microprocessori per incrementare la quantità di istruzioni eseguite in una data quantità di tempo. Fondamentalmente l’elaborazione di un’istruzione da parte di un processore con pipeline si compone di cinque passaggi fondamentali:

➤ lettura dell’istruzione da memoria;

➤ decodifica;

➤ esecuzione dell’istruzione;

➤ attivazione della memoria;

➤ scrittura del risultato.

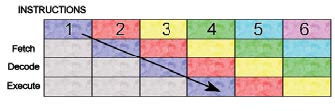

ARM7 è basata su tre livelli di pipeline per processare le istruzioni: pipeline di tipo fetch, decode ed excute (figura 1).

Figura 1: pipeline.

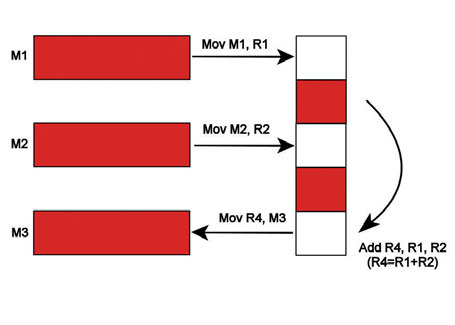

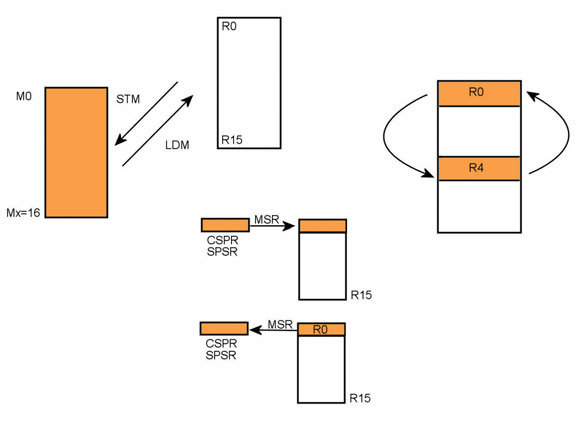

L’ARM7 è un tipo di architettura loadstore. I dati vengono caricati da una memoria centrale in un set di registri (memoria secondaria), quindi vengono eseguite le varie istruzioni di processamento di dati. Successivamente i dati sono riportati nella memoria centrale (figura 2).

Figura 2: architettura load-store.

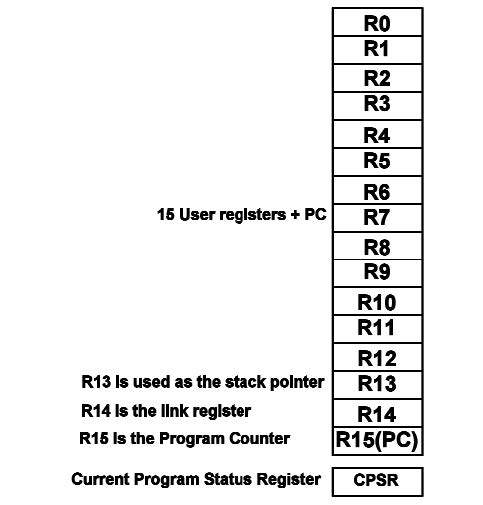

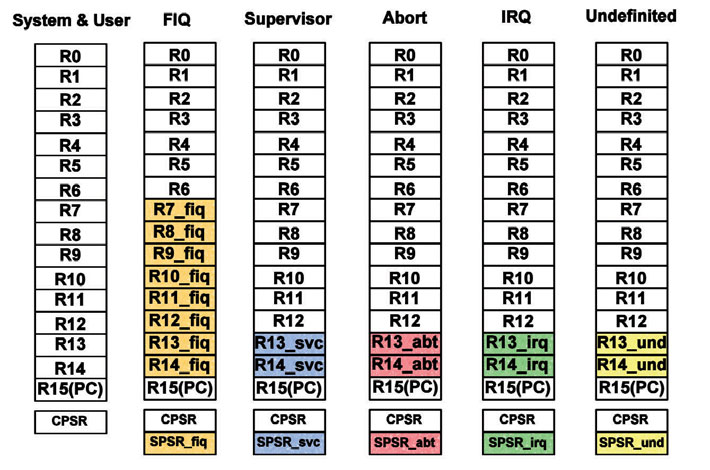

Il set di registri sono costituiti da 16 registri di 32 bit di cui alcuni utilizzati per funzioni speciali del microprocessore, gli altri a disposizione per l’utente (figura 3).

Figura 3: il set di registri (memoria secondaria)

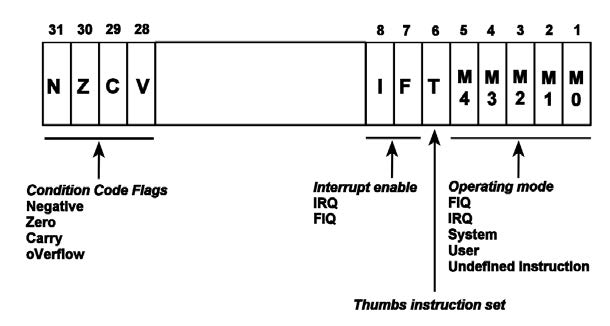

Da R0 a R12 abbiamo registri senza un particolare scopo, registri quindi di uso generale. I registri che invece vanno da R13 a R15 sono di vitale importanza per il corretto funzionamento della CPU: R13 è lo stack pointer, R14 il link register e R15 il PC program counter. Esiste anche un altro registro importantissimo nell’ARM7, il CPSR, registro a 32 bit contenente delle flag le quali monitorano il funzionamento del processore e sono in grado di settare particolari opzioni (figura 4).

Figura 4: CPSR.

Gli ultimi 4 bit rappresentano le condizioni di flag: negative, zero, carry e overflow. I bit 7 e 8 sono i bit che abilitano e disabilitano gli interrupt ester ni al processore. Occorre sottolineare che i due bit sono settati non con l’uno logico ma con lo zero. Tutte le periferiche esterne alla CPU sono connesse a queste due linee di interrupt. Il bit 5 è il cosiddetto THUMB bit grazie al quale il processore stabilisce se le istruzioni lette sono da interpretare come istruzioni ARM o THUMB. Se il bit T è posto a 1 allora l’istruzione è da considerarsi in THUMB mode (16 bit). I primi 5 bit determinano la modalità di funziona mento del processore: user, FIQ, Supervisor, Abort, IRQ, Undefined. Normalmente il funzionamento è in modalita user mode. In risposta ad un evento, come ad esempio un interrupt o un errore del la memoria, il processore cambia modalità di funzionamento e, da come è possibile vedere nella figura 5, i registri interni cambiano le loro funzioni.

Figura 5: SPSR (Saved program status register).

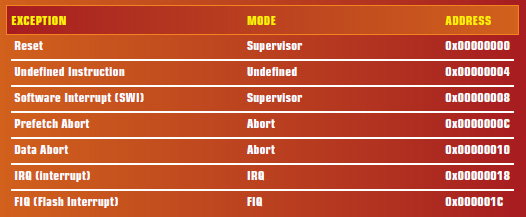

E’ possibile vedere come ogni modo di funzionamento abbia il proprio link register e il proprio stack pointer. Inoltre, tutti i modi di funzionamento che gestiscono le eccezioni hanno un registro aggiuntivo chiamato SPSR, Saved program status register. Al verificarsi dell’evento, l’intero CPSR è salvato nel SPSR. Questo fa si che, ultimata l’esecuzione del codice di reazione all’evento, il programma sia in grado di ripartire da dove si era fermato. Ci sono delle eccezioni che fanno cambiare modalità al processore. Ognuno degli eventi ha associato un vettore che rappresenta l’indirizzo al quale punta il PC immediatamente dopo il verificarsi dell’evento stesso. Ogni eccezione ha chiaramente una sua priorità, questo per gestire i conflitti nei casi in cui due eccezioni sopraggiungano contemporaneamente (tabelle 6 e 7).

Tabella 6: exception Modes.

Tabella 7: priorità.

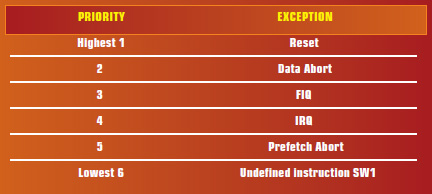

La famiglia del LPC2000 è costituita inter namente da diversi tipi di bus (figura 8):

■ 1-Local bus: per il trasferimento di codice.

■ 2-Advance High Permorfance Bus: utilizzato per connettere in maniera veloce le periferiche esterne all’ARM7 (AHB). Periferiche connesse direttamente a questo bus sono solamente il vector Interrupt controller (VIC), responsabile della gestione degli interrupt e 8Kbyte di memoria flash.

■ 3-VLSI Bus: per connettere Chip esterni alla CPU. Tutte le altre periferiche sono connesse alla CPU per mezzo di un altro bus connesso al primo con un bridge che include un divisore di frequenza, il VPB divider. Questo permette all’ARM di lavorare al massimo delle sue potenzialità lasciando alle periferiche una frequenza di funzionmento più bassa al fine di risparmiare sui consumi. Considerato che gli accessi in memoria durante l’esecuzione di un programma sono frequenti, in questo modo si riescono a evitare fastidiose collisioni che inevitabilmente rallenterebbero il processore.

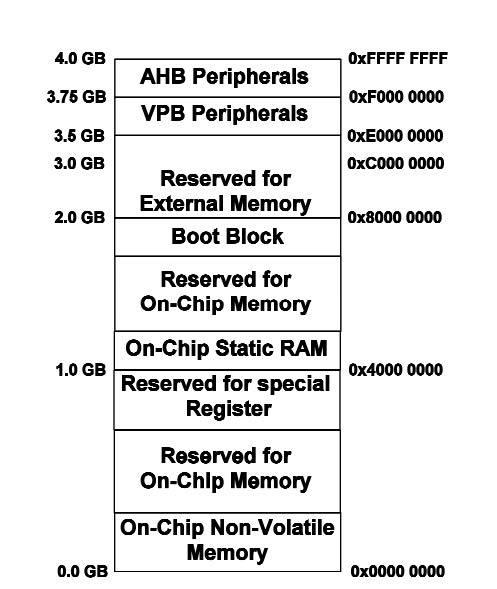

Un altro accessorio per aumentare le prestazioni del microcontrollore è fornito dal Memory Acceleretor Module (MAM). Uno dei maggiori limiti nel design di sistemi embedded ad alta velocità è quello dell’accesso veloce alla memoria Flash. Il chip ARM è capace di lavorare fino a 80 MHz. La comune memoria flash ha un tempo di accesso che si aggira intorno ai 50ns limitando la velocità della CPU a 20MHz. Questo problema è risolto con il MAM, che gestisce due banchi di memoria aventi ciascuno 128 bit. All’avvio del processore, il programma viene via via caricato su questi due banchi, al fetch della CPU si hanno subito disponibili ben 4 istruzioni ARM a 32 bit o 8 THUMB a 16 bit, mentre queste istruzioni sono eseguite, il secondo banco è disponibile per un ulteriore fetch. Nonostante il numero interno di bus, LPC2000 ha una mappatura di memoria lineare. La struttura generale è rappresentata in figura 9.

Figura 8: struttura del Bus.

Figura 9: memory Map.

Le istruzioni

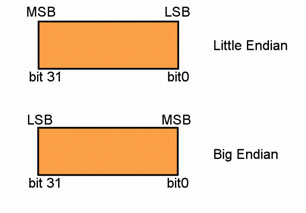

L’ARM7 è designato per operare sia in modalità big-endian che little-endian (figura 10).

I principali set di istruzioni sono:

- Branching

- Data processing

- Data transfer

- Block Transfer

- Software interrupt multiplo.

Figura 10: big-endian e little-endian.

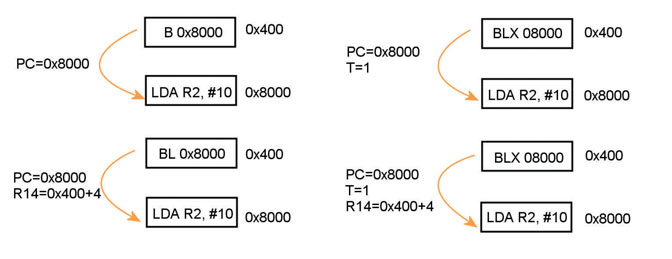

Figura 11: branching.

Il Branching è quell’operazione che permette al sistema di fare dei salti, avanti o indietro, nel programma. In alcuni casi esiste una versione modificata della classica operazione di branch, la branch link, questa fa la stessa operazione del branching classico con la differenza che salva l’indirizzo corrente del PC nel link register. Nel caso quindi di salto condizionato il processore esegue prima un’operazione di branch link e una volta ultimata la subroutine ritorna al punto di partenza grazie all’indirizzo salvato sul LR con un branch classico (figura 11). L’istruzione data processing si compone di diverse strutture rappresentate in figura 12.

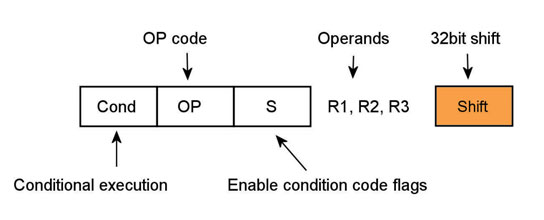

Figura 12: data processing.

Gli altri due tipi di istruzioni (figura 13) vengono utilizzati per copiare singoli o multipli registri, oppure scambiare il contenuto di due registri (swap) o modificare lo stato del registro stesso.

Figura 13: data/Block Transfer.

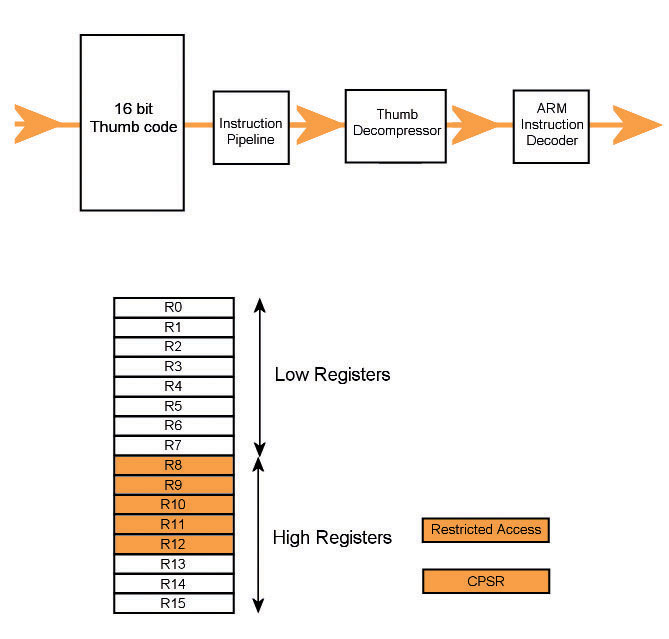

L’istruzione Software interrupt è utilizzata per forzare il processo in esecuzione nella modalità supervisore. Benché ARM7 è un processore a 32 bit ha anche un secondo set di istruzioni a 16 bit chiamato THUMB (figura 14).

Figura 14: THUMB.

La differenza principale rispetto alle istruzioni a 32 bit è che le istruzioni THUMB non hanno accesso a tutti i registri ma solo a R0-R7. Solo pochissime istruzione possono accede a R8-R12.

Il software

La maggior parte dei microcontrollori viene programmata non più con codici di basso livello come l’Assembler, ma con il linguaggio C. Il codice C, essendo un linguaggio di più alto livello, consente una maggiore semplicità di utilizzo: infatti con i puntatori si è in grado di lavorare comodamente con registri e locazioni di memoria. Il problema del C, come di ogni linguaggio di programmazione ad alto livello, è che occorre trovare un compilatore affidabile in grado di tradurne le parole in linguaggio macchina. Esistono software di sviluppo sia open source che proprietari aventi tool a volte discutibilmente utili. Per lo sviluppo di applicazioni con LPC2000 è molto comodo utilizzare IDE µvision 3 della KEIL. La versione dell’IDE reperibile gratuitamente sul web è completa di ogni opzione. Ha come unico limite la capacità di programmare solo 16Kbyte di memoria flash. Il software µvision include: l’ARM Real View compiler, un potente debugger software in grado di testare tutte quante le principali periferiche; una libreria avente le specifiche di tutti i microcontrollori aventi CPU ARM; validi esempi di codice tra cui anche un µKer nel per lo sviluppo di un sistema RTOS (Real T ime Operative System ). Una volta scelto il tipo di dispositivo sul quale si intende lavorare, l’IDE fornisce, in automatico, un comodo file chiamato startup.s nel quale è possibile dare una prima configurazione del sistema impostando: PLL e clock del sistema, il clock del bus (VPBDIV), il MAM e configurare la memoria di stack. Una volta fatto questo è possibile iniziare a scrivere il codice che verrà quindi eseguito dopo il file di startup. Una volta scritto il codice, è buona norma andarlo a simulare prima via software: l’IDE vision dispone di un potentissimo e affidabile debugger software (in alternativa o in aggiunta è possibile esegure anche un hardware debugging) in grado di gestire tutte quante le componenti del microcontrollore. Infatti, l’interfaccia consente oltre che effettuare classiche simulazioni degli stati logici dei pin esterni (Logic Analyzer) anche di visualizzare, in maniera real-time, gli stati dei registri interni alla CPU, gli accessi alla memoria flash e gli stati di tutte le periferiche e dei registri connessi, interni al microcontrollore.