I progettisti si dividono tra coloro che utilizzano architetture di tipo Harvard e quelli che continuano a sostenere i dispositivi basati su Von Neumann. Le architetture Harvard hanno una divisione funzionale estremamente interessante: dividendo la sezione codice da quella dei dati possono offrire una macchina più robusta in fatto di sicurezza, anche se poi occorre considerare altri aspetti.

Alcuni si chiedono, a ragion veduta, se un computer che si vanta di offrire un’architettura Harvard, con codice e dati separati, può essere immune agli attacchi di tipo code injection perché un dato non può essere trattato allo stesso modo di codice eseguibile. Per essere precisi, una giustificazione di questo tipo non è del tutto corretta. Infatti, ogni architettura offre sempre un punto di unione; in qualsiasi architettura presa come riferimento esiste sempre un momento in cui i dati sono trattati alla stessa stregua di codice eseguibile. Nelle soluzioni di tipo Von Neumann questo succede immediatamente all’interno della CPU, mentre in quelle Harvard il procedimento è differente. In questo caso può avvenire prima che la memoria sia riservata e assegnata al modulo, o ancora prima, se pensiamo a un file che sia stato in precedenza già preparato a questo scopo. Infatti, è possibile inserire in un file, o in una struttura dati, codice maligno e, di conseguenza, nella memoria della macchina e causare, ad esempio, un buffer overflow per reindirizzare differentemente l’esecuzione, utilizzando la struttura già caricata in precedenza. In realtà, in un sistema embedded, il procedimento non è del tutto semplice e occorre uno studio finalizzato, ma nulla è impossibile, come dimostra, per esempio, il lavoro di Francillon e Castelluccia che hanno posto in evidenza il loro risultato in “CCS ‘08: Proceedings of the 15th ACM conference on Computer and communications security”.

ARCHITETTURE HARVARD E VON NEUMANN

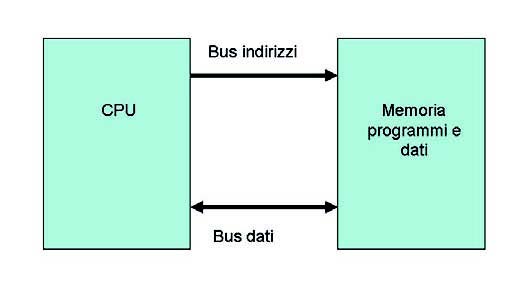

I microprocessori possono essere raggruppati in diverse categorie: microprocessori general-purpose, microcontrollori, processori specializzati all’elaborazione dei segnali o DSP. I microprocessori del tipo general-purpose offrono una soluzione architetturale finalizzata all’ottimizzazione della gestione della memoria, anche se poi, tipicamente, le loro prestazioni nell’elaborazione digitale dei segnali risultano mediocri. I microcontrollori, ossia soluzioni hardware che implementano singole parti di un elaboratore, offrono un’architettura generalmente più funzionale all’ottimizzazione delle caratteristiche di I/O. Infine, i processori specializzati nell’elaborazione dei segnali (DSP) sono stati realizzati per ottimizzare le prestazioni nell’elaborazione dei segnali. La maggior parte dei microprocessori general-purpose è basata sull’architettura proposta da Von Neumann e realizzata per la prima volta nel 1951 (Figura 1) in cui dati e programmi vengono memorizzati nella stessa area di memoria.

Figura 1: Architettura Von Neumann

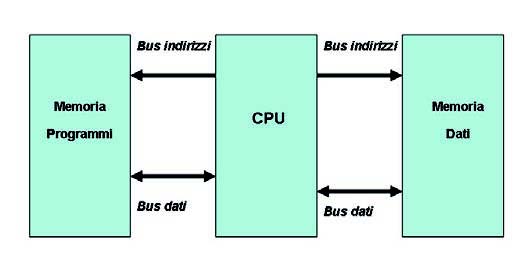

In questo caso esiste un’unica area di memoria per dati e programmi, e il processore usa gli stessi bus dati e indirizzi per accedervi. Le unità basilari sono l’unità aritmetico-logica (ALU) e l’unità di input-output (IO). L’unità ALU permette l’esecuzione di operazioni aritmetiche, mentre l’unità di input-output gestisce il flusso di dati esterni alla macchina. Per questo tipo di macchina, i programmi sono sequenze di istruzioni e la singola istruzione generalmente contiene un comando di operazione e l’indirizzo del dato su cui il comando deve essere eseguito. Esiste un’alternativa a questa proposta, ossia un’architettura che permette un aumento di velocità, come richiesto dalle applicazioni concernenti l’elaborazione dei segnali, ovvero l’architettura di Harvard, così come proposta negli anni trenta da Howard Aiken all’università di Harvard e realizzata negli anni quaranta (Mark IV ed Eniac). Quest’architettura prevede due spazi di memoria, uno per i dati, l’altro per i programmi e, analogamente, diversi bus dati e bus indirizzi per accedervi (Figura 2). Questa particolare architettura permette di accedere contemporaneamente sia ai dati sia alle istruzioni, ottenendo migliori prestazioni in velocità. Infatti, la fase di fetch dell’istruzione seguente è effettuabile in parallelo all’esecuzione dell’istruzione corrente. L’architettura Harvard aumenta la velocità di esecuzione, anche se introduce alcuni svantaggi. Per aumentare flessibilità nell’allocazione di spazio di memoria, alcuni processori prevedono speciali blocchi di memoria che possono essere riconfigurati o come memoria per dati o come memoria per programmi. Questo porta a processori con un’architettura di Harvard modificata: un singolo bus è usato esternamente per dati e indirizzi, mentre due o più bus separati per dati e programmi sono usati internamente, come il dispositivo DSP TMS320C203.

Figura 2: Architettura Harvard