La famiglia di Piattaforme Estensibili di Elaborazione Zynq-7000 di Xilinx coniuga nello stesso dispositivo un sistema basato su processore ARM Cortex-A9 MPCore con la logica programmabile e con periferiche IP sintetizzate su silicio, offrendo una combinazione impareggiabile di flessibilità, configurabilità e prestazioni.

Xilinx ha presentato i dispositivi di una famiglia realizzata attorno alla propria Piattaforma Estensibile di Elaborazione (EPP), un’architettura rivoluzionaria che abbina un processore duale ARM Cortex™-A9 MPCore con della logica programmabile a basso consumo e con periferiche IP sintetizzate su silicio, tutti nello stesso dispositivo. Xilinx ha annunciato i primi quattro dispositivi di quella che è stata ora chiamata la famiglia Zynq™-7000 EPP.

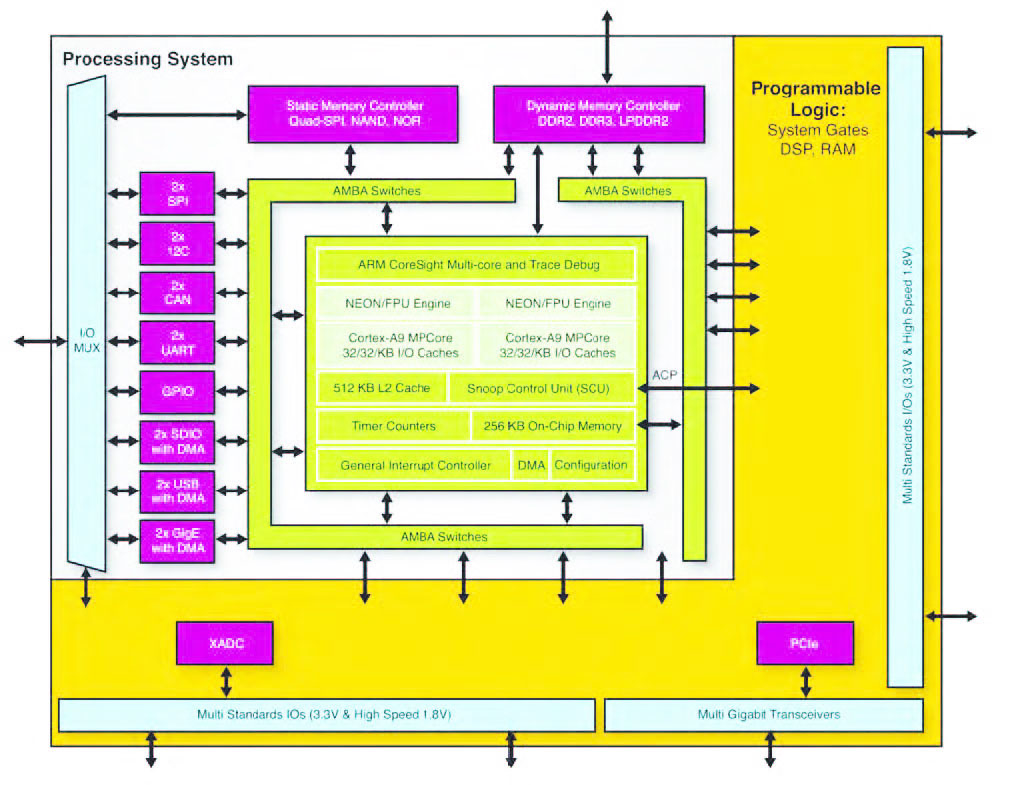

Ogni dispositivo Zynq-7000, realizzato nella tecnologia di processo da 28 nanometri, è strutturato con un sistema di elaborazione Cortex-A9 MPCore a doppio core di ARM, dotato di un’unità multimediale NEON e di un’unità a virgola mobile a doppia precisione, oltre a delle cache di Livello 1 e di Livello 2, ad un controllore multimemoria e ad un gran numero di periferiche di utilizzo comune (figura 1).

Figura 1: la famiglia di EPP Zynq-7000 lascia condurre la scena al processore ARM, piuttosto che alla logica programmabile.

Mentre i produttori di FPGA hanno dotato in precedenza i dispositivi con processori su scheda, sia sintetizzati su silicio, sia sintetizzabili, l’EPP Zynq-7000 è unico per il fatto che è il sistema processore ARM, anziché la logica programmabile, a dominare la scena. In altri termini, Xilinx ha progettato il sistema di elaborazione di modo che si avvii in fase di accensione (prima della logica FPGA) e che faccia girare una varietà di sistemi operativi indipendenti dalla matrice di logica programmabile. I progettisti programmano quindi il sistema di elaborazione per configurare la logica programmabile in base alle necessità. Con questo approccio, il modello di programmazione software è esattamente lo stesso dei System-onChip (SoC) con funzionalità complete basati su processore ARM. Le realizzazioni precedenti richiedevano, da parte dei progettisti, la programmazione della logica FPGA per far funzionare il processore su scheda. Ciò significava che dovevate essere un progettista FPGA per usare i dispositivi. Questo non è il caso con gli EPP Zynq-7000. La famiglia di prodotti elimina il ritardo e i rischi legati alla progettazione di un chip partendo da zero, facendo sì che i gruppi di progettazione a livello di sistema possano creare in tempi rapidi SoC innovativi, sfruttando una versatilità di programmazione hardware e software semplicemente non ottenibile con altri dispositivi su semiconduttore. Come tale, l’EPP Zynq-7000 è la soluzione ideale che consente ad un vasto numero di innovatori (siano essi professionisti in campo hardware, software o progetti sti a livello di sistema, o semplici “produttori”) di esplorare le possibilità di combinare le risorse di elaborazione con la logica programmabile per creare applicazioni che nessuno aveva mai immaginato prima. “Al suo livello più elementare, l’EPP Zynq-7000 costituisce una classe di prodotti su semiconduttore” ha affermato Larry Getman, vice presidente della divisione piattaforme di elaborazione presso Xilinx. “Non è semplicemente un processore e non è solo un FPGA. Noi combiniamo i vantaggi di entrambe le soluzioni, e per questo motivo eliminiamo molte delle limitazioni che avete con le soluzioni esistenti, specialmente con le soluzioni a due chip e con gli ASIC.” Getman osserva che molti sistemi elettronici oggi abbinano un FPGA e/o un processore standalone o un ASIC con un processore su scheda sullo stesso PCB. L'offerta di Xilinx consentirà al le aziende che usano questi tipi di soluzioni a due chip di realizzare sistemi di prossima generazione con un solo chip Zynq-7000, risparmiando sui costi per i componenti e sullo spazio su PCB, e riducendo i budget complessivi di potenza. E, dato che il processore e l’FPGA sono sulla stessa matrice, l’incremento delle prestazioni è immenso. L’EPP Zynq7000 accelererà inoltre la migrazione naturale del mercato dagli ASIC agli FPGA, ha dichiarato Getman. La realizzazione degli ASIC nelle ultime tecnologie di processo è troppo costosa e troppo rischiosa per un numero crescente di applicazioni. Di conseguenza, sempre più aziende stanno adottando gli FPGA. Molti di coloro che cercano di mantenere le vecchie metodologie ASIC, realizzano i propri progetti nelle geometrie di processo più vecchie, in ciò che gli analisti chiamano “SoC ASIC orientati al prezzo.” Qualsiasi ASIC richiede ancora cicli di progettazione lunghi ed è a rischio di dover incorrere in più cicli di riprogettazione, che possono essere costosi e possono ritardare l’introduzione tempestiva sul mercato dei prodotti. “Con l’EPP Zynq7000 in tecnologia da 28 nm, la porzione di logica programmabile del dispositivo non presenta penalizzazioni, in termini di dimensioni o di prestazioni, rispetto alle tecnologie di generazione precedente, e vi consente anche di ottenere l’ulteriore vantaggio di un SoC sintetizzato su silicio da 28 nm all’interno del sottosistema di elaborazione. Con un prezzo di partenza al di sotto di 15 dollari, stiamo realmente rendendo difficile per le aziende giustificare i costi e i rischi di progettare su ASIC, a meno che non si tratti di volumi estremamente elevati,” ha affermato Getman. “Potrete avere i vostri gruppi di sviluppo hardware e software completamente operativi fin dal primo giorno. Questo da solo rende difficile per i gruppi di ingegnerizzazione giustificare la scelta di mantenere l’approccio ASIC.” Getman osserva che da quando Xilinx ha annunciato l'architettura, l’anno scorso, l’interesse e le richieste di EPP Zynq-7000 sono state notevoli “Un numero selezionato di clienti alfa sta già prototipando i sistemi che usano i dispositivi Zynq-7000. La tecnologia è molto interessante.”

Decisioni intelligenti a livello architetturale

Il gruppo di progettazione dell’EPP Zynq7000, sotto la direzione di Vidya Rajagopalan, vice presidente per le soluzioni di elaborazione di Xilinx, ha ideato un’architettura ben congegnata per questa classe di dispositivi. Prima e al di là di scegliere l’onnipresente e immensamente popolare sistema di processore ARM, una decisione chiave dal punto di vista architetturale è stata quella di usare diffusamente l’interconnessione di Interfaccia Estensibile Avanzata (AXI™) AMBA® a larga banda fra il sistema di elaborazione e la logica programmabile. Questo consente di effettuare trasferimenti dati dell’ordine dei gigabit fra l’unità ARM a due core, il sottosistema di elaborazione MPCore Cortex-A9 e la logica programmabile a consumi molto bassi, eliminando di conseguenza i colli di bottiglia comuni nelle prestazioni per il controllo, i dati, gli I/O e la memoria. Xilinx ha collaborato, infatti, con ARM per adattare ancora meglio l’architettura ARM alle applicazioni FPGA. “L’AXI4 dispone di una versione con mappatura in memoria e una versione a flusso continuo”, ha spiegato Rajagopalan. “Xilinx ha accelerato la definizione della versione a flusso continuo per la soluzione ARM, perché numerosi blocchi di proprietà intellettuale che sono realizzati per applicazioni quali il video a larga banda; sono unità IP che operano a flusso continuo. ARM non disponeva di un prodotto che avesse questa interfaccia a flusso continuo e così hanno collaborato con noi per realizzarlo.” Getman ha spiegato che un altro aspetto chiave dell’architettura è che Xilinx ha sintetizzato su silicio una combinazione vantaggiosa di proprietà intellettuale di interfacce standard all’interno del silicio degli EPP Zynq-7000. “Abbiamo cercato di scegliere periferiche che fossero più diffuse, come USB, Ethernet, SDIO, UART, SPI, I2C e GPIO, che sono tutte praticamente standard,” ha affermato Getman. “L’unica eccezione è che abbiamo anche aggiunto l’interfaccia CAN al dispositivo. L’interfaccia CAN è quella più specializzata fra le unità sintetizzate su silicio, ma è largamente usata in due dei nostri mercati chiave di riferimento: quello industriale e quello automotive. Il fatto di averla sintetizzata su silicio all’interno del dispositivo, è un ulteriore fattore di convenienza dell’EPP Zynq-7000.” In termini di memoria, i dispositivi Zynq-7000 offrono fino a 512 kbyte di cache L2, che è condivisa da entrambi i processori. “I dispositivi EPP Zynq-7000 hanno 256 kbyte di memoria di lavoro, che è una memoria condivisa a cui sia il processore, sia l’FPGA possono accedere,” ha spiegato Getman. Un controllore DDR unico multistandard supporta tre tipi di memoria a doppia velocità di trasmissione dati. “Là dove gran parte degli ASSP si rivolgono ad un particolare segmento di un mercato, noi supportiamo le interfacce LPDDR2, DDR2 e DDR3, di modo che l’utente possa effettuare il compromesso fra la decisione di privilegiare la riduzione dei consumi o le prestazioni, “ha affermato Rajagopalan. “Si tratta di un controllore DDR multistandard e noi siamo una delle prime società ad offrire un controllore di questo tipo.” Oltre ad essere una classe di dispositivi, l’EPP Zynq -7000 è anche l’ultima Piattaforma di Progettazione Mirata di Xilinx, offerta con schede di sviluppo base, software, IP e documentazione, per rendere i clienti operativi in tempi rapidi. Inoltre, la compagnia introdurrà nel corso dei prossimi anni Piattaforme di Progettazione Mirata EPP Zynq-7000 per mercati verticali e Piattaforme specifiche di un’applicazione, schede o schede figlia, IP e documentazione, il tutto per aiutare i gruppi di progettazione ad introdurre i prodotti sul mercato più rapidamente. I membri dello Xilinx Alliance Program e della Connected Community di ARM offriranno inoltre ai clienti una varietà di risorse per gli EPP Zynq-7000, inclusi i sistemi operativi più diffusi, i debugger, l’IP, i progetti di riferimento e altri materiali di apprendimento e per lo sviluppo. Oltre a realizzare silicio di eccellente qualità e i tool relativi, Xilinx ha messo assieme meticolosamente flussi di progettazione e di programmazione facili all’uso per l’EPP Zynq-7000.

Un flusso di progettazione che ruota attorno al processore

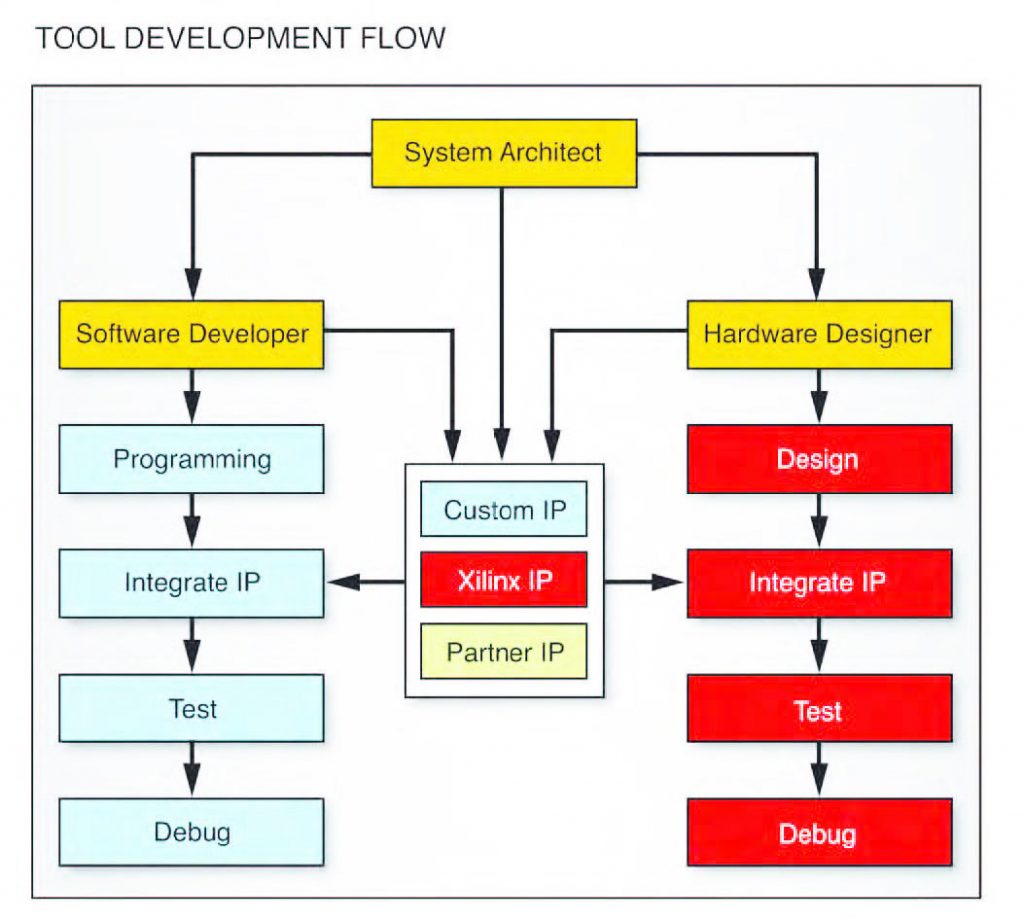

L’EPP Zynq-7000 si basa su una sequenza di tool familiare che consente agli ingegneri hardware e agli ingegneri software che realizzano soluzioni dedicate di effettuare i loro rispettivi compiti di sviluppo, di messa a punto e di esecuzione nello stesso modo che fanno ora, usando metodologie comuni di progettazione dedicata già fornite attraverso la Suite di Progettazione Xilinx® ISE® e da tool di terzi (figura 2).

Figura 2: l’EPP Zynq-7000 si basa su una sequenza di tool comuni sia per gli architetti di sistema, sia per gli sviluppatori software, sia per i progettisti hardware.

Getman osserva che gli ingegneri applicativi software possono usare gli stessi tool di sviluppo che hanno utiliz-zato per i progetti precedenti. Xilinx fornisce il Kit di Sviluppo Software (SDK), un insieme di tool basati sullo standard Eclipse per i progetti di applicazioni software dedicate. Gli ingegneri possono anche usare altri ambienti di sviluppo di terzi, come ARM Development Studio 5 (DS-5™), ARM RealView Development Suite (RVDS™), o altri tool di sviluppo dall’ecosistema ARM. Gli sviluppatori di applicazioni Linux possono sfruttare appieno entrambe le unità CPU Cortex-9 all’interno dei dispositivi Zynq-7000 in modalità processore simmetrica, per ottenere le massime prestazioni. In alternativa, essi possono impostare le unità CPU in una modalità a singolo processore o multiprocessore asimmetrica su cui gira Linux, un sistema operativo in tempo reale (RTOS) come VxWorks o entrambi. Per avviare lo sviluppo software, Xilinx fornisce ai clienti dei driver Linux di tipo open source, oltre ai driver grezzi per tutte le periferiche di elaborazione (USB, Ethernet, SDIO, UART, CAN, SPI, I2C e GPIO). Anche i pacchetti di supporto OS/RTOS alla scheda, pienamente supportati, saranno disponibili da parte dell’ecosistema di partner di Xilinx e di ARM. Nel frattempo, il flusso di progettazione hardware è simile al flusso di progettazione dei processori dedicati all’interno della suite di progettazione ISE, con qualche nuovo passaggio per la Piattaforma Estensibile di Elaborazione. Il sottosistema di elaborazione è un sistema completo a due processori, con un ampio insieme di periferiche di uso comune. I progettisti hardware possono estendere la potenza di elaborazione, aggiungendo ulteriori periferiche IP sintetizzabili all’interno della logica programmabile verso il sottosiIl tool di sviluppo hardware Xilinx Platform Studio automatizza molte delle fasi di sviluppo hardware più comuni ed è anche in grado di assistere i progettisti attraverso una piedinatura ottimizzata dei dispositivi. “Abbiamo anche aggiunto a ISE alcune funzionalità di ricerca guasti congiunta per i punti di arresto hardware e per le attivazioni incrociate,” ha spiegato Getman. “La cosa più importante per noi era fornire agli sviluppatori software e ai progettisti hardware i loro ambienti di progettazione nel massimo comfort.”

Una metodologia di programmazione consapevole

Nello schema di Xilinx, gli utenti possono configurare la logica programmabile e connetterla all’unità ARM attraverso dei blocchi di “interconnessione” AXI per estendere le prestazioni e le funzionalità del sistema processore. L’ecosistema di partner di Xilinx e di ARM fornisce un grande insieme di unità di interfaccia IP sintetizzabili di tipo AMBA, che possono essere realizzate all’interno della logica programmabile FPGA. I progettisti possono usarli per realizzare qualsiasi funzione dedicata di cui la loro applicazione di riferimento necessita. Dato che il dispositivo fa uso di strutture comuni in logica programmabile che si trovano all’interno degli FPGA della serie 7, i progettisti possono caricare una configurazione in logica programmabile di tipo statico, più configurazioni o persino avvalersi di tecniche di riconfigurazione parziale, per consentire al dispositivo di riprogrammare in corso d’opera la funzionalità della logica programmabile, secondo le necessità. Il funzionamento dell’interconnessione fra le due regioni del dispositivo è in larga misura trasparente ai progettisti. L’accesso fra il master e lo slave è indirizzato attraverso l’interconnessione AXI, in base all’insieme di indirizzi assegnati a ciascun dispositivo slave. Più master possono accedere a più slave simultaneamente, e ciascuna interconnessione AXI usa uno schema di arbitrazione a due livelli per risolvere le collisioni.

Preparatevi, sarete pronti prima…

I clienti possono iniziare oggi a valutare la famiglia di EPP Zynq-7000, aderendo al programma Early Access. I primi dispositivi su silicio sono previsti per la seconda metà del 2011, mentre i campioni per la pre-produzione saranno disponibili nella prima metà del 2012. I progettisti possono usare immediatamente i tool e i kit di sviluppo che supportano la tecnologia ARM, per familiarizzare con l’architettura MPCore Cortex-A9 e per iniziare a trasferire il codice. I prezzi variano e dipendono dal volume e dalla classe del dispositivo. In base alle previsioni sui prezzi per la produzione in volumi, la famiglia EPP Zynq-7000 avrà una fascia di prezzo di partenza al di sotto di 15 dollari per i grandi volumi. I clienti interessati possono contattare i propri rappresentanti Xilinx locali. Per maggiori informazioni, visitate www.xilinx.com/zynq.

Un sistema di elaborazione, quattro dispositivi

Ciascuno dei quattro dispositivi della famiglia di EPP Zynq-7000 ha esattamente lo stesso sistema di calcolo ARM, ma le risorse di logica programmabili variano in modo scalare e sono adatte per applicazioni diverse (si veda la figura). L’unità Multi-Processore (MPCore) Cortex-A9 consiste in due CPU, ciascuna con un processore MPCore Cortex A9, con un coprocessore dedicato NEON (un’architettura di elaborazione multimediale e segnali che aggiungono istruzioni dedicate per le funzioni audio, video, grafica 3D, elaborazione delle immagini e del parlato) e un’unità a virgola mobile a doppia precisione. Il processore CortexA9 è una macrocella ARM ad alte prestazioni e a basso consumo, con un sottosistema cache di Livello 1 che fornisce funzionalità complete di memoria virtuale. Il processore è realizzato in architettura ARMv7™ ed esegue istruzioni ARM a 32 bit, istruzioni Thumb a 16 bit e a 32 bit, e i codici di byte Java a 8 bit in tecnologia Jazelle. Inoltre, il sistema di elaborazione include un’unità di controllo per le investigazioni, un controllore cache di Livello 2, una SRAM onchip, temporizzatori e contatori, blocchi DMA, registri di controllo di sistema, blocchi di configurazione a livello di sistema e un sistema ARM CoreSight™. Quest’ultimo contiene una memoria interna temporanea di tracciamento, una macrocella di tracciamento per la strumentazione ed un modulo ARM con attivazione incrociata, assieme ad un monitor dell’interfaccia AXI e dei moduli per il tracciamento della matrice di Xilinx, per la ricerca guasti. I due dispositivi di dimensioni maggiori, Zynq-7030 e Zynq7040, includono la connettività seriale a basso consumo con i transceiver multigigabit, che operano fino a 10,3125 Gbits/secondo. Questi dispositivi offrono circa 1,9 milioni e 3,5 milioni di gate ASIC equivalenti (rispettivamente da 125.000 e da 235.000 celle logiche), assieme alle risorse DSP, le quali forniscono rispettivamente 480 GMAC e 912 GMAC di prestazioni di picco. I due dispositivi più piccoli, il Zynq-7010 e il Zynq-7020, forniscono rispettivamente all’incirca 430.000 e 1,3 milioni di gate ASIC equivalenti (30.000 e 85.000 celle logiche), con 58 GMAC e 158 GMAC di prestazioni DSP di picco. Ciascun dispositivo contiene un’interfaccia di convertitore analogico-digitale (XADC) di uso generico, che presenta due ADC a 12 bit da 1 Msample/s, sensori integrati e canali di ingresso analogici esterni. Lo XADC offre funzionalità potenziate rispetto al monitor di sistema che si trovava nelle generazioni precedenti degli FPGA Virtex®. I due ADC a 12 bit, che possono campionare fino a 17 canali esterni analogici di ingresso, supportano una gamma eterogenea di applicazioni che devono elaborare i segnali analogici con bande di meno di 500 kHz. La Piattaforma Estensibile di Elaborazione Zynq7000 debutta con una famiglia di quattro dispositivi. Tutti mostrano lo stesso sistema di elaborazione ARM, ma variano nelle risorse logiche programmabili. Il numero dei gate va da 430.000 a 3,5 milioni di gate ASIC equivalenti.