Il PSoCTM, prodotto di Cypress, non è il classico microcontrollore, ma qualcosa di più grazie alla presenza di blocchi analogici e digitali completamente configurabili a livello funzionale, così come le interconnessioni tra loro, al fine di sostituire con un singolo chip più blocchi funzionali. In questo modo l’utente può creare configurazioni ad hoc di periferiche che soddisfano le richieste di un particolare progetto. Esso rappresenta il giusto compromesso tra le logiche programmabili ed i microcontrollori.

Introduzione

Con il termine PSoCTM (Programmable System-on-Chip) si indica la famiglia dei sistemi prodotti da Cypress. L’architettura del PSoC è costituita da quattro aree funzionali:

- il core

- il sistema digitale

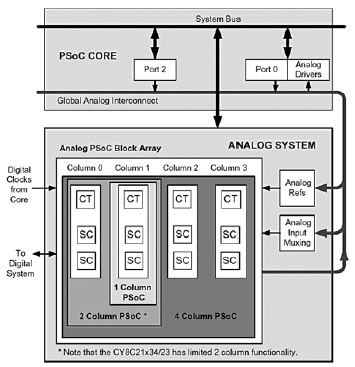

- il sistema analogico

- le risorse di sistema

La Tabella 1 riporta la classificazione dei differenti modelli di PSoC, evidenziando per ciascuno le caratteristiche peculiari.

L’architettura del core

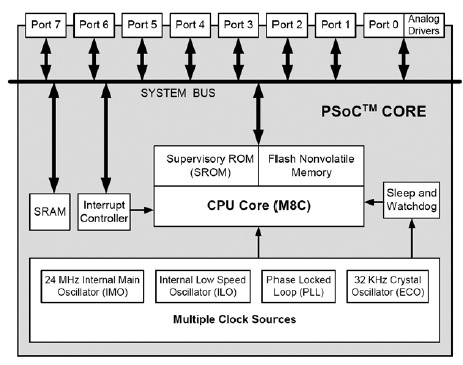

La Figura 1 mostra lo schema a blocchi del core del PSoC, indicato con il termine M8C. Si tratta di un micro con architettura Harvard ad 8bit.

La velocità del clock è selezionabile tra 93.7kHz e 24MHz, permettendo al core di adeguarsi alle prestazioni e consumo di potenza richiesti per un particolare progetto. Per quanto concerne lo spazio di indirizzamento, il PSoC è dotato di tre differenti aree: ROM, RAM e registri. Lo spazio per l’indirizzamento della ROM include il supervisore di ROM (SROM) e la Flash, come è mostrato in Figura 1. Esiste un bus apposito per accedere a quest’area. La Flash è organizzata in blocchi da 64byte. Lo spazio di indirizzamento dei registri è utilizzato per la configurazione dei blocchi programmabili del PSoC (descritti più avanti in questo articolo). Esso consiste di due banchi di 256byte ciascuno. Per la commutazione tra i due banchi, è necessario utilizzare il bit XIO del registro flag (‘1’ per il banco 1 e ‘0’ per il banco 0).

Set di istruzioni

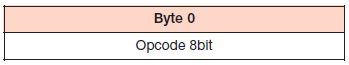

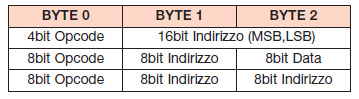

L’M8C presenta 7 formati di istruzione che utilizzano come lunghezza di uno, due o tre byte. Alcune delle istruzioni utilizzano un solo byte poiché non necessitano di un indirizzo o dato come operando (vedere la Tabella 2).

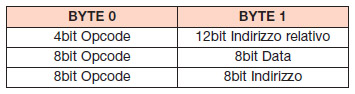

In questa categoria rientrano tutte le istruzioni che non aggiornano nessun registro (NOP e SSC), l’istruzione PUSH e HALT, le istruzioni che modificano i registri interni (ASL, ASR, CPL, DEC, INC …). La maggior parte delle istruzioni del M8C sono a 2byte. Nella riga 1 della Tabella 4 è mostrato il formato tipico con opcode a 4bit ed operando a 12bit, usato per istruzioni di salto incondizionato; CALL, JMP JNZ sono alcuni esempi. Nel secondo formato (riga 2 della Tabella 3) rientrano tutte le istruzioni con modalità di indirizzamento immediato (ad esempio ADD A, 7).

Infine, nel terzo formato (riga 3 della Tabella 3) rientrano tutte le istruzioni di indirizzamento non immediato. La Tabella 4 mostra l’ultima tipologia di istruzioni dell’M8C a 3 byte.

Il primo formato mostrato, è relativo alle istruzioni di salto LJMP e LCALL. Gli altri formati servono per effettuare indirizzamenti di tipo immediato differenti da quelli citati in precedenza.

La paginazione della RAM

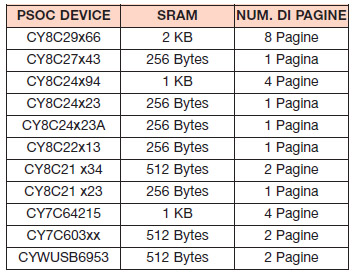

Il core del PSoC è dotato di una CPU e di un bus di indirizzamento ad 8bit. Questo permette di accedere fino a 256byte di SRAM. Ovviamente, esistono modelli dotati di quantità superiore. Questo è possibile grazie alla paginazione della memoria. La Tabella 5 mostra per ogni modello di PSoC la quantità di memoria disponibile e il numero di pagine gestite.

La modalità paginazione deve essere, però, abilitata mediante il bit 7 del registro CPU_F (altrimenti la memoria è limitata a 256byte). Il registro CUR_PP permette la selezione di una delle 8 pagine possibili. A questo punto tutte le istruzioni che operano sulla RAM faranno riferimento alla pagina indicata da CUR_PP[7]. La Figura 2 mostra lo schema a blocchi delle pagine di SRAM.

General purpouse I/O

Ciascun blocco GPIO può essere usato come:

- I/O digitale.

- I/O globale, per interconnettere i segnali ai/dai blocchi digitali del PSoC.

- I/O analogico, per interconnettere i segnali ai/dai blocchi analogici del PSoC.

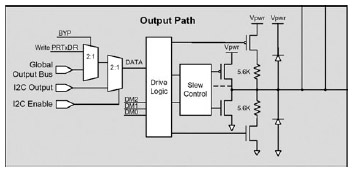

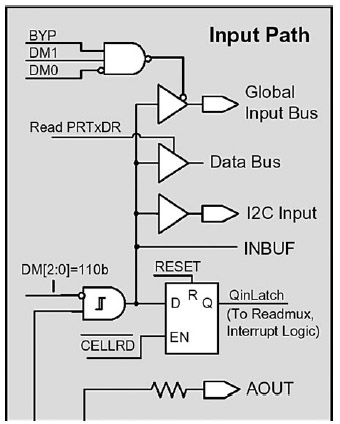

La configurazione generale di tali blocchi è mostrata in Figura 3 (stadio di uscita) e Figura 4 (stadio di ingresso).

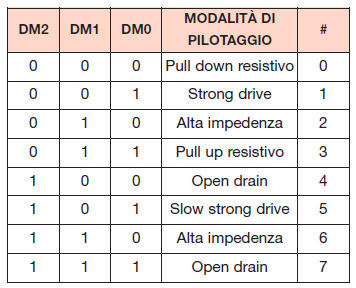

Per soddisfare le più svariate possibilità di pilotaggio di un carico, i blocchi GPIO possono essere configurati in 8 differenti modi, tramite i registri DM2, DM1 e DM0. La Figura 5 ne illustra le diverse possibilità, mentre la Tabella 6 descrive le impostazioni dei registri.

Per scrivere o leggere un valore sulle/dalle porte di uscita è sufficiente utilizzare il registro PRTxDR (dove x= 0…7).

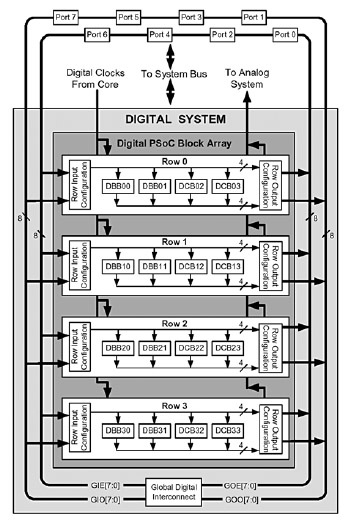

Il sistema digitale

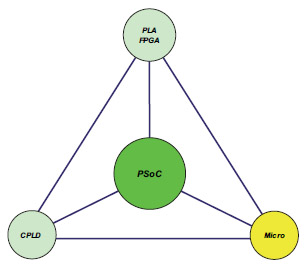

Quelle descritte fino a questo punto sono caratteristiche tipiche di un microcontrollore. Ma, in realtà, il PSoC è qualcosa di più che un semplice micro. La Figura 6 mostra come può essere inquadrato nel panorama dei dispositivi programmabili.

Figura 6. Il PSoC è qualcosa di più che un semplice microcontrollore. Esso si pone come compromesso tra la flessibilità di una logica programmabile ed quella di un micro.

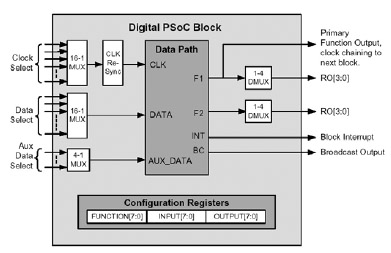

La sua architettura è dotata di blocchi digitali ed analogici che garantisce all’utilizzatore di creare un’ampia varietà di funzioni, anche a run-time. Ciascun blocco digitale (schematizzato in Figura 7) è una risorsa ad 8bit, che può essere configurata per essere una delle tante funzioni ad 8bit previste.

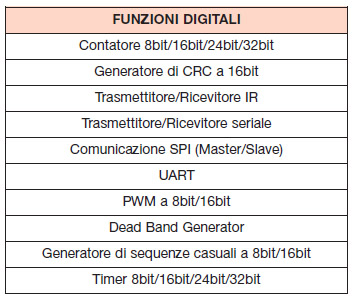

Per ottenere funzioni digitali con un numero di bit superiore si possono combinare più blocchi tra loro (ad esempio due blocchi possono essere uniti per ottenere un timer a 16bit oppure tre blocchi per farne uno a 24bit e così via). Essi possono anche implementare interfacce di comunicazione come UART, SPI e IR (InfraRed). Ciò che è importante sottolineare è che questi blocchi non sono programmati a livello di gate (come avviene ad esempio nelle PLA o FPGA), ma a livello funzionale, come se fossero tanti piccoli microcontrollori. Si riporta in Tabella 7 un elenco delle principali funzioni che si possono implementare con i blocchi digitali.

La cella base di questa architettura a blocchi è mostrata in Figura 8.

Si nota la presenta di tre registri di configurazione:

- FUNCTION, utilizzato per configurare cinque funzioni base (timer, counter, PWM, PRS e CRC).

- INPUT, rappresenta l’ingresso della funzione.

- OUTPUT, rappresenta l’uscita della funzione.

Il sistema analogico

I blocchi analogici sono, invece, basati su amplificatori operazionali programmabili (Figura 9).

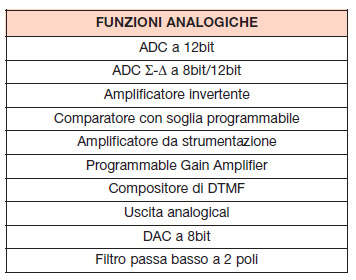

Ci sono tre tipi di PSoC Block, ciascuno con una differente struttura circuitale nel percorso di retroazione dell’opamp. Il primo tipo è un circuito tempo continuo con una matrice di resistenze programmabile nel percorso di feedback. Questo tipo di blocco ha un elevata impedenza di ingresso ed è utile per creare amplificatori a guadagno programmabile, attenuatori, amplificatori da strumentazione, filtri e comparatori analogici. A differenza del primo, i successivi due blocchi analogici presentano sul percorso di feedback degli switched capacitor (il vantaggio degli SC è la possibilità di simulare attraverso capacità, resistori il cui valore sarebbe impossibile da ottenere in un circuito integrato). Essi sono impiegati per realizzare filtri bi-quad, ADC di tipo SAR, ADC e DAC di tipo Σ-∆. La lista di tutte le funzioni analogiche possibili sono riportate in Tabella 8.

Risorse di sistema

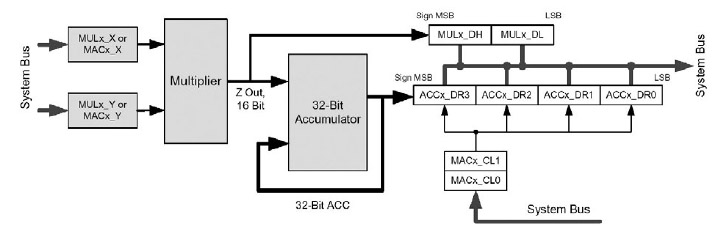

Tra le risorse di sistema di cui è dotato il PSoC bisogna sicuramente menzionare il modulo MAC (Multiply Accumulate). Può essere utilizzato come moltiplicatore semplice ad 8bit oppure combinato con l’accumulatore a 32bit. Esistono modelli di PSoC dotati di uno e due moduli indipendenti. Lo schema di principio è mostrato in Figura 10.

Per eseguire una moltiplicazione è sufficiente scrivere il valore del fattori nei registri MULx_X e MULx_Y, mentre il risultato sarà disponibile in MULx_DH e MULx_DL. Per effettuare la moltiplicazione con accumulazione è necessario scrivere i registri MACx_X e MACx_Y, mentre il risultato è disponibile nei registri ACCx_DR3, ACCx_DR2, ACCx_DR1 e ACCx_DR0. Questo modulo può essere molto utile per implementare, ad esempio, filtri digitali. Particolarmente efficace per applicazioni di elaborazione di segnali digitali è il modulo decimatore. In realtà, il PSoC ne presenta due varianti, indicate con tipo 1 e tipo 2. Per esempio, in un convertitore DAC è utilizzato un filtro decimatore di tipo sinc2 che è facilmente implementabile con il modulo tipo 1. Un altro punto di forza di questo sistema è rappresentato dalla presenta dell’interfaccia USB 2.0 (full-speed) integrata. Essa è costituita da:

- Blocco SIE (Serial Interface Engine).

- Blocco PMA (PSoC Memory Arbiter).

- 256 byte di SRAM dedicati

- Transceiver USB full-speed (12Mbps).

Tali blocchi semplificano enormemente la gestione del protocollo USB e riducono drasticamente il numero di componenti esterni.

Ambiente di sviluppo

Trasformare i blocchi digitali ed analogici del PSoC in utili funzioni per il proprio progetto non è di per se una cosa molto semplice. Perciò sono necessari strumenti di sviluppo che ne semplificano il compito. La famiglia dei dispositivi PSoC è dotata di “User Modules” per assistere il programmatore nella configurazione. Si tratta, cioè, di configurazioni già create e testate per realizzare una specifica funzione. Un tipico User Module digitale è il PWM a 16bit, mentre un tipico User Module analogico è l’ADC incrementale a 12bit. Questo permette al programmatore di concentrarsi solo sulla soluzione del problema, anziché districarsi nell’impostazione dei vari registri. È possibile modificare la configurazione non solo a design-time ma anche a run-time; così, ad esempio, un blocco utilizzato inizialmente come UART può essere convertito in un timer ad 8bit oppure in un generatore di sequenze casuali. Questa caratteristica, nota come ri-configurazione dinamica, permette riutilizzare blocchi digitali e analogici, fornendo una maggiore flessibilità del dispositivo. La Cypress mette a disposizione dei suoi clienti l’ambiente di sviluppo PSoC Designer IDE, L’altro ambiente di sviluppo proposto dalla casa madre è il PSoC Express. Si tratta di un nuovo strumento di sviluppo, easy-to-use, che migliora drasticamente la progettazione mixed-signal, permettendo di programmare con un livello di astrazione superiore al C e all’assembler. Sarà sufficiente trascinare i vari blocchi ed interconnetterli tra loro.

Cypress sta conducendo molte attivita’ di ricerca e sviluppo in vari ambiti quali il wearable e l’automotive con i sistemi ADAS.