Microcontrollore ad alte prestazioni e basso costo con Ethernet controller integrato. In questo articolo esploriamo le potenzialità e le risorse di questo versatile MCU per sistemi embedded su LAN e Internet.

Considerando la larga diffusione delle reti di calcolatori, siano esse di tipo industriale, civile o militare, si comprende come l’interfacciamento dei microcontrollori con il supporto fisico Ethernet, apra le porte ad una moltitudine di servizi ed applicazioni sempre più attuali e di largo riscontro. Il PIC18F67J60 rappresenta un'ottima risposta a molte esigenze di questo tipo, senza trascurare fattori come versatilità, performance, ingombri e costi ridotti.

La famiglia PIC18F97J60

Il PIC18F67J60 è un microcontrollore della famiglia PIC18F97J60, quest’ultima facente parte della PIC18J-series che raccoglie MCU con architettura a 8 bit ed implementanti via hardware l’Ethernet, l’USB full-speed e l’LCD-drivers. Le caratteristiche più rilevanti di questa serie sono: pinout da 18-100 pin, memoria Flash da 8-128 KByte, velocità di calcolo da 10-12 MIPS (Milion Instructions Per Second), voltage-range da 2,0-3,6V e input 5,5V tolerant. Ai fini dell’interfacciamento di un sistema embedded (con architettura a microcontrollore) con il supporto Ethernet, i MIPS forniscono una misura della velocità di elaborazione dei pacchetti dati da e verso la rete (e delle elaborazioni di supporto alle applicazioni implementate), il range di tensione (comprendente i 3,3V) garantisce una più facile interfacciabilità hardware con la rete fisica (livello fisico dello stack TCP/IP), mentre l’elevata capacità della memoria programma consente la memorizzazione di firmware complessi implementanti tutti (o in parte) i protocolli standard dello stack per la comunicazione in rete (TCP, IP, HTTP, AR P, ICMP eccetera). La famiglia PIC18F97J60 eredita i tradizionali vantaggi della serie PIC18, ovvero: alta permormance computazionale e un ricco set di caratteristiche. Alla luce dei punti di forza di questa famiglia, la Microchip la definisce come “una scelta logica per svariate applicazioni da alte prestazioni, dove il fattore costo è di primaria importanza”. Altre importanti particolarità di questi MCU sono l’EMB (External Memory Bus) e l’estensione del set di istruzioni. Il primo (solo per pic da 100 pin) è un BUS esterno che può essere opzionalmente implementato da alcune linee di I/O, e con il quale il pic è in grado espandere fino a ben 2 Mbytes la memoria programma. Ovviamente ciò è consentito dalla maggiore capacità di indirizzamento del program counter interno. Stesso discorso vale anche per la RAM con la quale poter memorizzare maggiori quantità di dati. L’“Extended Instruction Set” è l’estensione del normale set di istruzioni tipico della serie PIC18 (composto da 75 istruzioni), ottenuta dall’introduzione di otto istruzioni dedicate. Di default questi pic hanno abilitata questa estensione ma, all’occorrenza, può essere disabilitata ponendo a zero il bit XINST della configuration-bit. Le otto istruzioni sono state introdotte per meglio ottimizzare la ricorsione, l’uso di stacke la gestione di strutture dati presenti nel codice del software e, in modo particolare, per quelli stilati in linguaggi ad alto livello come il C. La famiglia PIC18F97J60 supporta l’ICSP (In-Circuit Serial Programming), l’ICD (In-Circuit Debugger) e l’ICE (In-Circuit Emulator). Inoltre viene supportata dall’intero ambiente di sviluppo MPLAB (MPASM, MPLAB C18 e MPLAB C30 compilers, MPLINK, MPLIB, MPLAB ASM30, MPLAB SIM), e dai diversi dispositivi di programmazione (PICSTART Plus, MPLAB PM3 e PICKit 2), di emulazione (MPLAB ICE 2000 e MPLAB REAL ICE) e di debug (MPLAB ICD 2) sviluppati dalla Microchip. Inoltre, la stessa azienda commercializza diverse board dimostrative (PICDEM.net 2, PICTAIL Daughter e Internet Radio Demo Board) basate sull’interfacciamento Ethernet, con le quali è possibile esplorarne le potenzialità, studiare e usare il pacchetto software dello stack TCP/IP, oggi giunto alla versione 4.55. Questo pacchetto, sviluppato per le serie PIC18, PIC24 e dsPIC, contiene i project in linguaggio C di alcune specifiche applicazioni per LAN e Internet, tutti i codici sorgente in C che implementano i protocolli standard di comunicazione in rete, e alcuni software molto utili per lo sviluppo di alcuni dispositivi quali i miniWebserver per la monitorizzazione remota, e le applicazioni embedded di controllo tramite LAN o Internet. Queste demoboard montano un pic della famiglia PIC18F97J60, oppure un microcontrolore della serie 18 ed il famoso controller Ether net ENC28J60, interfacciabile serialmente tramite SPI (Serial Peripheral Interface). La Internet Radio Demo Board monta proprio il PIC18F67J60 e implementa lo SHOUTcast di brani musicali in formato MP3, una tecnolgia di streaming dove i contenuti audio vengono trasmessi da una sorgente a uno o più destinatari su Internet.

Caratteristiche del PIC18F67J60

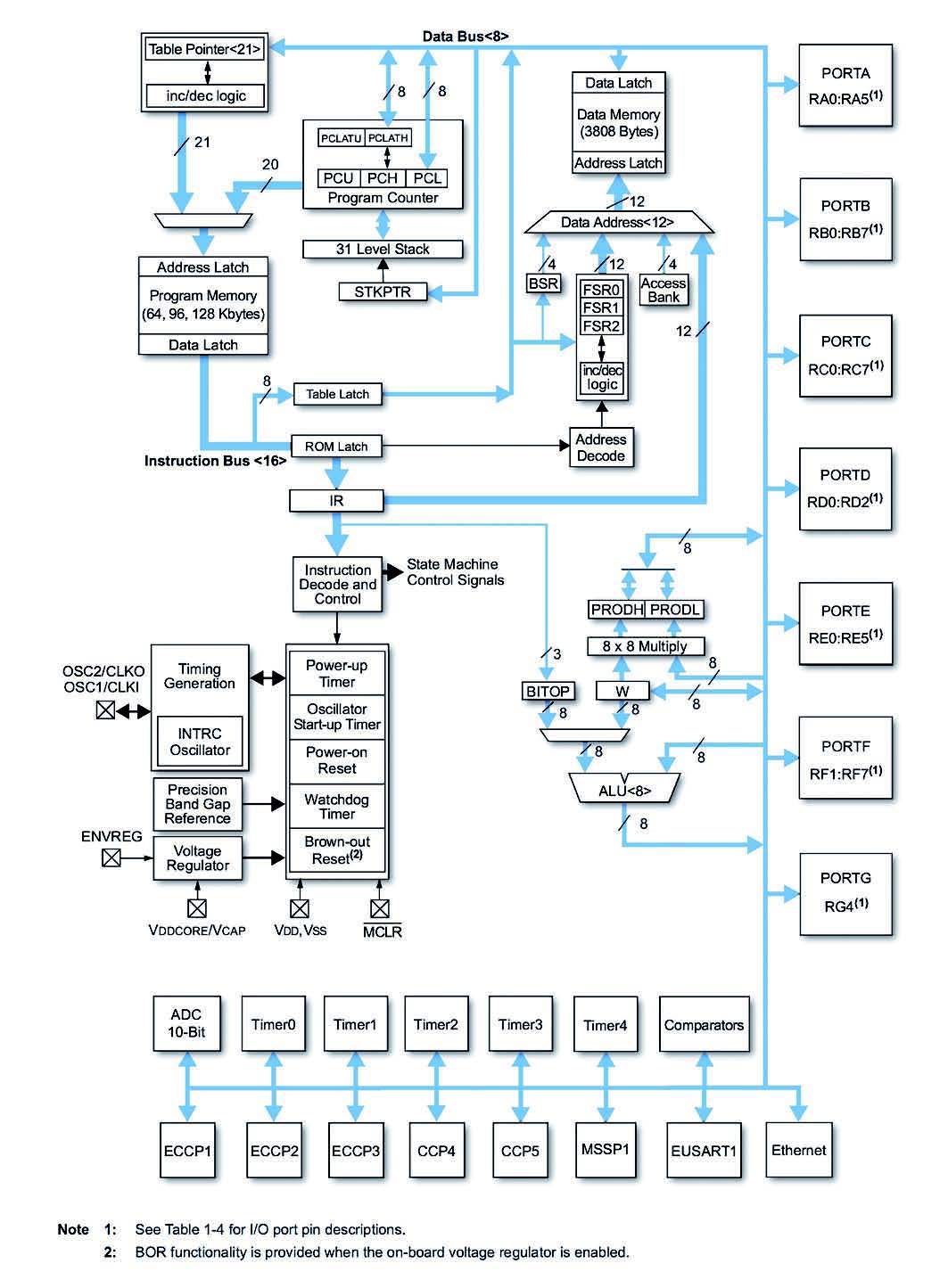

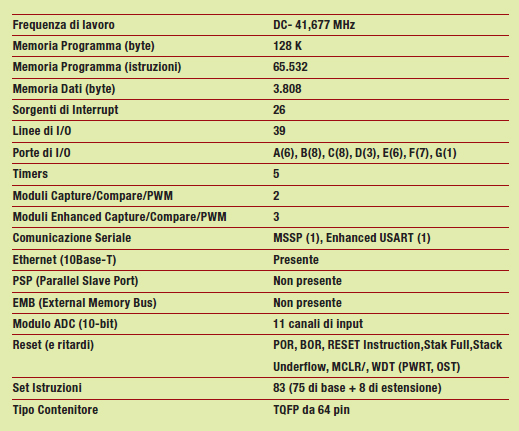

Questo microcontrollore, come tutti gli MCU della sua famiglia, è realizzato in tecnologia CMOS Low-Power High-Speed ed è disponibile in package smd tipo TQFP (Thin Quad Flat Pack) da 64 pin. Dispone di un totale di 39 linee di I/O suddivise (non equamente) in 7 port differenti. Di questi solo le linee dei port B e C sono in grado di fornire un’alta corrente di sink/source (25mA massimo), mentre quelle D, E e J possono pilotare carichi medi, e le rimanenti controllano solo carichi molto bassi. La tabella 1 riassume alcune delle più importanti caratteristiche hardware proprie del PIC18F67J60 (memoria, I/O, ADC, moduli di comunicazione, timer eccetera), mentre la figura 1 ne mostra lo schema a blocchi.

Figura 1: schema a blocchi del PIC18F67J60.

TABELLA 1: CARATTERISTICHE del PIC18F67J60

Il modulo Ethernet

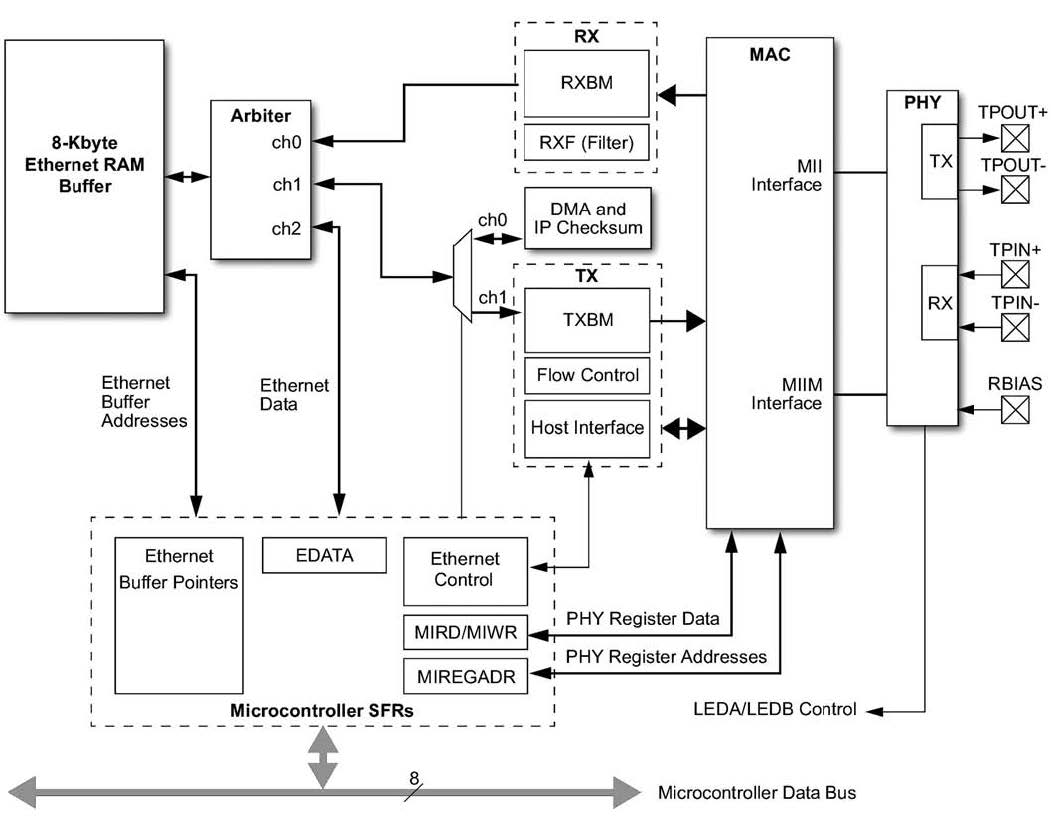

Come già anticipato, tutti gli elementi della famiglia PIC18F97J60 integrano un controller Ethernet embedded che garantisce il rispetto delle specifiche IEEE 802.3 (Institute of Electrical and Electronic Engineers), relative alla connettività a 10Base-T per reti Ethernet twisted-pair. Per completezza di informazione, la dicitura 10Base-T specifica una velocità di trasmissione pari a 10 Mbps in banda base su due doppini intrecciati, mentre “twister-pair” identifica un cavo elettrico i cui fili interni sono intrecciati a coppie, e queste tra loro, al fine di limitare interferenze, disturbi e crosstalk potenzialmente presenti durante le trasmissioni. Il modulo Ethernet implementa via hardware sia il Medium Access Control (MAC), che il Physical Layer transceiver (PHY). Questi due moduli, assieme al buffer per lo stoccaggio dei pacchetti ricevuti/trasmessi e ai moduli ‘Arbiter’ e di interfaccia registri, rappresentano i 5 blocchi più importanti integrati nel modulo Ethernet (vedere figura 2).

Figura 2: schema a blocchi del modulo Ethernet integrato

Nello specifico e brevemente:

» il modulo PHY è l’interfaccia che implementa la logica al più basso livello (quello fisico), previsto dallo stack TCP/IP secondo il modello ISO/OSI (International Standard Organization/Open System Interconnection). In altre parole, traduce i segnali analogici provenienti dal cavo Ethernet (secondo la codifica Manchester) e genera quelli da trasmettere sullo stesso supporto. Inoltre pilota, secondo la relativa programmazione, due led di stato della connessione (LEDA e LEDB), opzionalmente connessi alle linee di I/O RA0 ed RA1.

» Il modulo MAC implementa sia la logica di comunicazione secondo le specifiche IEEE 802.3 (quindi lavoro appena al di sopra del PHY), sia il MIIM (Media Independent Interface Management) per il controllo del PHY.

» Il Buffer è una RAM da 8 Kbytes per il salvataggio dei pacchetti da trasmettere/ricevere.

» L’Arbiter è quel circuito che controlla l’accesso al buffer quando si verificano le richieste da parte del microcontrollore, il DMA ed i blocchi RX e TX.

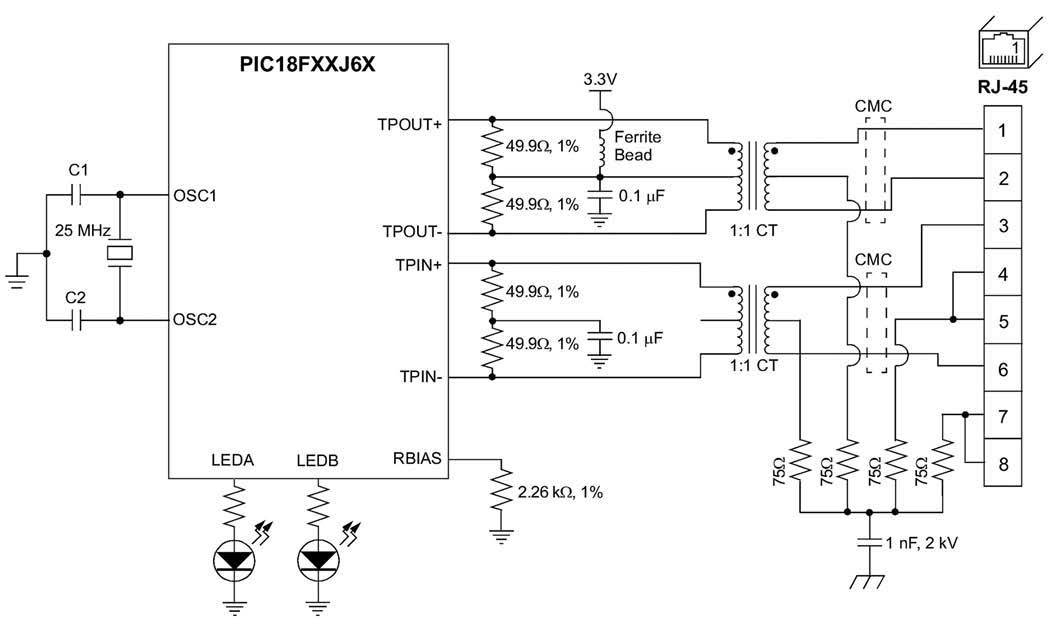

» L’SFR è l’interprete dei comandi e dei segnali tra il modulo Ethernet e il Microcontroller-SFRs (Select File Register). L’interfacciamento del pic col cavo Ethernet si realizza grazie a sole 4 linee elettriche differenziali dedicate: TPIN+ e TPINper l’input, e TPOUT+ e TPOUTper l’output. E’ da evidenziare che i blocchi TX ed RX del modulo PHY vengono alimentati indipendente (l’uno dall’altro e tra questi ed il resto del pic) grazie alle linee di alimentazione dedicate VDDTX, VSSTX, VDDRX e VSSRX, (così come anche il PLL: VDDPLL e VSSPLL). Completano la circuteria di interfaccia pochi componenti standard esterni come la resistenza RBIAS (pin 53), che modifica l’ampiezza dei segnali TPOUT+/- (il valore consigliato è di 2,26 KΩ), un piccolo trasformatore ad impulsi da interporre tra le linee TPOUT+/- TPIN+/- e i pin del connettore RJ45 per la connessione del cavo Ethernet, e poi alcune resistenze e condensatori tra le quali quelle necessarie all’EMI-reduction (Electro Magnetic Interference). Si fà presente comunque che in commercio sono disponibili connettori RJ45 che integrano gran parte di questi componenti (tra i quali anche i due led di segnalazione dello stato della connessione), cosa che decisamente riduce ancora di più la complessità del dispositivo embedded, nonché le sue dimensioni. La figura 3 mostra uno schema di riferimento riportante i componenti appena mensionati e la loro connessione al pic.

Figura 3: interfacciamento col connettore Ethernet RJ45.

Il modulo Ethernet, inoltre, integra un doppio controller DMA (Direct Memory Access) che consente la scrittura dei dati sul buffer e l’implementazione della logica del checksum a 16 bit, quest’ultimo pienamente compatibile con molti dei protocolli standard di comunicazione come il TCP, l’UDP, l’IP eccetera. Questo calcolo viene eseguito rispettando i seguenti passi:

■ 1-si sommano tra loro più byte raggruppati in interi da 16 bit;

■ 2-l’eventuale riporto al 16° bit viene sommato al primo bit; si fa il complemento ad uno del risultato.

Ad esempio, si deve calcolare il checksum dei byte 89h, ABh e CDh :

■ 1-89ABh + CD00 = 56ABh + riporto al 16° bit; 56ABh + 1 = 56AC; complemento a 1à Checksum = A953h .

L’Ethernet Buffer

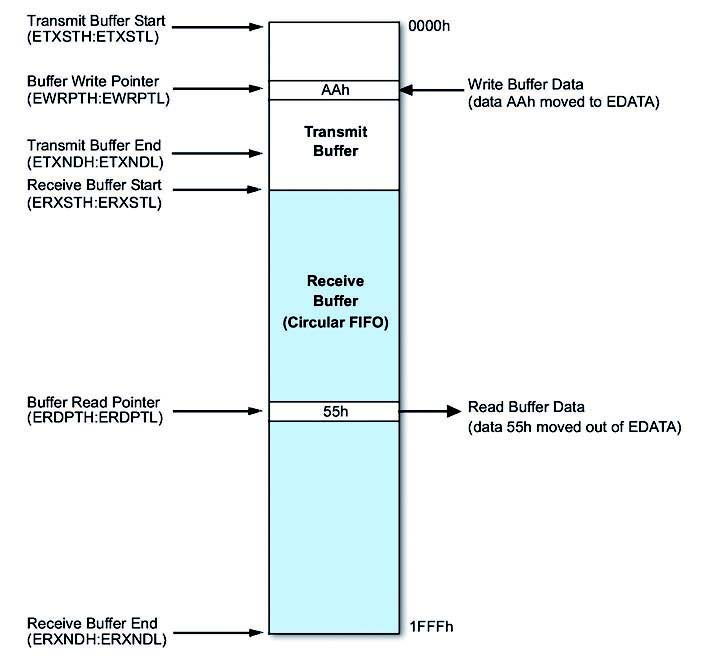

La RAM da 8 Kbyte destinata al buffer Ethernet può, all’occorrenza, essere impiegata dal microcontrollore per altri scopi, a patto che il modulo Ethernet venga disabilitato. L’accesso al buffer si realizza tramite il registro dati EDATA, il quale crea al suo interno una sorta di finestra per il bus dati. Questa ‘finestra’ è determinata dai contenuti dei registri puntatori ERDPT e EWRPT, rispettivamente per la lettura e la scrittura dei dati. Questi registri possono venire incrementati automaticamente ad ogni operazione di lettura/scrittura, se configurati opportunamente. La figura 4 mostra schematicamente l’organizzazione dell’Ethernet buffer.

Figura 4: organizzazione dell’Ethernet Buffer.

Si osservi come le coppie ETXSTH/ETXSTL e ETXNDH/ETXNDL (rispettivamente i registri a 16 bit ETXST e ETXND) delimitino il buffer di trasmissione, come analogamente fanno le coppie ERXSTH/ERXSTL e ERXNDH/ERXNDL (rispettivamente i registri a 16 bit ERXST e ERXND) per il buffer di ricezione. Poi vi sono i puntatori EWRPT ed ERDPT anch’essi divisi in byte alto e basso (EWRPTH/EWRPTL e ERDPTH/ERDPTL), per il puntamento del dato da scrivere (sul transmit buffer) e quello da leggere (dal receive buffer). La gestione del buffer di ricezione è di tipo FIFO circolare (First Input First Output). Questo significa che, una volta scritta la locazione di END (ultima del buffer di ricezione puntata da ERXND), il prossimo dato che sarà ricevuto e convalitato verrà salvato all’indirizzo di START dello stesso buffer (ERXST). Il contenuto del registro puntatore per i dati in scrittura (ERXWRPT), definisce automaticamente la finestra del buffer di ricezione occupata attualmente dai pacchetti ricevuti e salvati. Questo allora, consente di determinare quanto spazio libero è attualmente disponibile per i futuri dati. Và tuttavia evidenziato che, nel caso in cui il buffer arriva a riempirsi e i pacchetti continuano ad arrivare, i dati in memoria non ancora elaborati dall’applicazione non verranno persi sovrascrivendo quelli nuovi, anzi, saranno proprio questi ad essere gettati via. Questo meccanismo fà sì che l’applicazione in esecuzione non si veda sottratti dati non ancora elaborati, e quindi utili ai suoi fini. Affinchè il controller Ethernet salvi puntualmente tutti i dati ricevuti, bisogna far in modo che l’applicazione risulti sufficientemente veloce a ‘tenere il passo’. D’altronde, se quelle stesse applicazioni fanno uso di protocolli evoluti come il TCP/IP, avranno altre chance di ricevere nuovamente i dati precedentemente scartati a causa della mancanza di spazio nel buffer di ricezione. Il resto della RAM non destinata ai dati in ingresso, viene automaticamente assegnata al buffer di trasmisisone. Tuttavia, dal momento che via hardware non è possibile garantire che la definizione degli estremi del buffer di trasmissione (ETXST e ETXND) generi sovrapposizione tra i due buffer, è demandato al firmware il compito di non spedire pacchetti in questo particolare caso.

Configurazioni dell’oscillatore

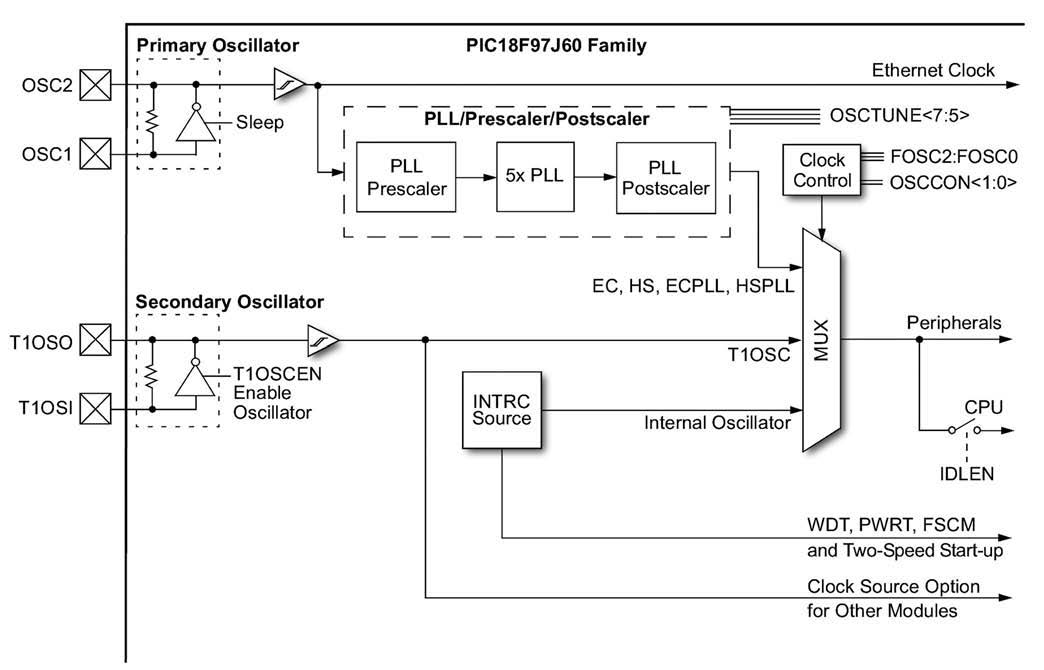

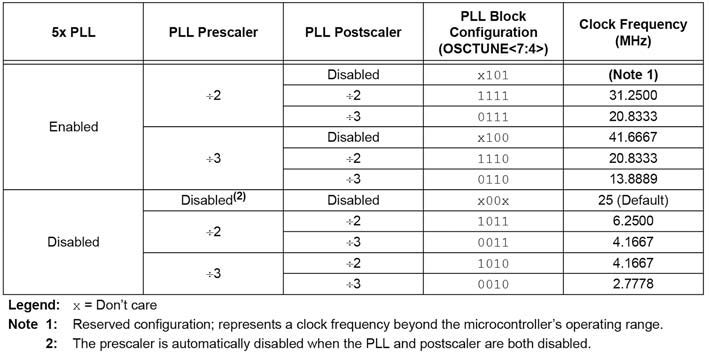

Tutti i microcontrollori della famiglia PIC18F97J60 offrono ben 5 modalità per la generazione del clock interno: HS e HSPLL che usano quarzi o risuonatori ceramici (il secondo anche il PLL), EC e ECPLL che impiegano clock esterni (il secondo anche il PLL), e l’INTRC, ovvero la modalità che utilizza l’oscillatore interno a frequenza fissa da 31 KHz. Quest’ultima ha una buona stabilità ed è in grado di garantire bassi consumi e robustezza nel funzionamento. Inoltre Microchip ha adottato alcuni particolari accorgimenti in grado di rendere ancora più robuste le applicazioni realizzate con questa famiglia. Tali accorgimenti si realizzano con le operazioni di “Fail-Safe Clock Monitor” e “Two-Speed Start-up”. La prima opzione monitorizza costantemente la sorgente primaria del clock impiegando un segnale di riferimento generato dall’oscillatore interno: in caso di comportamento anomalo, il controller seleziona in automatico quest’ultimo, così da consentire il proseguimento in low-speed oppure il salvataggio e la chiusura. Il “Two-Speed Start-up” invece, interviene selezionando dapprima l’oscillatore interno in occasione, ad esempio, di un Power-On Reset o di un risveglio dallo sleep-mode, per poi selezionare il clock primario quando questo diviene disponibile. Questi pic inoltre, integrano un PLL che permette di abbassare o aumentare (fino ad un massimo 41,667 MHz) la frequenza dell’oscillatore. La figura 5 mostra lo schema a blocchi del sistema per la generazione del clock: notare in alto la presenza del PLL/Prescaler/Postscaler, configurabile tramite i bit <7:5> del registro OSCTUNE.

Figura 5: schema a blocchi del sistema di generazione del clock.

La sorgente del clock è selezionata dal multiplexer e quindi dai bit di configurazione FOSC2:FOSC0 e dal registro OSCCON (bit <1:0>). E’ importante sottolineare che il controller Ethernet necessita di un clock con frequenza pari esattamente a 25 MHz. Dal momento che il segnale di sincronismo generato dal primary-oscillator viene riportato direttamente al modulo Ethernet, bisognerà collegare tra i pin OSC1 e OSC2 un quarzo (o un risuantore ceramico) con quella stessa frequenza o, in alternativa, un segnale di sincronismo esterno sempre a 25 MHz. In questo caso il blocco PLL, completo di prescaler, moltiplicatore 5x e postscaler, consentirà la generazione del clock (utile al resto del microcontrollore), con un valore di frequenza più idoneo per l’applicazione implementata dal sistema. La tabella 2 mostra le possibili configurazioni del blocco PLL e, quindi, le frequenze ottenibili partendo dai 25 MHz. Si segnala la possibilità di commutare la sorgente del clock e, contemporaneamente, la modalità operativa.

Tabella 2: possibili configurazioni del blocco PLL.