Questo microprocessore di NXP, basato sul core e500 realizzato in tecnologia Power Architecture, si evidenzia particolarmente per impieghi nel campo delle telecomunicazioni, del networking, e dei sistemi wireless.

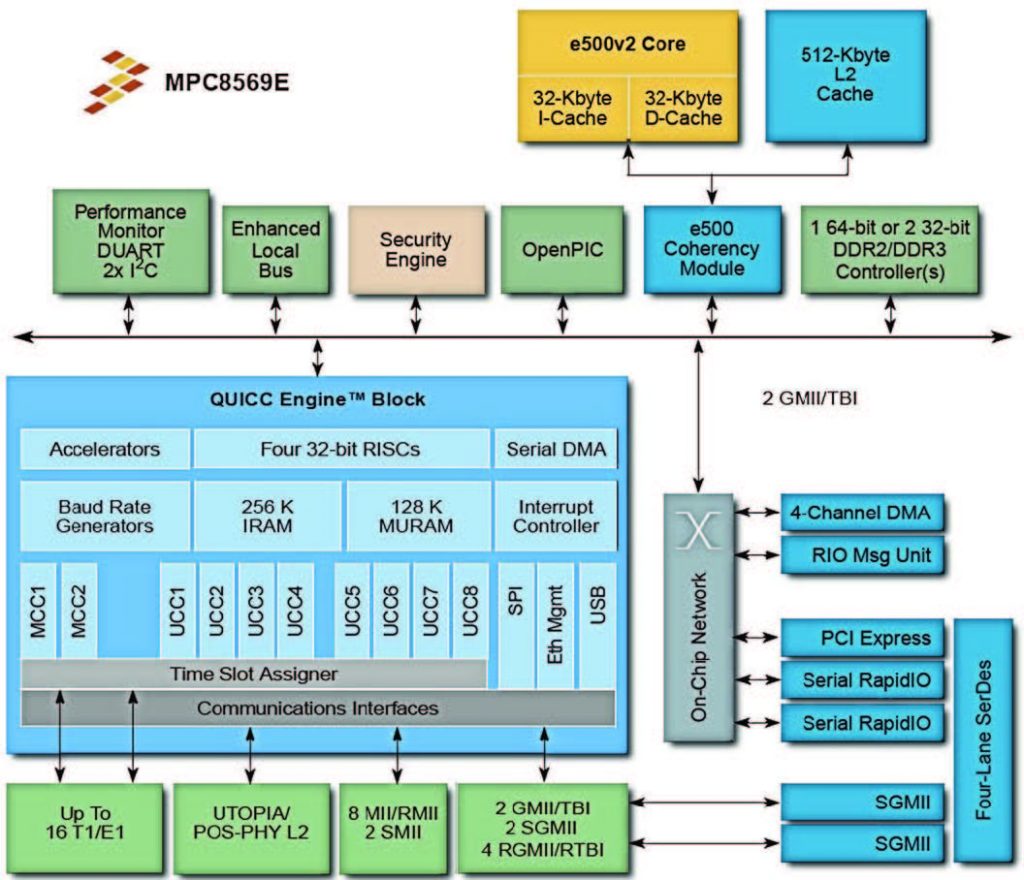

Il processore MPC8569 (visibile in figura 1) rappresenta un eccellente esempio di come si possa integrare il supporto per diversi tipi di protocolli ed interfacce su di uno stesso componente; esso comprende infatti una CPU ad elevate prestazioni con un’ampia memoria cache di livello 2, un controllore di memoria DDR2/DDR3 a 64-bit (oppure due controllori a 32-bit), interfacce di tipo PCI Express, SGMII, USB 2.0, e serial RapidIO. Tutte queste caratteristiche permettono di sostituire la gestione separata dei segnali di controllo e dati con una soluzione basata su un singolo chip. L’MPC8569 include inoltre un nuovo modello di QUICC Engine basato su quattro processori RISC in grado di offrire terminazione, interworking, e switching tra diversi tipi di protocolli di comunicazione a larga banda, inclusi ATM (Asynchronous Transfer Mode), Ethernet, POS (Packet Over Sonet), PPP, e HDLC. La funzionalità di interworking resa disponibile dal QUICC Engine agevola inoltre la transizione dei sistemi ATM verso quelli basati sull’IP consentendo una significativa riduzione dei costi. E’ inoltre fornito supporto per il protocollo IEEE 1588 precision time, utilizzato per la sincronizzazione temporale dei dispositivi collegati ad una rete Ethernet. La famiglia PowerQUICC cui appartiene questo componente è stata espressamente progettata per soddisfare la crescente domanda di componenti per applicazioni a banda larga, come ad esempio stazioni 3G/WiMAX/LTE, controllori per reti radio, gateway, dispositivi per telecomunicazioni di tipo ATM, TDM, ed IP. L’MPC8569 offre al cliente la possibilità di gestire diverse funzioni con il medesimo componente, cosa che in passato era possibile solo con l’utilizzo di diversi componenti separati e specializzati. Inoltre, una soluzione integrata offre anche innegabili vantaggi in termini di minori costi, minori consumi, e maggiore spazio disponibile a livello di PCB. In figura 2 è mostrato uno schema a blocchi del processore, con evidenziate le principali unità funzionali.

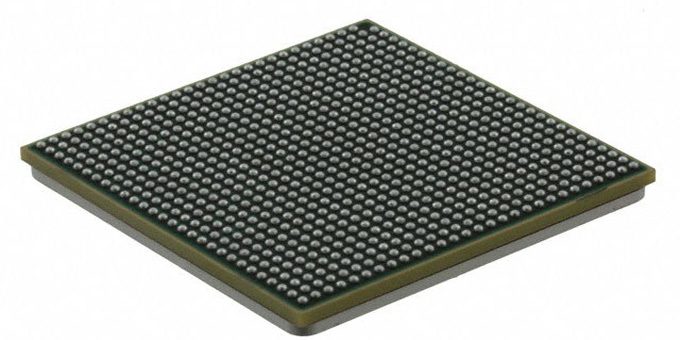

Figura 1: il processore MPC8569E.

Figura 2: schema a blocchi del processore.

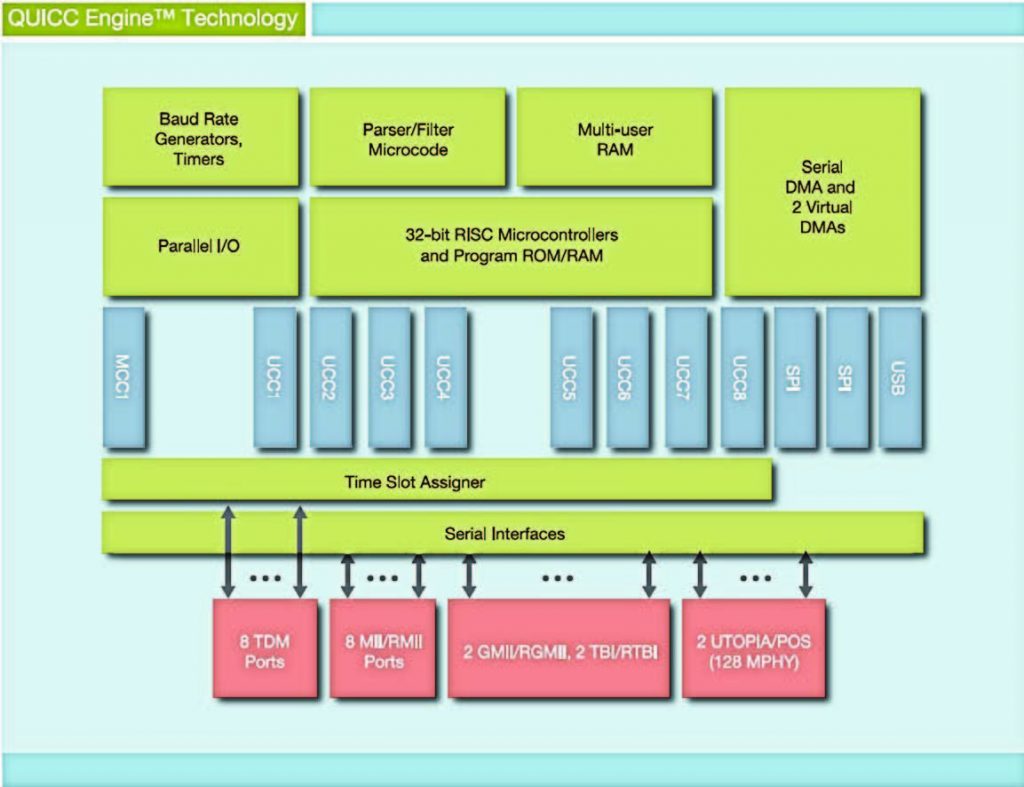

LA TECNOLOGIA QUICC ENGINE

La tecnologia QUICC Engine di Freescale Semiconductor, costruita sulla base dell’architettura Power Architecture, rappresenta un passo significativo all’interno del programma di sviluppo CPM (Communication Processor Module). QUICC Engine comprende un numero scalare di core RISC integrati in grado di fornire un grado di prestazioni tale da soddisfare anche i clienti più esigenti. La versione base del QUICC Engine include 2 processori RISC operanti ad una frequenza di 500 MHz con supporto per numerosi tipi di protocolli, ed offre funzionalità di interwrking con un throughput di 1.2 Gbps; la gamma comprende poi altre funzionalità avanzate, come lo switching, il parsing e l’IP forwarding. Otto controllori unificati per la comunicazione (UCC, si osservi la figura 3) garantiscono il supporto per Fast Ethernet, Gigabit Ethernet, High level Data Link Control (HDLC), Asynchronous Transfer Mode (ATM), Packet Over Sonet (POS).

Figura 3: la tecnologia QUICC Engine.

Otto multiplexer a divisione di tempo (TDM) abilitano la connessione con 8 linee E1/T1, oppure T3/E3. Oltre alle UCC, QUICC Engine supporta controllori di comunicazione multipli e multi-canale (MCC), anche se uno soltanto è oggi disponibile, ed include uno switch Ethernet di livello 2 (L2). Esiste inoltre la possibilità di connettersi a memorie SDRAM e DDR tramite un controllore DMA integrato. La tecnologia QUICC Engine include perciò molte caratteristiche avanzate che la rendono adatta per l’utilizzo attuale e futuro in applicazioni di telecomunicazione a larga banda con e senza fili, come anche sistemi di networking. Ricordiamo infine che QUICC Engine mantiene un elevato grado di compatibilità software con l’architettura originaria PowerQUICC: la compatibilità all’indietro facilita la migrazione da una piattaforma all’altra, riduce i costi di sviluppo, e riduce il time to market.

L’INTERWORKING

L’obiettivo di ogni operatore del settore telecomunicazioni è quello di poter disporre contemporaneamente di traffico dati e voce (telefonia) sulla stessa rete. Ciò è possibile sfruttando la tecnologia basata sui pacchetti IP (Ethernet): in questo modo i dispositivi operanti sulla rete possono interoperare tra flussi di tipo “circuit-switched” e flussi di tipo “packet-switched”, e tra diversi tipi di standard e protocolli. L’interoperabilità tra i protocolli viene chiamata “interworking”. La tecnologia QUICC Engine supporta l’interworking tra ATM ed Ethernet, senza alcun intervento da parte della CPU, secondo la specifica RFC2684. Inoltre, il QUICC Engine supporta l’interworking da MC/MLPPP ad Ethernet, ed è in grado di eseguire funzioni di lookup tra i layer 2 e 4, sempre senza intervento della CPU.

CARATTERISTICHE HARDWARE

Le principali caratteristiche dell’MPC8569, realizzato in tecnologia silicon on insulator (SOI) da 45 nm, sono le seguenti:

- core e500v2 in tecnologia Power Architecture con frequenza pari a 33 GHz, indirizzamento fisico a 36-bit, supporto per la rappresentazione numerica in virgola mobile a doppia precisione

- 32 Kbyte di cache istruzioni e dati di livello 1

- 512 Kbyte di cache di livello 2 con ECC

- QUICC Engine operante alla frequenza di 667 MHz e comprendente: 4 processori RISC, supporto per i protocolli Ethernet, ATM, POS, e T1/E1 e relativo interworking, 4 interfacce Gigabit Ethernet (fino a due con SGMII), fino ad otto interfacce Ethernet 10/100 Mbps, fino a 16 link TDM (Time Division Multiplexing) T1/E1, interfaccia UTOPIA POSPHY L2, supporto per IEEE 1588 v2, USB 2.0 full speed, vari segnali di I/O

- security engine integrato (solo nella versione MPC8569E) con supporto per numerosi protocolli quali: ARC-4, DES, 3DES, AES, RSA/ECC, RNG, Singlepass SSL/TLS, SNOW, MD5, SHA-1/2, Kasumi F8 e F9

- un controllore per memorie

DDR2 / DDR3 SDRAM a 64-bit (o due da 32-bit) con ECC - interfacce di comunicazione ad elevata velocità:RapidIO, PCI Express, SGMII, SerDes

- controllore di interrupt programmabile (PIC) compatibile con lo standard Open-PIC

- controllore DMA a 4 canali

- 2 controllori I2C, DUART, timer, SPI, ed Ethernet PHY

- enhanced local bus controller (eLBC) a 32-bit, operante a 166 MHz

- porta di test/debug IEEE 1149.1 JTAG

- enhanced Secured Digitial Host Controller (eSDHC) per l’interfacciamento con le schede di memoria SD/MMC

- assorbimento contenuto: meno di 7 W alla frequenza di 800 MHz

ARCHITETTURA DEL’MPC8569E

Vediamo ora di esaminare in dettaglio i singoli blocchi funzionali che compongono il processore.

E500V2 CORE

Il cuore dell’MPC8569 risiede in un core a 32-bit di elevate prestazioni realizzato in tecnologia Power Architecture e le cui principali caratteristiche possiamo così riassumere: indirizzamento fisico a 36-bit (spazio di indirizzamento pari a 64 Gbyte), set di istruzioni embedded per il calcolo in virgola mobile (supporto per il tipo vettore a 64-bit e scalare a 32-bit in singola precisione, e per il tipo scalare a 64-bit in doppia precisione), cache istruzioni e dati L1 da 32 Kbyte (entrambe con controllo di parità), 512 Kbyte di memoria cache L2 utilizzabile anche come SRAM. L’MPC8569 può inoltre far parte di un sistema con uno spazio di indirizzamento maggiore attraverso la mappatura di apposite “translation window”, una funzionalità resa disponibile dalle unità ATMU (Address Translation and Mapping Units) in grado di supportare la traslazione degli indirizzi sia in ingresso (inbound) che in uscita (outbound); questa caratteristica permette al processore di far parte di mappe di indirizzamento di grandi dimensioni come quelle relative alle architetture PCI Express e RapidIO.

QUICC ENGINE

Il blocco QUICC Engine fornisce supporto per:

- interfaccia UTOPIA/POS-PHY L2 (fino a 128 porte disponibili), fino a 4 interfacce Gigabit Ethernet, fino a 8 interfacce Ethernet 10/100 Mbps, fino a 16 interfacce seriali T1/E1/J1/E3 o DS3, SPI ed Ethernet PHY, USB 2.0 full/low speed

- protocollo IP (sia Ipv4 che Ipv6), switch Ethernet di livello 2 (utilizzo del mac address oppure delle VLAN tag in accordo allo standard IEEE 802.1p/Q), protocollo ATM (con disponibilità di traffic shaping, Circuit Emulation Service 2.0, IMA sub-layer), Point-to-Point Protocol (PPP), HDLC

- statistiche sia per l’ATM che per l’Ethernet (RMON/MIB)

- IEEE 1588 v2, utillizzato per la sincronizzazione dei real-time clock nei sistemi distribuiti.

- Il QUICC Engine integra 4 processori RISC, in grado di accrescere significativamente le prestazioni del sistema, ed in grado di gestire contemporaneamente un elevato numero di task e thread.

INTEGRATED SECURITY ENGINE (SEC)

Si tratta di un core modulare e scalare per la gestione della sicurezza, ottimizzato per processare tutti gli algoritmi associati a IPsec, IKE, SSL/TLS, iSCSI, SRTP, IEEE 802.11i®, IEEE 802.16® (WiMAX), IEEE 802.1AE® Std. (MACSec), 3GPP, A5/3 per GSM ed EDGE, GEA3 per GPRS, e SNOW 3G (richiesto dai sistemi LTE). Il SEC dispone al suo interno di unità di elaborazione crittografiche, specifiche per i singoli protocolli, che gli permettono di eseguire gli algoritmi con un singolo passaggio dei dati.

CONTROLLORE DI MEMORIA DDR SDRAM

L’MPC8569 dispone di un controllore di memoria DDR a 64-bit (o due a 32-bit) in grado di supportare memorie sia di tipo DDR2 che DDR3, con uno spazio di indirizzamento che può estendersi sino a 16 Gbyte. Sono disponibili 16 segnali di indirizzamento multiplexati che, unitamente a 4 segnali di chip select, consentono di gestire fino a 4 banchi di memoria con densità da 64 Mbyte a 4 Gbyte. Utilizzando poi la modalità “page mode”, si possono aprire contemporaneamente fino a 32 pagine di memoria, riducendo drasticamente i tempi di latenza sugli accessi. Dal punto di vista della sicurezza, grazie all’ECC si possono rilevare e correggere tutti gli errori sul singolo bit e rilevare tutti gli errori su 2 bit, e tutti gli errori all’interno di un nibble. Per quanto riguarda invece il power management, è presente un segnale con cui l’MPC8569 può portare immediatamente la memoria in una modalità sleep a basso assorbimento di potenza.

INTERFACCE DI I/O

Sono disponibili i seguenti tipi di interfacce di I/O ad elevata velocità:

- Serial RapidIO: si tratta di un’interfaccia standard punto-punto ad elevate prestazioni caratterizzata da un numero esiguo di pin e dall’utilizzo della tecnologia di commutazione di pacchetto. Altre proprietà di questa interfaccia sono l’ampia larghezza di banda, la bassa latenza, ed il supporto per metodologie di scambio messaggi basate su mailbox

- PCI Express, conforme alla PCI Express Base Specification Revision 1.0a. Può essere configurato in fase di boot per agire sia come root complex che come endpoint. Il livello fisico del PIC Express opera alla velocità di 2.5 Gbps per canale, con un’ampiezza di banda unidirezionale teorica pari a 2 Gbps per canale; dal momento che le porte di ricezione e trasmissione operano indipendentemente, l’ampiezza di banda aggregata teorica risulta pari a 4 Gbps per canale.

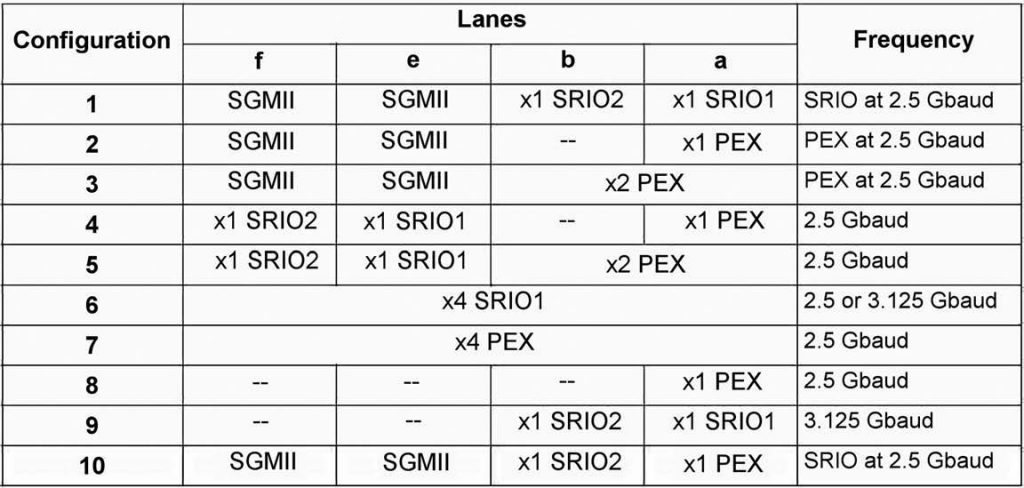

- SGMII: durante il power-on si può selezionare una tra 10 diverse configurazioni, come evidenziato in figura 4.

Figura 4: configurazioni SGMII selezionabili al power-on.

PROGRAMMABLE INTERRUPT CONTROLLER

L’MPC8569 implementa la logica e le strutture di programmazione dell’architettura OpenPIC, fornendo supporto per gli interrupt esterni (con annidamento degli stessi), interrupt associati ai messaggi, interrupt associati a stati logici interni, e timer ad elevata risoluzione. Sono disponibili 16 livelli di priorità degli interrupt. Il modulo PIC può inoltre essere escluso per permettere l’utilizzo di un controllore esterno.

ALTRI DISPOSITIVI

Altri moduli presenti nell’MPC8569 sono:

- controllore di DMA integrato a 4 canali in grado di trasferire dati tra le porte di I/O e la memoria, oppure tra due dispositivi di memoria

- due controllori I2C

- una DUART full-duplex compatibile con i modelli di programmazione PC16450 e PC16550; sia il trasmettitore che il ricevitore supportano code FIFO da 16 byte

- enahnced local bus controller (eLBC) che consente il collegamento con una vasta gamma di memorie esterne, DSP, ASIC, e FPGA. Sono presenti tre macchine a stati separate che condividono gli stessi pin esterni e possono essere programmate separatamente per accedere a diversi tipi di dispositivi.

Per quanto concerne la selezione del dispositivo primario da cui eseguire il boot, il processore può essere configurato in modo tale da avviarsi da una delle seguenti interfacce:

- controllore di memoria DDR2/DDR3

- interfaccia Serial RapidIO

- interfaccia PCI Express

- local bus interface

- I2C boot sequencer

- controllore di memorie SD/MMC.

SISTEMI DI SVILUPPO

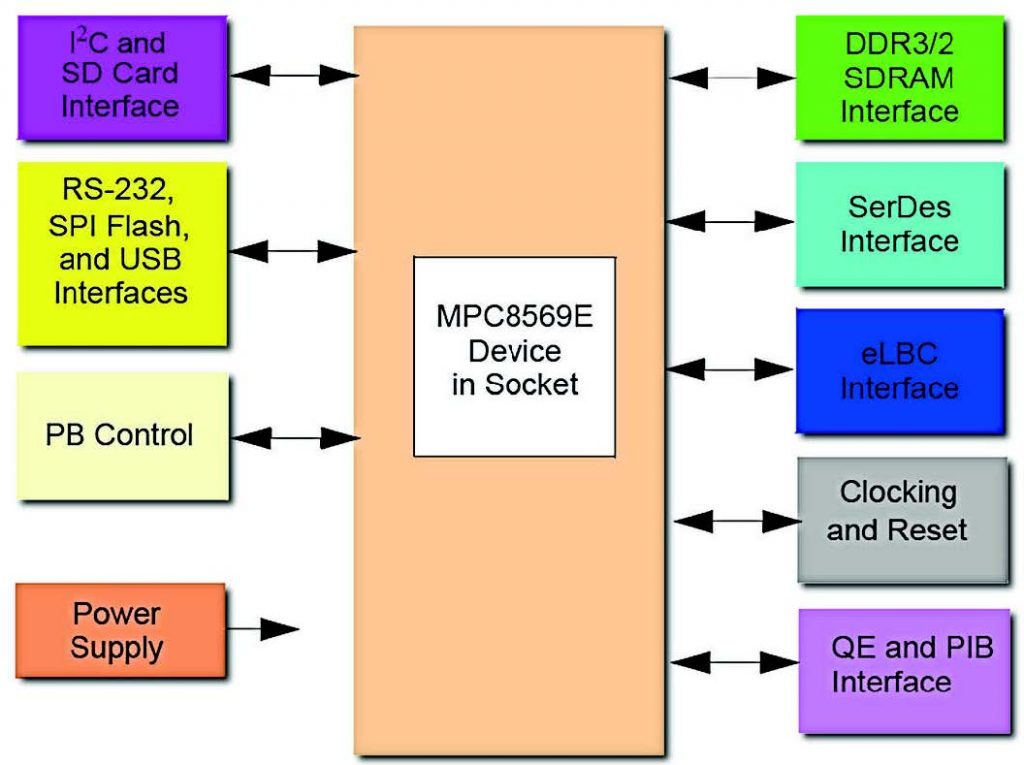

Il principale strumento di sviluppo per questo tipo di processore è rappresentato dal sistema MDS (MPC8569E Modular Development System), espressamente progettato per permettere agli sviluppatori hardware e software di accelerare le fasi di sviluppo e test, riducendo sensibilmente il time to market. L’MDS si compone di diverse board che nel complesso formano un sistema di sviluppo completo:

- scheda processore con il micro MPC8569E

- scheda con i segnali di I/O

- moduli di espansione in grado di fornire supporto per: TDM, ATM, PCI Express. In figura 5 è mostrata la scheda MDS di Freescale, mentre in figura 6 è presentato lo schema a blocchi della board.

Figura 5: la scheda di sviluppo MDS.

Figura 6: schema a blocchi della scheda MDS.

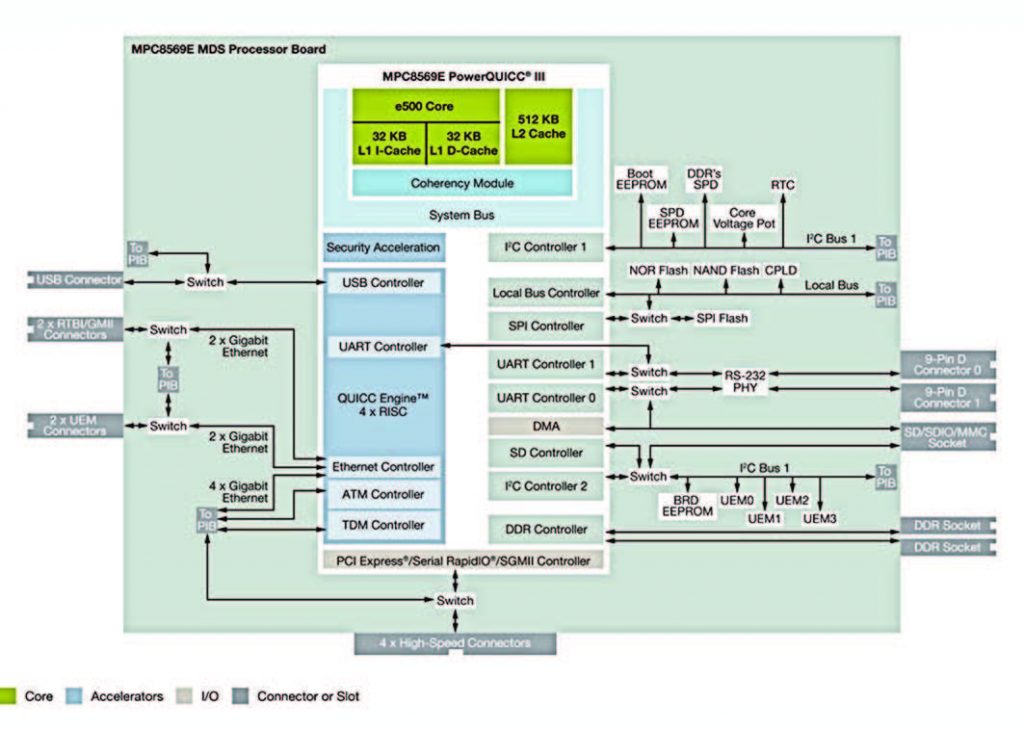

SCHEDA PROCESSORE

Questa board è contraddistinta dalle seguenti caratteristiche:

- processore MPC8569E operante fino a 1.33 GHz, core alimentato a 1.1 V, package FBGA da 783 pin

- memoria DDR3 SODIMM da 1 Gbyte, con frequenza fino ad 800 MHz, senza ECC

- adattatore PCI Express

- due porte Ethernet 10/100/1000 Mbps per il modulo QUICC Engine

- doppio transceiver RS232 connesso alla DUART

- 2 moduli LYNXx1 per l’interfaccia Serial RapidIO

- interfaccia local bus con installati 32 Mbyte di memoria flash NOR e 32 Mbyte di memoria NAND flash, oltre ad una CPLD

- porta di debug con connettore JTAG/COP

- doppio bus I2C per l’accesso a memoria EEPROM e real-time clock (RTC)

- possibilità di accogliere i moduli di espansione PQ-MDS-T1 (16x TDM, 2 x DS3), e PQ-MDS-QOC3 (1 x UTOPIA / POS Level 2)

- USB 0, Real Time Clock (RTC), doppia interfaccia I2C

- memoria EEPROM

- interfaccia per schede di memoria SD/MMC

- interruttori e indicatori a led, interfaccia di debug JTAG

- possibilità di eseguire il power on/off da remoto pilotando appositi contatti della

Le risorse ed i dispositivi di debug presenti sulla scheda processore MDS consentono agli sviluppatori di caricare il software e metterlo in esecuzione, impostare i breakpoint, visualizzare il contenuto dei registri e della memoria, e collegare hardware di tipo proprietario. Può anche essere utilizzata come scheda dimostrativa, dal momento che il programma può risiedere sulla sua memoria flash. La scheda può essere inserita in un normale PC come dispositivo end point PCI Express utilizzando l’adattatore opzionale PCI-PCI Express. In figura 7 è mostrato lo schema a blocchi con le diverse unità funzionali presenti sulla scheda processore MDS.

Figura 7: la scheda processore MDS.

SCHEDA DI I/O

Questa scheda serve ad aggiungere alla scheda processore (Processor Board, PB) dei PHY addizionali oppure altri moduli di valutazione e supporta fino a 4 slot PMC (PCI Mezzanine Card). I moduli PMC possono essere connessi alla PB tramite il PIB, una scheda adattatore con formato AdvancedTCA che include 2 Gigabit Ethernet ottici e 8 MII/RMII Fast Ethernet Base-T.

MODULI DI ESPANSIONE

I moduli di espansione disponibili per MDS sono i seguenti:

- PQ-MDS-T1: supporta le interfacce E1/T1, DS3, T3, con la possibilità di impostare due linee telefoniche analogiche (POTS)

- PQ-MDS-QOC3: supporta fino a 4 transceiver ottici da 155 Mbps per impiego del bus UTOPIA L2/POS

- PQ-MDS-PCI: comprende un connettore PMC-PCI per l’utilizzo di board PCI

- PQ-MDS-PCI Express: modulo di espansione che supporta PCI agent multipli.