Le MCU HCS08 rappresentano un'evoluzione della famiglia HC08, con caratteristiche di throughput decisamente superiori, un rinnovato set d’istruzioni – sebbene compatibile con il precedente – ed un aggiornamento delle principali periferiche. Il funzionamento a tensioni più basse – 3.6V anziché 5 V- permette inoltre di ottenere un aumento delle prestazioni senza aumentare il consumo della MCU. Nel seguito vedremo in dettaglio le principali differenze tra queste due famiglie di MCU.

CPU E MODULO DEBUG

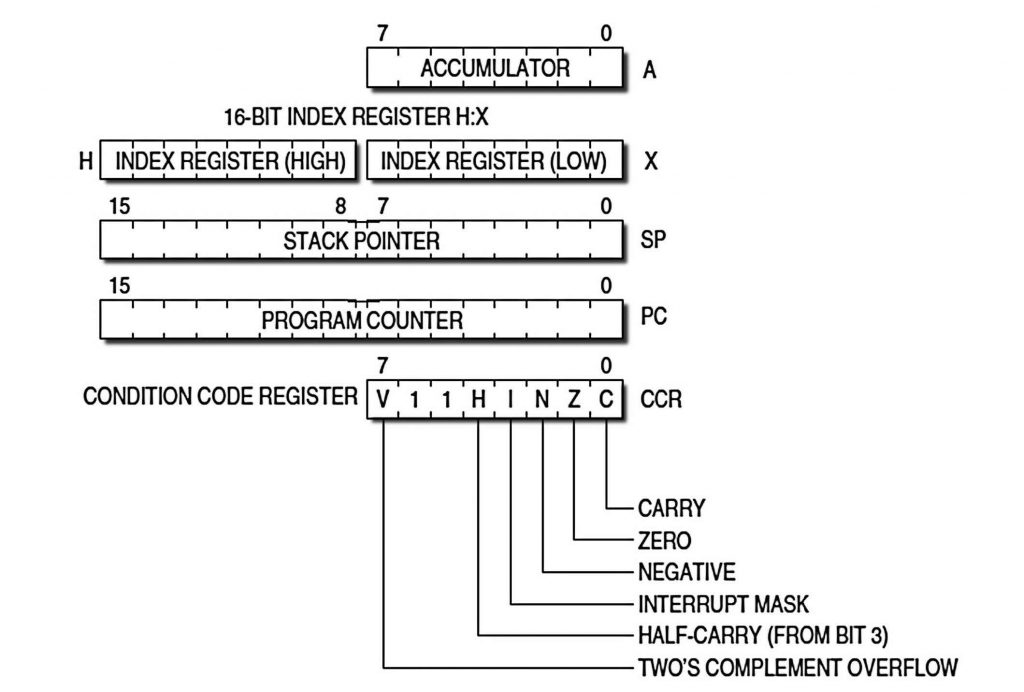

La CPU della famiglia HCS08 deriva dalle CPU 68HC05, a sua volta erede della notissima e storica CPU 6800 di Motorola. Si tratta di processori CISC con architettura di Von Newmann (memoria programma e codice condivisa) ed I/O mappato in memoria. Queste CPU possiedono 5 registri non mappati in memoria:

- Accumulatore ad 8 bit

- Registri indice H:X a 16 bit per l’indirizzamento attraverso indice

- Stack pointer (SP) a 16 bit

- Program Counter (PC) a 16 bit

- Condition Code (CCR) a 8 bit

La CPU può indirizzare fino a 64 kB di memoria come blocco singolo. Le modalità d’indirizzamento, tipiche di un processore CISC, sono le seguenti:

- Inerente (INH)

- Relativo con offset di 8 bit (REL)

- Immediato (IMM)

- Diretto (DIR)

- Esteso, in un punto qualsiasi dello spazio degli indirizzi di 64 KB (EXT)

- Indicizzato tramite H:X, con 5 sottomodalità con o senza offset di 8 o 16 bit e con o senza l’autoincremento (IX, IX+, IX1, IX1+, IX2)

- Indicizzato tramite SP con offset di 8 o 16 bit (SP1, SP2)

In figura 1 è riportato il modello di programmazione della CPU HCS08.

Figura 1: modello di programmazione della CPU HCS08.

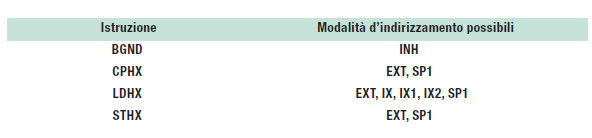

La gestione degli interrupt è identica sia che si tratti di interrupt hardware, generati da una periferica come un timer, che software –generati dall’istruzione SWI. Il contenuto dei registri PC, X, Accumulatore e CCR viene salvato nello stack. Per compatibilità con le MCU HC08, il contenuto del registro H non viene salvato, per cui è buona norma salvarlo all’inizio della routine di gestione dell’interrupt (ISR) e ripristinarlo alla fine. La CPU degli HCS08 comprende alcune nuove modalità d’indirizzamento attraverso indice, utili per aumentare l’efficienza dei compilatori C. Sono state aggiunte nel complesso 4 nuove istruzioni per un totale di 10 opcodes. I mnemonici delle nuove istruzioni sono riportati nella tabella 1.

Tabella 1: nuove istruzioni della CPU HCS08.

Per alcune delle istruzioni della CPU degli HCS08 è richiesto un numero di cicli inferiore rispetto alle CPU HC08, ma per molte altre il tempo di esecuzione è aumentato di 1 o 2 cicli. Ciò nonostante, il throughput della nuova CPU è in generale superiore grazie al fatto che la velocità del bus è stata portata fino a 20 MHz (con un clock di 40 MHz per la CPU), mentre nel caso degli HC08 era limitata a 8 MHz. Il clock del bus per gli HC08 è uguale al clock della CPU, mentre per gli HCS08 è pari alla metà, quindi 20 MHz alla velocità di clock massima di 40 MHz. Si noti che i tempi di ciclo della CPU sono relativi al clock del bus. Queste modifiche comportano peraltro lo svantaggio di modificare le routine di ritardo che fanno uso di loop di istruzioni: per tale motivo è fortemente consigliato l’utilizzo di timer per questo scopo. Il background debugger degli HCS08 Il supporto per l’in-circuit debugging degli HCS08 è stato completamente rinnovato. Negli HC08, l’ICD è eseguito nella cosiddetta modalità monitor: una combinazione di hardware e software, contenuto in una porzione di memoria ROM detta monitor. In questa modalità, i vettori di reset e dell’istruzione SWI (Software Interrupt) sono redirezionati in modo da eseguire il programma monitor anziché il programma utente. Ciò comporta un’alterazione del normale flusso d’esecuzione del programma, oltre a richiedere che una porzione di memoria (all’incirca 200 Byte) sia occupata dal programma monitor. Nella modalità debug sono disponibili 5 comandi: READ, WRITE, IREAD, IWRITE, e RUN.Gli HCS08 possiedono invece una modalità di debug detta Background debug. Il circuito di supporto per l’ICD è implementato tramite due moduli, il Background Debug Controller (BDC) e l’InCircuit Emulator (ICE). Inoltre non è necesario un firmware apposito nella memoria Flash. Il BDC si occupa di gestire l’interfaccia con l’esterno tramite un pin apposito. Mette a disposizione 30 comandi, tra cui 13 non invasivi che permettono un accesso diretto alla memoria della MCU. Il BDC può utilizzare il clock del bus o –se di frequenza troppo bassaun clock esterno. Il modulo ICE comprende le funzionalità principali di un emulatore, tra cui:

- Due tipi di breakpoint o trigger: su istruzione o su indirizzo.

- Due trigger in grado di scattare su due indirizzi o su un indirizzo ed un dato.

- Nove modalità di trigger.

- Un capture buffer in grado di memorizzare 8 word che può catturare gli indirizzi di cambi del flusso di esecuzione o dati relativi ad eventi.

Queste funzionalità interne al chip permettono di evitare la necessità dell’uso di un costoso emulatore esterno, che peraltro può funzionare in maniera non perfettamente corrispondente al dispositivo reale.

GESTIONE DELLA MEMORIA

Negli HC08 una porzione di memoria ROM è utilizzata dal programma monitor ed eventualmente da altro firmware per la programmazione della Flash interna. Negli HCS08, la disponibilità del background debugger ha reso non più necessaria questa memoria. Programmazione della memoria Flash Gli HCS08 possiedono un’interfaccia semplificata verso la memoria Flash, denominata Flash Command Interface, che permette la programmazione di blocchi di memoria Flash in modo da poterla usare come EEPROM o per la riprogrammazione sul campo. I vantaggi principali di questa nuova interfaccia rispetto a quella degli HC08 sono i seguenti:

- La programmazione di un byte della Flash richiede 6 passi, mentre negli HC08 ne sono richiesti 13, 4 dei quali richiedono un ritardo generato dall’utente.

- Tutte le temporizzazioni per la programmazione della Flash sono generate automaticamente.

- È disponibile una funzionalità di controllo errore in caso di non esecuzione corretta della procedura di programmazione. Anche la EEPROM utilizza la nuova interfaccia semplificata di programmazione.

PROTEZIONE DELLA MEMORIA E VECTOR REDIRECTION

Gli HCS08 dotati di memoria Flash possiedono una funzionalità di redirezione dei vettori (vector redirection), non presente negli HC08. Questa funzionalità è disponibile nel caso in cui sia utilizzata la protezione della memoria Flash. Mediante la vector redirection è possibile redirezionare i vettori d’interruzione (tranne il vettore di reset) verso una porzione di memoria non protetta. In un’applicazione che preveda un upgrade del firmware sul campo, ad esempio, è possibile mantenere protetta un’altra porzione di memoria comprendente il vettore di reset di modo che, se anche la procedura di aggiornamento non andasse a buon fine, rimarrebbe disponibile una porzione minima di codice in grado di rieseguire l’aggiornamento.

I CAMBIAMENTI NELLE PERIFERICHE

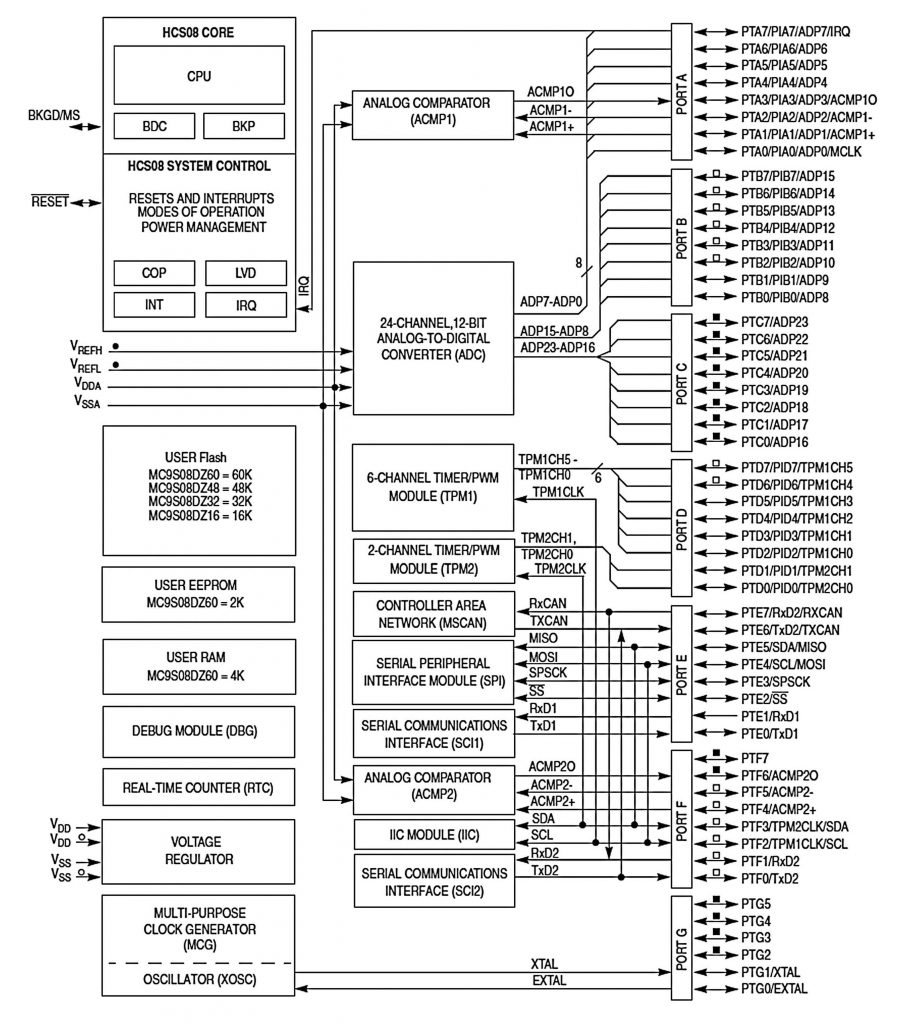

Gli HCS08 comprendono numerosi aggiornamenti delle periferiche già presenti negli HC08, e qualche nuova periferica. Ovviamente le differenze nelle funzionalità delle periferiche comportano una diversa configurazione dei registri e quindi la riscrittura di parte del firmware, in particolare le routine di configurazione e le ISR. In figura 2 è riportato lo schema a blocchi di una MCU avanzata della famiglia HCS08, il dispositivo MC9S08DZ60.

Figura 2: schema a blocchi dell MCU MC9S08DZ60.

GENERATORI DI CLOCK

Per gli HCS08 sono stati sviluppati tre nuovi moduli generatori di clock:

- Internal Clock Generator (ICG), evoluzione del modulo ICG degli HC08.

- Internal Clock Source (ICS), un nuovo modulo generatore meno sofisticato.

- Multi-Purpose Clock Generator (MCG), un misto tra i moduli ICG ed ICS precedenti, disponibile sulle MCU HCS08 più avanzate.

INTERNAL CLOCK GENERATOR (ICG)

Il modulo ICG comprende un FLL (Frequency Locked Loop) per poter generare più frequenze a partire da una singola sorgente di clock. Il modulo ICG degli HCS08 ha 4 modalità di funzionamento

- Self-clocked mode (SCM)

- FLL-engaged internal reference (FEI)

- FLL-engaged external reference (FEE)

- FLL-bypassed external reference (FBE) negli HC08 sono presenti invece le sole modalità FEI e FBE.

Inoltre, negli HCS08 è possibile usare oltre ad un fattore moltiplicatore nelle modalità che utilizzano il FLL, anche un fattore di divisione in tutte le modalità.

INTERNAL CLOCK SOURCE (ICS)

Questo modulo è una variante del modulo ICG, privo però della modalità SCM. Inoltre non è disponibile un fattore di divisione del FLL ma si può utilizzare un divisore per la frequenza di bus. è richiesta inoltre una frequenza di riferimento compresa tra 31.25 e 39.0625 kHz come ingresso del FLL; il modulo ICG può invece usare qualsiasi frequenza tra 32 e 100 kHz oppure tra 2 e 10 MHz.

MULTI-PURPOSE CLOCK GENERATOR (MCG))

Il modulo MCG è come detto un misto tra i moduli ICG ed ICS. Possiede le seguenti modalità di funzionamento:

FLL-engaged internal (FEI)

FLL-engaged external (FEE)

FLL-bypassed internal reference (FBI)

FLL-bypassed external reference (FBE)

PLL-engaged external (PEE)

PLL-bypassed external reference (PBE)

FLL-bypassed internal reference low power (FBILP)

FLL-bypassed external reference low power (FBELP)

Il modulo MCG è incluso solo nelle MCU HCS08 di fascia alta e può essere confrontato con il modulo CGM (Clock Generator Module) delle MCU HC08 highend, il quale però comprende solo un PLL ed è privo del FLL.

TIMER E PWM (TPM)

Gli HCS08 includono un nuovo modulo timer/PWM (TPM), più completo e versatile del modulo timer (TIM) degli HC08. I vantaggi principali di questo nuovo modulo sono i seguenti:

- Modalità di conteggio up/down anziché solo up.

- Una sorgente aggiuntiva di clock: external clock.

- 8 valori di prescaler invece di 7.

- Possibilità di generare segnali PWM center-aligned.

- PWM bufferizzato su qualsiasi canale singolo invece che su coppie di canali.

In particolare, i passi per poter configurare un PWM bufferizzato nel caso degli HCS08 sono i seguenti:

- Fermare il TPM ponendo a 0:0 i bit CLKSB:CLKSA nel registro TPMxSC. Settare anche il prescaler bit PS2:PS1:PS0 ed il bit CPWMS se si vuole un PWM center-aligned.

- Scrivere il periodo del PWM desiderato nei registri:

TPMxMODH:TPMxMODL - Scrivere il valore desiderato del duty-cycle nei registri TPMxCnVH: TPMxCnVL di un canale n qualsiasi.

- Se è stato selezionato un PWM edgealigned, settare il bit MSnB del registro TPMxCnSC. Scrivere 1:0 nei bit ELSnB:ELSnA per cancellare l’output compare o X:1 per settarlo.

- Selezionare la sorgente di clock tramite i bit CLKSB:CLKSA nel registro TPMxSC: il timer verrà avviato.

- Per aggiornare il duty-cycle, scrivere il nuovo valore desiderato nei registri TPMxCnVH: TPMxCnVL.

Le altre modalità di funzionamento del TPM, input capture e output compare, sono configurate in maniera simile.

SERIAL PERIPHERAL INTERFACE (SPI)

Il modulo SPI (Serial Peripheral Interface) è sostanzialmente simile a quello degli HC08. Alcuni miglioramenti sono i seguenti:

- 8 rapporti di prescaling ed 8 baud rate selezionabili.

- Ricevitore con doppio buffer.

- Configurabile nella modalità di trasmissione/ricezione LSB first oltre che MSB first.

- Modalità bidirezionale (singolo filo anziché due fili per TX ed RX).

Altre differenze riguardano soprattutto diversi flag di interrupt per le condizioni d’errore.

INTER-INTEGRATED CIRCUIT (IIC)

Il modulo IIC degli HCS08 è derivato da quello delle MCU a 16bit HCS12. Tra le differenze principali con il modulo IIC degli HC08 abbiamo:

- 64 possibili frequenze di clock anziché 8.

- ndirizzamento con 10 bit oltre che con 7 bit.

- Riconoscimento di una general call all’indirizzo $00.

- Uso di un solo registro sia per trasmettere che per Per questo motivo, anche il flag TCF (Transfer Complete) è uno solo.

- Un solo flag IICIF per Transmit Empty, Receive Full e Arbitration Al contrario, gli HC08 usano tre flag separati.

- Non supporta l’SMBus.

CONTROLLER AREA NETWORK (MSCAN)

I moduli CAN degli HC08 e degli HCS08 supportano le versioni 2A e B del protocollo CAN. Inoltre, entrambi hanno un triplo buffer di trasmissione, un filtro di identificazione mascherabile e funzionalità di segnalazione e di interrupt per tutti gli stati di errore in trasmissione e ricezione. Il modulo CAN degli HCS08 presenta le seguenti modifiche rispetto a quello degli HC08:

- Modalità listen per monitorare il CAN bus.

- Bus off recovery programmabile.

- Timer interno per l’etichettatura temporale.

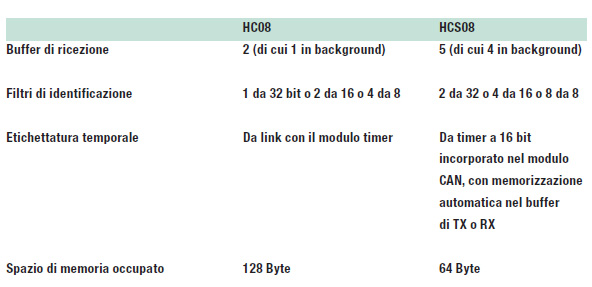

Nella tabella 2 sono riportate le differenze nell’implementazione del modulo CAN tra le due famiglie.

Tabella 2: differenze tra i moduli CAN delle MCU HC08 e HCS08.

SERIAL COMMUNICATIONS INTERFACE (SCI)

Il modulo SCI degli HCS08 è derivato da quello degli HCS12. Poiché gli HC08 possiedono due tipi di moduli SCI, standard ed enhanced (ESCI), faremo la comparazione con il modulo standard. Le differenze principali tra i moduli degli HCS08 e degli HC08 sono le seguenti:

- Lo SCI degli HCS08 ha un registro baud rate di 13 bit, che permette perciò 8191 diversi valori di baud Gli HC08 usano un prescaler ed un baud rate su 3 bit che permettono un totale di 32 combinazioni.

- Il baud rate massimo degli HCS08 è pari alla frequenza di bus ÷64 (312500 baud massimi), quello degli HC08 è pari alla frequenza di bus ÷16 (500000 baud massimi).

- Gli HCS08 supportano una modalità a singolo filo.

- Gli HC08 possono invertire i dati trasmessi mediante un bit di controllo, gli HCS08 no.

CONVERTITORI ANALOG-TO-DIGITAL (ADC)

Per la famiglia HCS08 sono state implementate due nuove versioni del modulo ADC: una versione di base ed una più recente disponibile sulle MCU più avanzate. In entrambi i casi si tratta convertitori ADC ad approssimazione successiva (SAR) a 10 bit, dotati di sample & hold. Le differenze tra il modulo ADC di base ed i moduli ADC tipici delle MCU HC08 sono le seguenti:

- In aggiunta ad ogni pin di ingresso dell’ADC è presente un pin di enable, di modo che il pin ADC non possa essere attivato erroneamente tramite l’usuale channel select software.

- È previsto un bit di power on/off separato per ogni canale d’ingresso.

- Oltre alla modalità a 10 bit con segno, è prevista una modalità di conversione ad 8 bit con segno.

- La frequenza di clock massima del modulo ADC è di 2 MHz anziché di 1 MHz come per gli HC08.

- Sono disponibili 16 valori di prescaling della frequenza di clock invece di 5.

- Il modulo ADC degli HCS08 può usare solo la frequenza di bus come clock. Inoltre, ogni conversione richiede 28 cicli del clock ADC invece dei 17 cicli degli HC08. Tuttavia, grazie alle frequenze più elevate degli HCS08, il massimo sample rate è di 71000 sps invece dei 59000 sps degli HC08.

ANALOG COMPARATOR (ACMP)

Il modulo Analog Comparator è nuovo per gli HCS08. Non c’è pertanto un equivalente negli HC08. Le caratteristiche principali di questo modulo sono:

- Può confrontare due tensioni esterne od una tensione esterna ed un riferimento interno.

- L’uscita del comparatore è alta quando il segnale sul pin non invertente è maggiore di quello sul pin invertente, al contrario è bassa.

- Opera su una gamma di tensioni railto-rail (escursione pari alla tensione di alimentazione).

- L’uscita del comparatore è prelevabile, opzionalmente, su un pin di output.

- Può generare un interrupt sul fronte di salita, sul fronte di discesa o su entrambi.

CONCLUSIONI

Le più recenti MCU della famiglia HCS08 rappresentano un notevole miglioramento delle MCU HC08, soprattutto in termini di prestazioni grazie alle frequenze di clock superiori. Le periferiche sono state in genere potenziate ed il loro uso semplificato. Molto utile per lo sviluppatore il nuovo modulo per il debug in-circuit in grado di sostituire un eventuale e costoso emulatore esterno. D’altro canto, la riorganizzazione dei vari moduli richiede generalmente una riscrittura parziale del firmware, almeno per quanto riguarda le funzioni di basso livello che fanno uso direttamente dell’hardware del dispositivo.