Intelligent i/o è una periferica integrata nei micro renesas della famiglia mc32/80 che rende disponibili moduli per eseguire misure di tempo, generare segnali di controllo temporizzati, gestire protocolli di comunicazione standard.

Intelligent I/O è una periferica integrata nei microcontrollori della serie M32C/80 che rende disponibili funzionalità per misure di tempo, generazione di forme d’onda, gestione di interfacce di comunicazione standard. La periferica comprende nella configurazione più generale fino a 4 gruppi, ognuno dei quali include le seguenti due unità: Time Measurement Unit, Communication Unit.

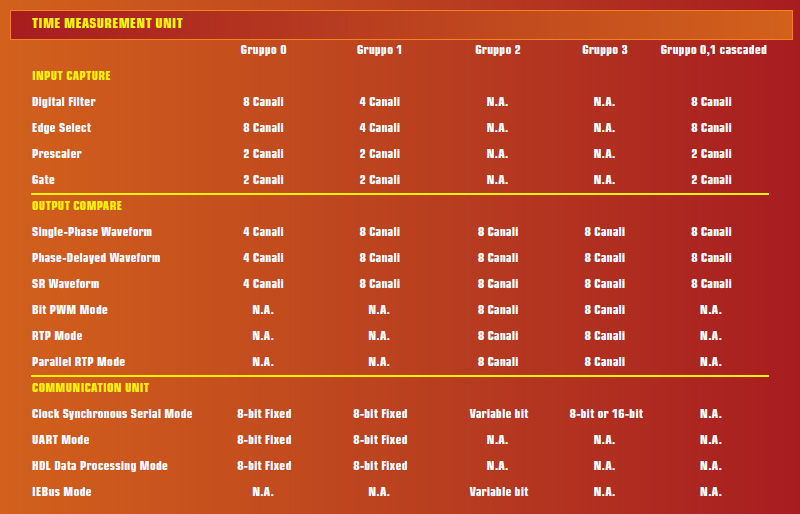

In funzione del tipo di microcontrollore selezionato e della configurazione hardware della periferica presente, tutte o soltanto alcuni dei gruppi e delle funzionalità supportate da questi sono implementati. La tabella 1 riassume le diverse configurazioni in cui la periferica Intelligent I/O è disponibile.

TABELLA 1 – CONFIGURAZIONE DEI GRUPPI DELLA PERIFERICA INTELLIGENT I/O

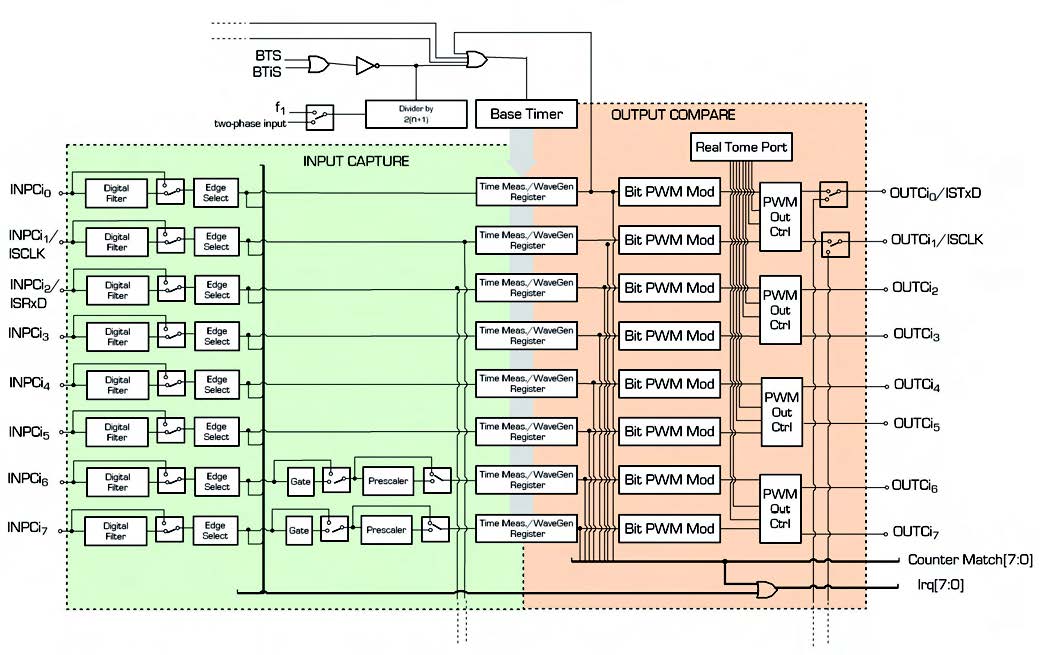

Time Measurement Unit

La figura 1 mostra un’architettura di principio della Time Measurement Unit in cui sono riportati quasi tutti i moduli presenti nei diversi gruppi; come già osservato, la reale configurazione resa disponibile in un particolare gruppo è descritta nella tabella 1.

Figura 1: time Measurement Unit

Come mostrato nella figura, la Time Measurement Unit integra:

➤ il Base Timer Register

➤ il modulo Input Capture

➤ il modulo Output Compare

➤ i registri T ime Measurement Register/Waveform Generation Register

Il Base Timer Register, in particolare, è un contatore a 16-bit con abilitazione e modalità di tipo up o down configurabili mediante apposite istruzioni. Il clock di conteggio può essere derivato dall’oscillatore della CPU mediante prescaler a 5 bit oppure da un segnale esterno attivo su entrambi i fronti. Il contatore può essere configurato in modo da inizializzarsi a zero automaticamente quando raggiunge il fondo-scala oppure quando uguaglia il valore del Waveform Generation Register a 0. E’ possibile accedere al registro in lettura e scrittura; nel primo caso viene restituito il valore corrente, nel secondo viene invece configurato il valore da cui riprendere il conteggio. I Timer appartenenti ai gruppi 0 e 1 possono essere configurati in cascata in modo da realizzare un contatore a 32 bit. L’Input Capture consente l’acquisizione di segnali di trigger esterni. In corrispondenza dell’evento di trigger, il valore del Base Timer Register viene memorizzato nel Time Measurement Register del canale e viene generato un interrupt al processore; si è in grado così di effettuare semplici misure di frequenza di un segnale esterno o di distanza temporale tra due eventi. La catena di acquisizione del segnale di trigger integra i seguenti elementi:

1- Digital Filter: abilitabile, consente di filtrare impulsi di durata inferiori a tre cicli del clock del Base Timer e rigettare così eventi spuri legati a rumore sulla linea di ingresso.

2- Edge Select: consente di selezionare il fronte attivo del segnale da utilizzare come evento di trigger; in alternativa è possibile abilitare entrambi i fronti in modo da rilevare una qualunque transizione del segnale in ingresso.

3- Gate: abilitabile, consente di mascherare eventi di trigger successivi alla prima occorrenza; il trigger può essere riabilitato mediante opportuna istruzione o quando il Base Timer Register eguagli il valore indicato nel Waveform Generation Register del canale di uscita associato.

4- Prescaler: consente di ridurre la frequenza di trigger di un fattore N programmabile fino a 255.

Il modulo di Output Compare include, invece, le seguenti funzionalità:

■ 1- Single-phase Waveform Output: disponibile nei gruppi 0,1,2 e 3, consente di generare in uscita una forma d’onda quadra con duty cycle programmabile; il segnale viene pilotato nel livello alto quando il Base Timer Register è uguale al valore configurato nel Waveform Generation Register associato, mentre viene forzato basso quando il timer assume il valore zero.

■ 2- Phase-delayed Waveform Output: disponibile nei gruppi 0,1,2 e 3, commuta il valore del segnale di uscita ogni volta che il Base Timer Register è uguale al valore configurato nel Waveform Generation Register associato.

■ 3-Set-Reset Waveform Output: disponibile nei gruppi 0,1,2 e 3, definisce mediante due Waveform Generation Register gli istanti di commutazione (rispetto al valore assunto dal Base Timer Register) dei due fronti del segnale di uscita.

■ 4- PWM Bit-Modulation: disponibile nei gruppi 2 e 3, implementa un controllo PWM in grado di supportare elevate frequenze portanti.

■ 5- Real-Time Port Output: disponibile nei gruppi 2 e 3, utilizza un registro dati a 8-bit ed N Waveform Generation Register; quando il valore del Base Timer Register

uguaglia quello configurato nel Waveform Generation Register i-mo, il corrispondete bit del registro dati viene pilotato sulla porta di uscita associata. Può essere utilizzato per attivare controlli secondo una predefinita sequenza temporale.

■ 6- Parallel-Real Time Port Output: disponibile nei gruppi 2 e 3, utilizza un registro dati a 8-bit e N Waveform Generation Register; quando il valore del Base Timer Register uguaglia uno qualunque di quelli configurati nei Waveform Generation Register, il valore del registro dati viene pilotato parallelamente sulle linee di uscita. In è descritta la procedura di configurazione della periferica Intelligent I/O per utilizzare le funzionalità descritte di Output Compare nella realizzazione di un controller per motori stepper.

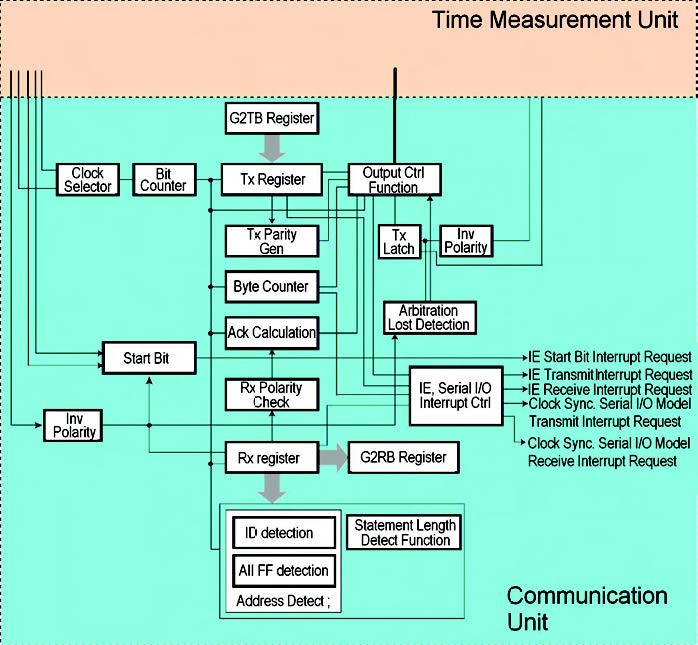

Communication Unit

La Communication Unit include le seguenti interfacce di comunicazione:

➤ seriale asincrona, disponibile nei gruppi 0 e 1;

➤ seriale sincrona, disponibile nei gruppi 0,1 e 2;

➤ HDLC standard, disponibile nei gruppi 0 e 1;

➤ IEBus, disponibile nel gruppo 2.

La figura 2 mostra, ad esempio, l’architettura del gruppo 2.

Figura 2: la Communication Unit del gruppo 3.

Le operazioni dell’unità richiedono alcune delle funzioni della Time Measurement Unit. L’interfaccia di comunicazione seriale asincrona, in particolare, utilizza segnali di clock per la serializzazione/deserializzazione dei caratteri generati mediante funzioni di Phase-delayed Waveform Output. In trasmissione il clock viene generato all’atto della scrittura del carattere nel registro di uscita, in ingresso, invece, è abilitato qualora una transizione della linea in ingresso rilevi una sequenza di start. Con una frequenza di clock di sistema di 30 MHz si è in grado di sostenere un data-rate fino a 5 Mbps. Il controller UART integrato nella periferica Intelligent I/O gestisce in trasmissione l’introduzione dei bit di start e stop ed in ricezione il controllo di eventuali errori di over-run e framing. Allo stesso modo il controller HDLC implementa in hardware le funzionalità di bit stuffing, flag detection, abort detection e calcolo/verifica del CRC richieste dal protocollo. L’interfaccia di comunicazione seriale, infine, può essere configurata in modalità master o slave generando in uscita o richiedendo in ingresso il segnale di clock; nel primo caso viene utilizzato un canale Wa veform Output Compare analogamente alla gestione del controller UART. La larghezza di parola, a seconda della configurazione della periferica Intellignet I/O, può essere programmata in 8 o 16 bit; in alcuni casi è supportata una interfaccia con numero di bit variabile.