Caratteristiche, architettura e prestazioni della CPU V850 di Renesas, la quarta generazione di microcontrollori per applicazioni automotive basati su CPU V850. Realizzati in tecnologia flash MONOS a 90 nm (Metal-Oxide-NitrideOxide-Silicon), i dispositivi garantiscono una capacità di calcolo di 2.5 DMIPS/MHz e supportano una massima frequenza di clock di 200 MHz.

La famiglia guarda al segmento di dispositivi high-end (figura 1) ed estende il portafoglio di soluzioni Renesas basate su CPU V850, che già includeva soluzioni di fascia bassa e ASSP (Application Specific Standard Product). In generale, i microcontrollori delle serie V850 si caratterizzano per le elevate prestazioni nel segmento di riferimento, bassa dissipazione di potenza ed elevata compatibilità elettromagnetica.

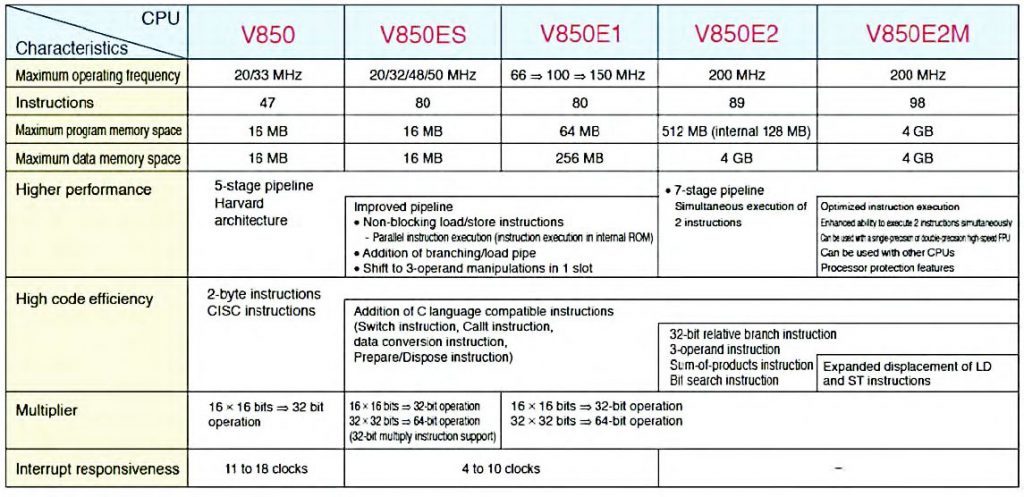

La CPU V850 è corredata da un ampio insieme di periferiche che include host USB 2.0, porte UART/LIN, CSI ed I2C multi-canale, Ethernet MAC 10/100, PWM controller a 16 bit/6 fasi, ADC a 12 bit, controller DMA a 4 canali, circuito Power-On Clear con clock monitor e funzionalità LVI (Low Voltage Indicator), debugger on-chip JTAGcompliant. Di seguito è presentata una descrizione più dettagliata delle caratteristiche e delle prestazioni del core V850. La figura 2 riassume in forma tabellare tali aspetti.

Figura 1: la quarta generazione di micro basati su CPU V850.

Figura 2: caratteristiche e prestazioni delle CPU V850.

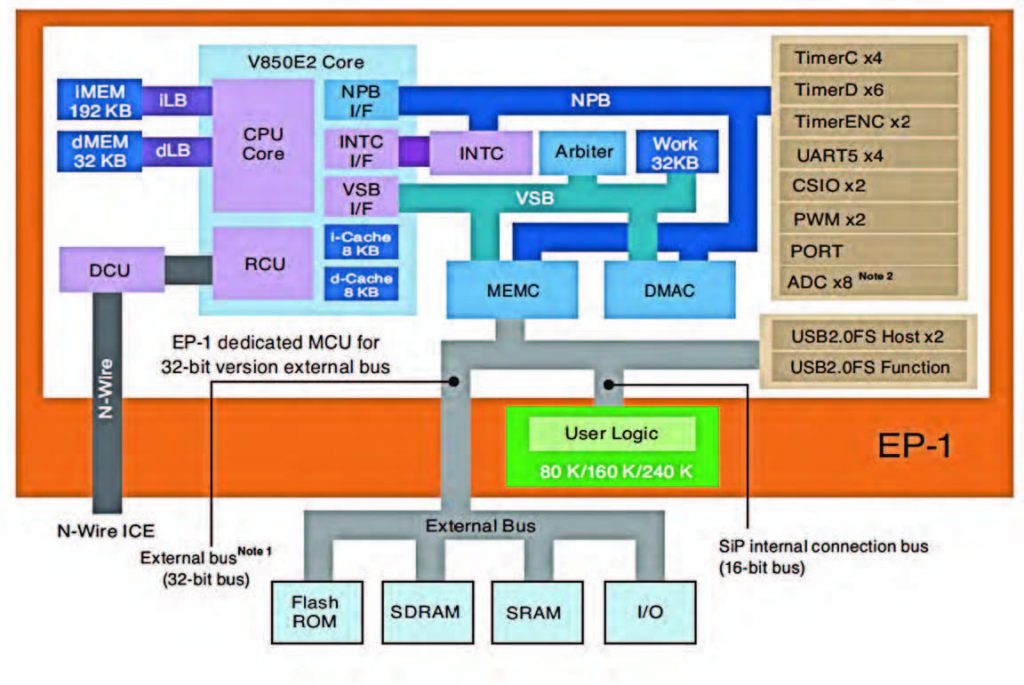

Figura 3 architettura dei dispositivi PFESiP flessibilità a basso rischio.

5 STADI DI PIPELINE ED ARCHITETTURA HARVARD PER LA VERSIONE BASE

La versione base V850 è caratterizzata da pipeline in 5 stadi ed architettura Harvard per l’accesso in memoria. La disponibilità di bus separati per lo spazio dati e programma, assicura elevate prestazioni evitando lo stallo della pipeline nel caso di accessi simultanei degli stadi IF (Instruction Fetch) e MEM (Memory Access to Target address). La CPU è in grado di eseguire la maggior parte delle operazioni in un singolo ciclo di clock. La dimensione massima dello spazio programmi e dati indirizzabile è di 16 MByte. L’insieme di registri include 32 registri generici, come la maggior parte dei sistemi oggi in commercio. Sembra, infatti, essere questa la dimensione ottimale del Register File. L’analisi di applicazioni tipiche mostra che, oltre tale valore, la riduzione della dimensione del programma compilato e l’incremento di prestazioni conseguenti all’aumento del numero di registri interni tendono ad appiattirsi, rendendo più pesanti, nel contempo, le operazioni di salvataggio del contesto nella gestione delle interruzioni e delle richieste di task switching. La CPU V850, in effetti, consente di definire in fase di compilazione il numero di registri effettivamente utilizzabili dall’applicativo scegliendo tra i valori 22, 26 e 32. Le modalità di indirizzamento supportate sono piuttosto semplici per consentire di operare a più elevate frequenze di clock della pipeline; come noto la massima frequenza di clock è dettata dal massimo ritardo di propagazione dello stadio di pipeline più lento. Nel caso d’indirizzamento in memoria programmi, la CPU V850 prevede le modalità di indirizzamento registro indiretto (in cui l’indirizzo successivo è specificato dal contenuto del registro generico indicato nell’istruzione) oppure relativo (il valore corrente del PC viene incrementato del valore esteso di segno specificato dall’istruzione). L’indirizzamento degli operandi è, invece, di tipo registro, immediato, based e bit addressing. In questi ultimi due casi, in particolare, l’indirizzo destinazione è ottenuto sommando un certo offset all’indirizzo base presente in un registro generico; offset e registro di base sono entrambi definiti dall’istruzione corrente. L’insieme di istruzioni supportato dalla CPU V850 prevede istruzioni a 16 bit per assicurare compattezza del codice compilato, confrontabile con quella delle architetture CISC a 16 bit. Sono previste istruzioni specifiche per la manipolazione di singoli bit come test, set, clear ed invert. L’ALU dispone poi di un barrel shift e di una unità Mulitply/Sum-Of-Product a 16 bit, con accesso diretto al Register File in grado di eseguire moltiplicazioni in 1 o 2 cicli di clock e somme di prodotto in 3 cicli. Prove comparative eseguite da Renesas, su programmi rappresentativi, mostrano un incremento delle prestazioni di un fattore fino a 2,5 per quanto concerne le prestazioni in applicazioni di calcolo aritmetico rispetto a dispositivi analoghi a 16 bit; le prestazioni della CPU V850 sono confrontabili con quelle di dispositivi a 32 bit operanti a frequenza doppia. Il tempo di esecuzione medio delle istruzioni, per un modello con frequenza di clock 20 MHz, è misurato in 50 ns, garantendo così 1 istruzione per ciclo. Dispositivi analoghi della serie 78k4 (CPU CISC a 16 bit) mostrano un tempo medio di esecuzione per istruzione (alla stessa frequenza di clock) di 125 ns.

MIGLIORI PRESTAZIONI CON LE SERIE E1 ED ES

Le CPU V850E1 e V850ES si basano sulla versione V850 ed introducono alcune modifiche per consentire di ottenere prestazioni più elevate (in termini, ad esempio, di numero di operazioni per secondo e riduzioni del tempo di risposta alle interruzioni) e maggiore efficienza del codice. La pipeline, in particolare, è modificata per evitare lo stallo nell’esecuzione di certe sequenze di istruzioni load/store e la destinazione di salto è calcolata nella fase di ID (Instruction Decode) riducendo di 1 ciclo di clock la penalità di salto. Inoltre, grazie alla larghezza di bus interna a 32 bit, è possibile leggere mediante un solo accesso in memoria programma l’istruzione di salto e quella successiva. Lo stesso insieme di istruzioni, poi, è esteso per includere istruzioni di ‘altolivello’ come swicth (corrispondente all’analoga istruzione in linguaggio C) o callt/ctret (per il salto mediante riferimento in tabella). La CPU V850E1 estende lo spazio d’indirizzamento programma fino a 64 MByte e quello dati fino a 256 Mbyte, supporta frequenza di clock fino a 150 MHz per una capacità di calcolo di 32 MIPS per applicazioni high-end. La versione V850ES si caratterizza, invece, come soluzione lowpower, con un rapporto tra corrente assorbita e prestazioni di soli 0.28 mA per MIPS, equivalente ad una riduzione della potenza dissipata (ad esempio, per i micro V850ES/Jx3-L) di fino anche al 65% rispetto a dispositivi concorrenti.

7 STADI DI PIPELINE ED ISTRUZIONI SIMD PER LE SERIE E2

La versione E2 rappresenta certamente la soluzione di punta della famiglia di CPU V850. Rispetto alle versioni base, la pipeline è struttura in questo caso in 7 stadi per consentire un incremento della frequenza di clock fino a 200 MHz ed il bus per il fetch delle istruzioni è esteso a 128 bit. Sono introdotte istruzioni per salti relativi a 32 bit ed a 3 operandi, come pure funzioni native di bit search. La CPU V850E2 supporta spazi d’indirizzamento distinti per programma e dati di dimensione fino a 4 GByte ognuno ed assicura una capacità di calcolo di 2.56 DMIPS/MHz, circa 1.4 volte superiore di quella di core analoghi. La versione V850E2H, il cui sviluppo è stato annunciato nell’ottobre 2010, prevede, inoltre, un’estensione per istruzioni SIMD per applicazioni di digital signal processing mediante pipeline dedicata e register file a 64 bit. Benchmark comparativi, basati su calcolo di FFT a 16 bit su 128 punti, mostrano che dimensioni dell’applicativo compilato e tempi di esecuzione si riducono rispettivamente ad un terzo ed un ventesimo dei valori che si avrebbero con le precedenti CPU. Oltre ai componenti tradizionali, su CPU V850E2 è basata la serie EP-1 di dispositivi PFESiP (Platform for Embedded System in a Package, vedi in figura 3), che integrano un sottosistema a microcontrollore con un gate array progettabile per realizzare funzioni definite dall’utente. La piattaforma riduce significativamente i rischi di sviluppo di soluzioni custom, essendo la sezione a microcontrollore già validata, ma garantisce nel contempo ampio flessibilità consentendo di estendere l’insieme nativo di periferiche con funzioni specifiche. La periferica utente è connessa al bus di sistema a 16 o 32 bit, sono disponibili versioni dei dispositivi PFESiP con fino a 240 K gate di logica utente.

DUAL CORE PER APPLICAZIONI HIGH-END

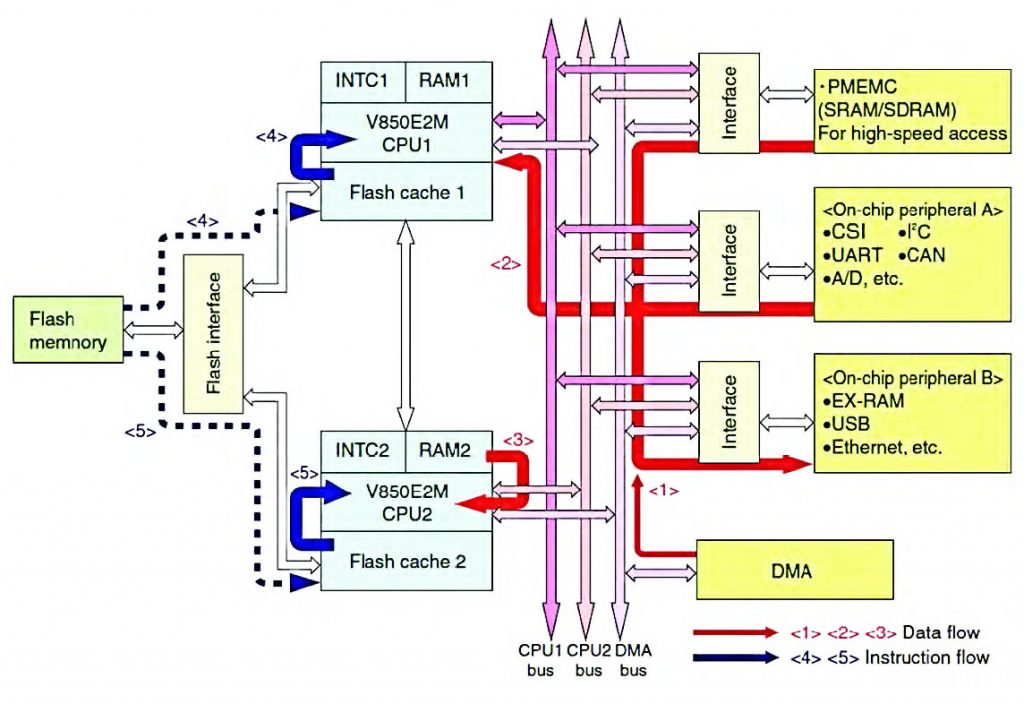

V850E2M è la versione dual-core della CPU E2, annunciata nel settembre 2010. Alla massima frequenza di clock di 200 MHz, la CPU raggiunge una capacità di calcolo complessiva di oltre 1 GIPS pur mantenendo un consumo di potenza di 0.88 mW/MIPS. Include (figura 4) tre bus interni per massimizzare le prestazioni consentendo l’esecuzione in parallelo di diverse funzionalità. Le serie EP-2 e EP-3 di dispositivi PFESiP in fase di sviluppo dovrebbero essere basati su tale CPU.

Figura 4: V850E2M: un dual-core a 1 GIPS.