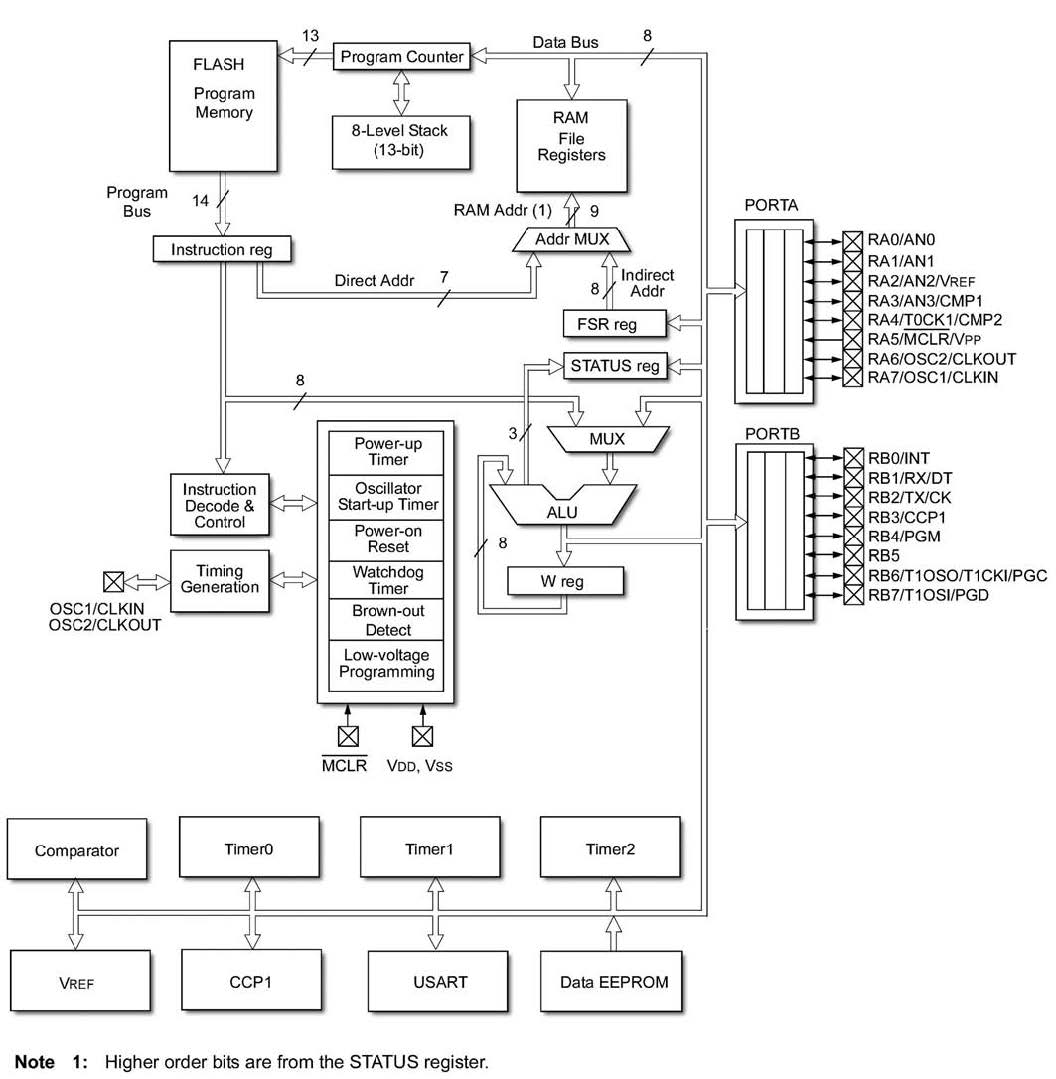

Nella maggior parte dei pic è implementata una periferica seriale, che viene identificata con il termine di “UNIVERSAL SYNCRONOUS ASYNCHRONOUS RECEIVER TRASMITTER (USART)”, nel presente articolo si fa riferimento a quella presente nel pic16f628.

La USART è uguale per tutta la famiglia pic16, quindi una routine scritta per un pic16 è utilizzabile su tutti i PIC della stessa famiglia a meno, del collegamento con il mondo esterno, ogni microcontrollore può avere mappato i pin su porte differenti, di conseguenza fanno verificati sul datasheet del microcontrollore dove sono ‘fisicamente collegati’. Da ricordare che la mappa dei registri in memoria potrebbe essere differente da modello a modello, e non tutti i registri SFR sono accessibili dallo stesso banco (si potrebbe scrivere in un registro che non è appropriato). La periferica seriale dei PIC può essere utilizzata in 3 modalità: il primo è il modo ASINCRONO, il secondo SINCRONO MASTER, il terzo SINCRONO SLAVE, in tutti i casi le linee a disposizione sono due, nel caso asincrono la periferica offre sui 2 pin di I/O, sia la linea di trasmissione (TX) che quella di ricezione (RX), quindi si può stabilire una comunicazione full duplex (o in italiano bidirezionale), cioè si può trasmettere e ricevere contemporaneamente, mentre nel caso sincrono la trasmissione avviene in half duplex (o mono direzionale), sempre su due pin, quindi o si trasmette o si riceve, questo perché non è disponibile un terzo pin per eseguire il collegamento con il registro interno che in ogni configurazione, nel Master il buffer di ricezione, nello Slave quello di trasmissione, viene escluso.

Figura 1: il registro RCSTA.

Figura 2: il registro TXSTA

Introduzione

Nel presente articolo tratteremo solo il modo asincrono; per poter utilizzare la periferica in questa modalità fanno configurati i relativi registri associati, che nonostante siano indicati come registri di trasmissione e ricezione, quindi come registri separati, fanno invece programmati considerandoli come un unico registro. Il formato dei dati deve essere di 8 bit, non sono ammessi formati differenti (esempio: 5,6,7 bit), l’unica eccezione è l’invio del bit 9 per gestire la parità, che va gestita tramite software. Per prima cosa va configurato SPBRG (base del tempo di clock), poi TXSTA (qui si attiva un ulteriore gestione del tempo di clock, oltre a gestire il flusso della trasmissione), e infine RCSTA (per attivare globalmente la periferica seriale, oltre alla gestione del flusso della ricezione).

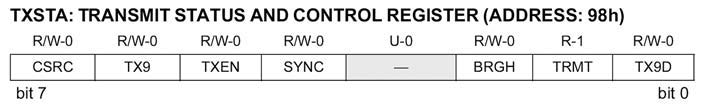

Figura 3: schema a blocchi della sezione di trasmissione della periferica USART.

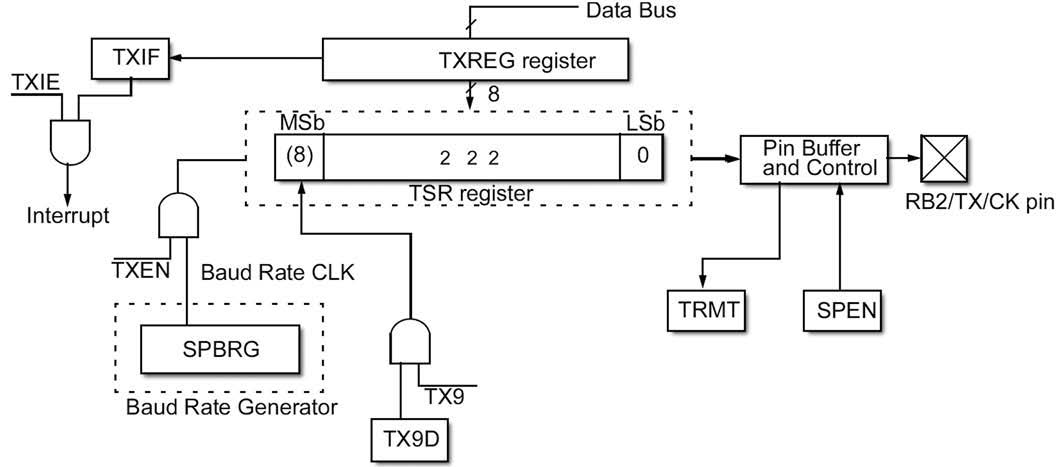

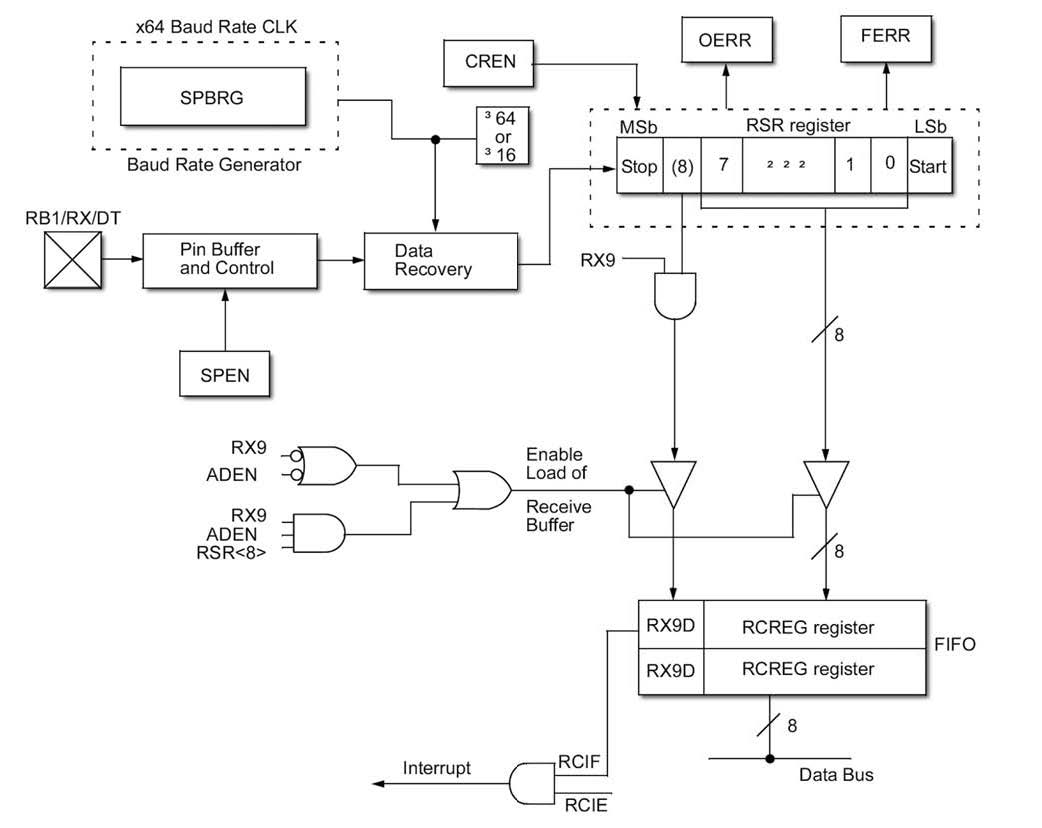

Figura 4: schema a blocchi della sezione di ricezione della periferica USART

Il Registro TXSTA e SPBRG

I registri TXSTA e SPBRG servono definire la base dei tempi, nel registro TXSTA si deve selezionare il bit BRGH per selezionare la modalita high o low (se è resettato, il fattore di divisione è di 64, mentre con il settaggio del bit il fattore di divisione è di 16), mentre nel registro SPBRG si inserisce il valore di divisione per ottenere la frequenza necessaria, la differenza dei gestione del bit BRGH consiste nel fattore di divisione. La formula per calcolare la frequenza di trasmissione è FOSC/(64(X+1)) nel caso di BRGH basso e FOSC/(16(X+1)) nel caso BRGH alto, dove in entrambi i casi X rappresenta il valore da inserire nel registro SPBRG. Per ricavare X conoscendo la frequenza di baudrate basta sostituire ad X+1, e il valore del baudrate necessario, in questo modo si ottiene: (ClkFreq/16/X)-1, va prestata attenzione ai limiti che il quarzo, ad esempio con una frequenza di 4 Mhrz, si possono avere dei tempi di clock che vanno da 4µSecondi (FOSC/(16(0+1))) a 1,024milliSecondi (FOSC/(16(255+1))), o 250KHz e 976,5625Hrz. A loro volta tali frequenze devono essere divise per 10 (1 il bit di start, 8 per i dati, e 1 bit per lo stop), ottenendo frequenze che vanno da 25Khrz a 97,6hrz, quindi possiamo affermare che il limite superiore è di 19.200hrz con BRGH posto a 1, ma se viene utilizzato il bit di parità, il fattore di divisione passerà a 11!, il datasheet del microcontrollore che utilizzate è una fonte di riferimento importante, a cui vi rimando. Il bit SYNC serve per selezionare la modalita di funzionamento asincrona o sincrona, il bit TRMT serve per verificare se il buffer è vuoto, in pratica serve per testare se il dato è stato inviato; va prestata la massima attenzione al suo utilizzo, infatti se non viene utilizzato nella fase di polling (ad es. Utilizzando al suo posto il bit di interruzione TXIF del registro PIR1), il microcontrollore non può più verificare se effettivamente il dato è stato trasmesso, in quanto tale bit non viene gestito senza l’uso delle interruzioni! Il bit TX9D può essere utilizzato se è necessario trasmettere il bit di parità; per far questo occorre abilitare il bit TX9, e avendo l’accortezza di caricare lo stato di tale bit, prima della trasmissione, perché caricando un dato nel registro di trasmissione, si attiva immediatamente l’invio del dato, senza poter poi caricare lo stato della parità.

Figura 5: lo schema a blocchi di un PIC della famiglia 16F62x.

Il Registro RCSTA e PIR1

Arrivati a questo punto va configurato il registro RCSTA: il bit SPEN abilita la periferica seriale, in pratica con questo bit si accende tutta la periferica, sia in trasmissione, che in ricezione, bisogna si attivare con i relativi bit (TXSTA<5> o TXEN e RCSTA<4> o CREN) l’avvio della\e sotto periferica\che (blocco TX o RC). Con il bit di CREN si abilita la gestione della ricezione, mentre, come già visto, il bit TX9D è utilizzato per ricevere il bit di parità, il bit di FERR serve per verificare la corretta ricezione del frame, questo è in pratica il valore del bit di stop, se questo valore è alto il frame (start-dato-stop) è stato correttamente ricevuto nel tempo stabilito dal baurate, altrimenti c’è stato un errore dovuto all’errata velocità di trasmissione. L’ultimo bit utilizzato nella modalità asincrona è il bit OERR, utilissimo con la gestione in polling. Il buffer di lettura è formato da 2 registri: il primo è temporaneo e serve per eseguire la ricezione nei tempi prestabiliti, mentre il secondo serve per salvare il dato letto mentre è in corso una possibile ricezione del dato successivo; se non viene letto il dato presente nel buffer, nel tempo a disposizione, viene attivato il flag di OERR per indicare che tale dato è andato perso! La fine della ricezione a differenza della trasmissione viene verificata tramite il flag di RCIF del registro PIR1, quindi per poter utilizzare la periferica seriale asincrona (o USART) del microcontrollore si deve utilizzare TXSTA, RCSTA, e PIR1, oltre ai registri-buffer di trasmissione e ricezione.

La teoria è sempre monotona...

Adesso che sono note le nozioni di base, simuliamo un po’ con l’mplab, iniziamo con creare il progetto tramite il project wizard, nella procedura guidata, dovete selezionare il micro PIC16f628, il file .asm da includere lo trovate sul sito della rivista, ed infine vanno inclusi il file P16F628.inc per le definizioni e il file 16F628.lkr per il linker, onde evitare errori di compilazione per la mancanza dei file. L’MPLAB permette di simulare una porta seriale, vediamo come. Prima di tutto va selezionato il simulatore MPLAB SIM, poi si seleziona MPLAB->Debbuger->Setting, si apre una finestra che permette di impostare vari parametri, di cui si deve selezionare Osc\Trace per impostare la frequenza di clock del micro a 4Mhrz, poi si cambia pagina selezionando il tag Uart1 I\O, qui si seleziona Enable Uart1 I\O per attivarla. Ora si deve selezionare un file da trasmettere al micro, si seleziona Rewind Input, e l’Output lo si seleziona come W indow, per visualizzarla nella finestra di debug (può essere salvato in un file, ma la funzione non permette di visionare la ricezione nella finestra di degub). Il file di esempio si limita a ricevere e ritrasmettere una serie di dati che possono essere modificati a piacimento. Durante il processo di boot il micro inizializza le porte e la periferica seriale, vanno osservate le relative righe di codice nel blocco di boot, questo codice serve per poter verificare che il valore numerico inserito in X sia valido ed ottenere così un valore adatto per SPBRG. Si può provare a modificare il valore di X nelle definizioni, inserendo 115.200, si noterà così che il processo di compilazione si ferma segnalando errore, per ogni dubbio si può andare a curiosare tra il topics dell’MPLAB Assembler, la valutazione durante la compilazione viene fatta anche per il limite di MaxChar in CreaBuffer. Finalmente si può compilare il progetto, e passare alla simulazione: attivate i break point dove più vi aggrada, e vedrete che arriveranno in sequenza tutti i caratteri che avete nel file *.txt che avete creato, poi dopo la trasmissione non avendo nessun ritardo il file *.txt, viene continuamente trasmesso, e quando il programma torna al main, passerà per la correzione dell’errore, ripristinando la comunicazione! A questo punto abbiamo creato una piattaforma per poter fare tutte le simulazioni possibili.

Il file TXT

■■■ Il file da trasmettere dalla porta seriale simulata, per essere utilizzato dal simulatore, va salvato in formato .txt, e ogni carattere o stringa ASCII va racchiuso tra le virgolette (“”); il topics relativo al SIM vi può essere utile per poter ampliare le possibilità offerte dal simulatore, tipo l’inserimento di ritardi tramite la wait xx yy, dove xx è un valore numerico, mentre yy è la scala di misura del tempo (ad esempio: wait 20 ms, significa che deve aspettare 20 millisecondi).

Parole strane...

■■■ Alcune “parole” che possono sembrare un pò strane, sono le definizioni per il linker, tipo “STARTUP code”, STARTUP indica al linker le prime locazioni della flash, mentre code indica l’inserimento di righe di codice eseguibile, per gli ulteriori dettagli si rimanda al file relativo al linker per il micro scelto. Da consultate il topic dell’mplab relativo a MPASM per trovare la spiegazione sui riferimenti mancanti, ad esempio: “gprnobnk udata_shr” col quale si riservano delle locazioni ram nella zona share (condivisa).