Abbiamo incontrato a Milano Jeff Lewis, Senior VP Marketing & Business Development di SuVolta, dove ci ha presentato, in concomitanza con l’IEDM 2011, la tecnologia Deeply Depleted Channel, una nuova tecnologia avanzata per la riduzione dei consumi energetici e la scalabilità CMOS.

All’IEDM 2011 (International Electron Devices Meeting), SuVolta ha reso noti alcuni dettagli sui transistor a basso consumo Deeply Depleted Channel (DDC). La tecnologia DDC di SuVolta, parte della piattaforma CMOS a basso consumo PowerShrink, fornisce dispositivi a basso consumo in grado di ridurre del 50% i consumi energetici, senza tuttavia pregiudicare la velocità operativa. In combinazione con tecniche avanzate di riduzione della tensione, tale percentuale può arrivare fino all’80% e oltre.

TECNOLOGIA DEEPLY DEPLETED CHANNEL (DDC)

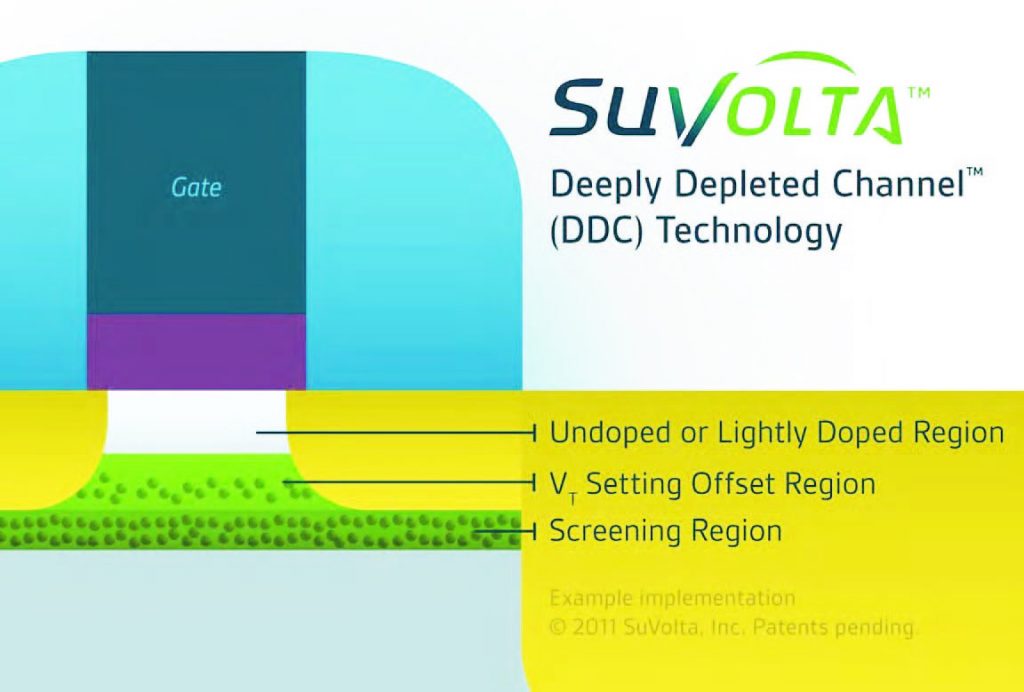

I transistor DDC di SuVolta riducono la variabilità della tensione di soglia (VT) e consentono una scalabilità CMOS continua. La struttura funziona formando un canale DDC nel momento in cui viene applicata tensione al gate. In un’implementazione tipica, il canale DDC è caratterizzato da più regioni: una regione non drogata o leggermente drogata, una regione offset di impostazione della VT e una regione di schermatura. Le implementazioni dei transistor DDC di SuVolta possono variare a seconda della fabbricazione del wafer e dei requisiti specifici di progettazione del chip. La regione non drogata o leggermente drogata (Figura 1) rimuove i droganti dal canale, consentendone lo svuotamento completo. Ciò riduce la fluttuazione casuale dei droganti (RDF), consentendo la scalabilità della VDD e una maggiore mobilità per l’aumento della corrente efficace. La regione offset di impostazione della VT regola i livelli della tensione di soglia del transistor senza pregiudicare la mobilità del canale e offre una migliore VT sigma rispetto ai tradizionali transistor.

La regione di schermatura scherma il carico e imposta la profondità del livello di svuotamento. Inoltre, funge da corpo per la regolazione dinamica della VT tramite polarizzazione. I transistor DDC funzionano a basso consumo grazie alla riduzione della tensione di alimentazione. Controllando la variazione VT, i chip dotati di tecnologia DDC di SuVolta offrono una serie di vantaggi, tra cui: riduzione del 30% della tensione operativa senza impatto sulle prestazioni, significativa riduzione delle dispersioni, meno guard banding nella progettazione, maggiore rendimento. I transistor DDC, inoltre, consentono di impostare più VT, una funzionalità essenziale per gli attuali prodotti a basso consumo. Oltre ai vantaggi associati alla riduzione della variazione VT, i transistor DDC offrono anche altri benefici per ridurre ulteriormente i consumi e aumentare al contempo la velocità, inclusi: aumento della mobilità del canale per una maggiore corrente di pilotaggio, riduzione del carico DIBL (Drain Induced Barrier Loading).

Figura 1: la tecnologia DDC di SuVolta

FUNZIONAMENTO DELLA SRAM A TENSIONI ULTRA BASSE

Fujitsu Semiconductor Limited e SuVolta, Inc. hanno inoltre dimostrato con successo il funzionamento a tensione ultra bassa dei blocchi SRAM (Static Random Access Memory) a una tensione di 0,425 V tramite integrazione della piattaforma CMOS a basso consumo PowerShrink di SuVolta nella tecnologia di processo a basso consumo di Fujitsu Semiconductor. Riducendo il consumo energetico, queste tecnologie consentiranno in un futuro vicino di sviluppare prodotti “ecologici” all’avanguardia. Specifiche tecniche e performance sono state presentate sempre in occasione dell’International Electron Devices Meeting (IEDM) 2011 che si è aperto a Washington DC il 5 dicembre. Il controllo dei consumi energetici è uno dei principali aspetti che limita l’aggiunta di funzionalità in prodotti quali i dispositivi elettronici mobili, i server e le apparecchiature di rete.

Il fattore che contribuisce maggiormente al consumo energetico è la tensione di alimentazione. In passato la tensione di alimentazione dei CMOS si è costantemente ridotta a circa 1,0 V sul nodo tecnologico da 130 nm. Tuttavia, non si è ottenuta un’ulteriore riduzione con il passaggio al nodo da 28 nm. Una delle principali problematiche legate alla riduzione della tensione di alimentazione è rappresentata dalla tensione operativa minima dei blocchi SRAM embedded. Combinando il transistor DDC e la sofisticata tecnologia di processo di Fujitsu Semiconductor, le due aziende hanno dimostrato che una SRAM da 576 K può funzionare senza problemi a una tensione di circa 0,4 V dimezzando la variazione della tensione di soglia (VT) del transistor CMOS. Questa tecnologia è compatibile con le infrastrutture esistenti, inclusi i layout SoC, gli schemi di progettazione (ad esempio, il controllo di polarizzazione del corpo) e gli strumenti di produzione esistenti.

PRIMA FASE

Secondo la legge di scalabilità, la tensione di alimentazione dei CMOS si riduce progressivamente fino a circa 1,0 V sul nodo tecnologico da 130 nm. Tuttavia, le tensioni di alimentazione sono rimaste ferme a circa 1,0 V nonostante le tecnologie di processo abbiano continuato a scalare da 130 nm a 28 nm. Poiché la potenza dinamica è proporzionale al quadrato della tensione di alimentazione, il consumo energetico è diventato una priorità per la tecnologia CMOS. La scalabilità della tensione di alimentazione si è fermata al nodo da 130 nm per via delle numerose fonti di variazione, inclusa la fluttuazione causale dei droganti (RDF). La fluttuazione RDF è una forma di variazione a livello di dispositivo e processo determinata dalle concentrazioni fluttuanti dei droganti impiantati o degli atomi di impurità nel canale del transistor. Tale fluttuazione determina una variazione della tensione di soglia (VT) tra transistor diversi su un chip. Una successiva riduzione della RDF è stata registrata utilizzando due strutture esotiche, ETSOI e Tri-Gate, una tecnologia FinFET. Entrambe le tecnologie, ETSOI e FinFET, sono tuttavia molto complesse e quindi difficilmente compatibili con le infrastrutture di progettazione e produzione esistenti.

IL TRANSISTOR DDC DI SUVOLTA

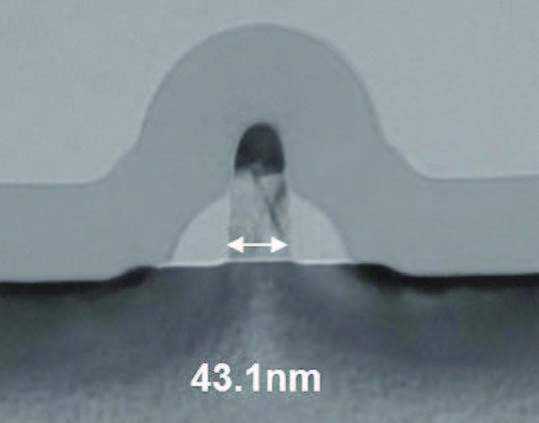

La Figura 2 illustra l’implementazione dei transistor DDC di SuVolta sulla tecnologia di processo CMOS a basso consumo di Fujitsu Semiconductor. La micrografia TEM (Transmission Electron Micrograph) intersezionale mostra un transistor fabbricato su una struttura in silicio piana.

Figura 2: sezione trasversale del transistor DDC

RIDUZIONE DELLA TENSIONE OPERATIVA MINIMA PER LA SRAM

Nella maggior parte dei chip la riduzione della tensione di alimentazione è limitata dalla SRAM. Fujitsu Semiconductor e SuVolta hanno dimostrato che una macro SRAM è in grado di funzionare anche a tensioni di 0,425 V. Dal momento che la SRAM è il circuito che pone i maggiori problemi nella riduzione della tensione di alimentazione, è stato dimostrato che un transistor DDC può funzionare a una tensione di 0,4 V su una serie di circuiti basati su CMOS.