Le caratteristiche principali del protocollo AMBA AHB-Lite introdotto da ARM. Con la descrizione dello standard, vengono presentati modelli VHDL sintetizzabili dei diversi elementi che compongono il sistema.

Il protocollo AMBA AHB-Lite è stato emesso nel 2006 da ARM - nota azienda leader nel mercato dei processori e core IP - in sostituzione dello standard AHB; la nuova specifica introduce importanti semplificazioni pur conservando le principali caratteristiche in termini di prestazioni e flessibilità della versione precedente.

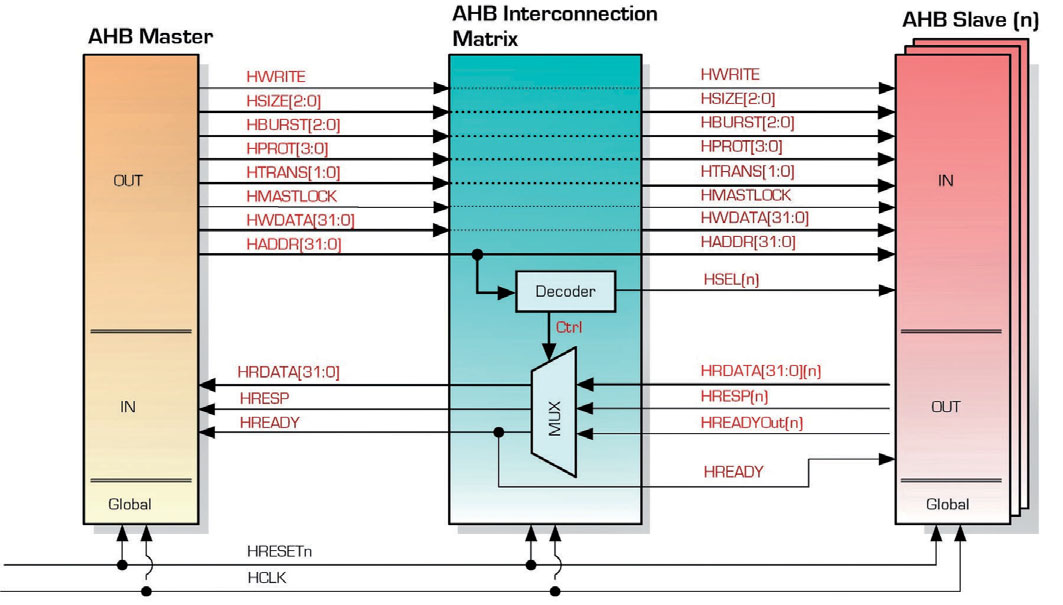

La figura 1 mostra uno schema di principio di un sistema AMBA AHB-Lite, composto dai seguenti elementi fondamentali:

➤ master: è la periferica responsabile dell’inizio di ogni transazione in lettura o scrittura. Nella versione attuale il protocollo è definito per sole applicazioni singlemaster; tuttavia, come discusso in dettaglio in seguito, è possibile modificare la matrice di interconnessione per introdurre supporto per sistemi multi-master;

➤ slave: è la periferica oggetto della transazione;

➤ matrice di connessione: include la logica di decodifica dell’indirizzo negli accessi alle periferiche slave ed il multiplexing delle linee dati, di risposta e di controllo di queste. Il significato dei diversi segnali del bus mostrati in figura sarà chiarito nel prosieguo.

Figura 1: un sistema basato su bus AMBA AHB-Lite (caso single master-multiple slave).

Accessi singoli

Il bus AHB-Lite è di tipo parallelo; la larghezza di parola è tipicamente 32 bit, ma sono possibili anche configurazioni a 64, 128, 256, 512 e 1024 bit. Lo spazio di indirizzamento è 1 Gbyte. Il protocollo di comunicazione è di tipo sincrono, con i dispositivi master e slave che operano tutti sullo stesso fronte attivo del segnale di clock. Sono previsti accessi singoli in lettura/scrittura ed operazioni a burst con meccanismo di lock del bus ove richiesto. Ogni transazione consiste, in generale, di:

➤ una fase di indirizzamento (address phase), durante la quale il master indica l’indirizzo oggetto della transazione ed il tipo di questa;

➤ una fase dati (data phase) durante la quale vengono scambiate le informazioni tra il master ed il dispositivo slave indirizzato.

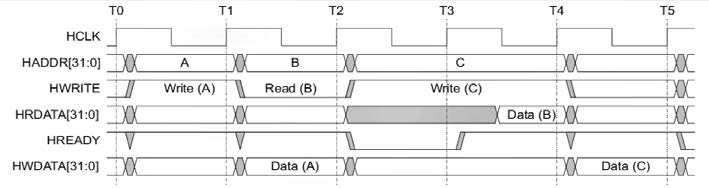

Tale natura pipelined del ciclo di bus consente di raggiungere più elevate frequenze di funzionamento in applicazioni ad elevate prestazioni. La fase dati, inoltre, ha una durata variabile; il termine della transazione è infatti direttamente controllato dal dispositivo slave indirizzato che può introdurvi un numero variabile di wait-state. In questo modo, ogni periferica può adattare la velocità di trasferimento sul bus al proprio tempo di accesso; si evita così che le prestazioni del sistema siano vincolate dal dispositivo più lento. La figura 2 mostra una sequenza di singole operazioni di scrittura/lettura in cui si evidenziano tutti questi aspetti. Il primo trasferimento è una operazione di scrittura all’indirizzo 0hA.

Figura 2: transazioni in lettura/scrittura su bus AMBA AHB-Lite (da AMBA 3 AHB-Lite Protocol Specification

Durante la fase di indirizzamento, corrispondente al periodo T0, il master pilota l’indirizzo destinazione HADDR e segnala che si tratta di un accesso in lettura attivando nel livello logico ‘1’ la linea HWRITE; nel successivo periodo T1 pone sul bus dati HWDATA il valore da scrivere nella locazioni indirizzata. Nello stesso periodo indica inoltre indirizzo e tipo della successiva operazione; si tratta di un accesso in lettura (HWRITE è posto a ‘0’) all’indirizzo 0hB. Tuttavia in questo caso, la periferica slave indirizzata non è in grado di terminare immediatamente la transazione; nel periodo T2, pertanto, mantiene il segnale HREADY nel livello ‘0’ per estendere il trasferimento. L’accesso sarà completato nel periodo T3, quando il dispositivo pilota sul bus HRDATA il contenuto della locazione richiesta e rilascia la linea HREADY. L’introduzione di wait-state ha come effetto quello di estendere la fase di indirizzamento del successivo trasferimento, come si può facilmente vedere dalla figura 2 in riferimento al terzo accesso; la fase inizia nel periodo T2 ma si conclude solo nel periodo T3. Per questo, come espressamente mostrato in figura 1, il segnale HREADY generato mediante multiplexer dalla matrice di interconnessione deve essere riportato in ingresso anche ai dispositivi slave per indicare a questi per l’appunto il termine della fase di indirizzamento.

Dimensione e tipo dei trasferimenti

Oltre alle linee HWRITE e HREADY, il protocollo AMBA prevede altri segnali di controllo che servono, tra le varie cose, a specificare la dimensione del trasferimento (HSIZE) ed il suo tipo (HTRANS ed HPROT). I trasferimenti, ad esempio, possono essere a byte, half-word, word, double-word in sistemi a 32 bit o, nelle architetture con larghezza di parola maggiore, a 128, 256, 512 o 1024 bit. L’indirizzo deve essere sempre allineato alla dimensione del trasferimento, ovvero deve essere, ad esempio, HADDR[1:0]=0b00 nel caso di trasferimenti a double-word o HADDR[0]=0 nel caso di accessi a word. I diversi tipi di transazione, invece, opportunamente segnalati dalla linea HTRANS, sono:

➤ IDLE: indica che il master non intende eseguire alcun trasferimento dati; in questo caso, il dispositivo slave selezionato in base all’indirizzo deve rispondere con zero wait state e non eseguire alcuna operazione.

➤ BUSY: nei trasferimenti a burst, indica che il master non è pronto a iniziare il successivo trasferimento dati. In questo caso, lo standard prevede che il master continui a pilotare il bus con le linee di indirizzo e di controllo della precedente transazione; la periferica slave dovrà quindi terminare tale trasferimento con zero wait-state ed ignorarlo

➤ NONSEQ: segnala un trasferimento singolo od il primo di un burst.

➤ SEQ: segnala un trasferimento successivo al primo in una transazione a burst. E’ inoltre previsto un meccanismo di controllo e protezione di accesso, sebbene il supporto di questo da parte delle periferiche master e slave non sia indicato come mandatario dallo standard. Mediante le linee di controllo HPROT, ad esempio, i trasferimenti possono essere segnalati come operazioni di fetch delle istruzioni in memoria, accessi ad aree di memoria dati, di tipo utente o privilegiato… In considerazione dei diversi tipi, i dispositivi slave indirizzati possono eseguire i controlli del caso. Una delle applicazioni più tipiche si ha ad esempio nei sistemi con MMU (Memory Management Unit) e che dispongano di cache istruzioni e dati.

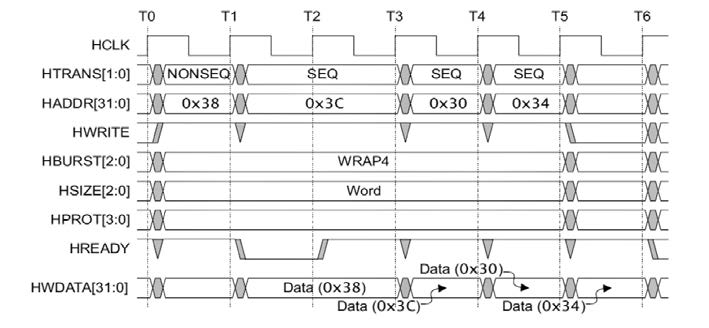

Trasferimenti locked e trasferimenti a burst

Come già anticipato, oltre ai trasferimenti singoli, il protocollo AMBA AHB prevede trasferimenti a burst di lunghezza fissata (pari a 4, 8 o 16 accessi) o indefinita, secondo quanto specificato dalle linee di controllo HBURST. Nei burst di lunghezza indefinita, l’indirizzo viene incrementato ad ogni accesso in funzione della dimensione del trasferimento. Tuttavia non è consentito che il burst si estenda oltre la finestra di indirizzamento di 1 Kbyte; nel caso, ad esempio, in cui abbia avuto inizio all’indirizzo 0hF00 ed utilizzi trasferimenti a double-word, l’ultimo indirizzo consentito è 0xFFC. Qualora il master intenda terminare prima il trasferimento, è previsto che istruisca sul bus un accesso di tipo IDLE. Nel caso invece di trasferimenti di lunghezza fissata, si distingue tra incrementing burst e wrapping burst. Nel primo caso si accede a locazioni contigue incrementando progressivamente l’indirizzo tra un accesso ed il successivo; nel secondo, invece, viene eseguito il wrap dell’indirizzo al termine di una finestra di indirizzamento che dipende dal numero di accessi di cui consiste il burst e dalla dimensione del trasferimento. Ad esempio, come mostrato in figura 3, nel caso di burst di 4 accessi a word, ogni singola finestra consiste di 16 byte e se l’indirizzo iniziale del trasferimento è 0h34, i successivi accessi dovranno essere effettuati agli indirizzi 0h38, 0h3C e 0h30.

Figura 3: esempio di trasferimento a burst (da AMBA 3 AHB-Lite Protocol Specification ).

Nei sistemi multimaster, per evitare che il bus sia riarbitrato mentre un burst è in corso, è possibile congelarne il possesso mediante il segnale HLOCK. Più in generale, lo standard impone che una qualsiasi sequenza di accessi, anche di tipo singolo, iniziati mentre tale segnale è attivo, debba essere considerata come indivisibile; i dispositivi indirizzati devono rispondere a tutti gli accessi prima di poter eseguire qualunque altra operazione. Una delle tipiche applicazioni riguarda, ad esempio, l’esecuzioni delle operazioni di swap in memoria su un dispositivo slave; il sistema deve assicurare che la periferica non esegua operazioni sulle locazioni oggetto dello swap prima che l’istruzione sia terminata.

Trasferimenti con errore

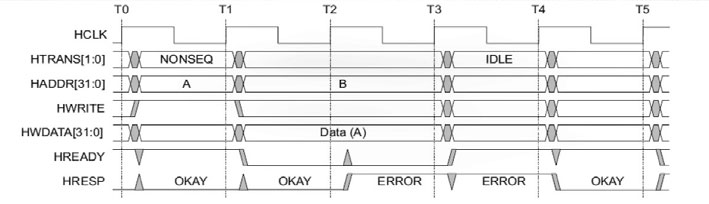

Oltre a controllare direttamente la durata dei singoli accessi, i dispositivi slave possono indicarne mediante la linea HRESP il buon esito. I motivi di errore possono essere diversi; uno dei casi più frequenti è, ad esempio, l’accesso in scrittura ad una locazione di tipo a sola lettura. La figura 4 mostra l’andamento dei segnali di controllo del bus in presenza di un trasferimento con singolo wait-state (trasferimento A) terminato con errore, come indicato dalla linea HRESP.

Figura 4: trasferimento con errore (da AMBA 3 AHB-Lite Protocol Specification ).

A causa della natura pipelined del bus, la procedura per la segnalazione di errore richiede almeno due cicli di clock. Il trasferimento A, come si può vedere dalla figura, ad esempio, ha inizio nel periodo T0, per la durata del quale si estende la sua fase di indirizzamento; il periodo T1 è invece un normale ciclo di wait-state introdotto dalla periferica indirizzata. Nel periodo T2, quindi, viene riconosciuto e segnalato l’errore; tuttavia, il trasferimento non può terminare immediatamente poiché questo significherebbe chiudere anche la fase di indirizzamento della transazione B che potrebbe non essere lecito eseguire a seguito dell’errore. Per cancellare la transazione, occorre un ulteriore periodo; durante tale periodo (T3), il master istruisce un trasferimento IDLE mentre alla periferica slave è permesso di chiudere il precedente accesso fallito. Non vi sono vincoli ulteriori; a questo punto il master, a seconda della particolare applicazione, potrà riprovare l’accesso alla locazione A, istruire nuovamente la transazione B od iniziare un nuovo trasferimento ad un diverso indirizzo.

Conclusioni

In questa prima parte del tutorial abbiamo introdotto le caratteristiche generali del protocollo AMBA AHB-Lite. Si tratta, come visto, di un bus per applicazioni System-On-Chip caratterizzato da elevate prestazioni (grazie ad un protocollo di indirizzamento pipelined ed al supporto per trasferimenti a burst) e relativa semplicità. Nella prossima puntata vedremo in maggior dettaglio le caratteristiche dei moduli master e slave unitamente ad un modello HDL sintetizzabile in logiche programmabili.