L’architettura ARM (precedentemente Advanced RISC Machine, prima ancora Acorn RISC Machine) indica una famiglia di microprocessori RISC a 32bit sviluppata da ARM Holdings e utilizzata in una moltitudine di sistemi embedded.

Grazie alle sue caratteristiche di basso consumo (rapportato alle prestazioni) l’architettura ARM domina il settore dei dispositivi mobili dove il risparmio energetico delle batterie è fondamentale. Attualmente la famiglia ARM copre il 75% del mercato mondiale dei processori a 32 bit per applicazioni embedded, ed è una delle più diffuse architetture a 32 bit del mondo. I processori ARM vengono utilizzati in PDA, cellulari, lettori multimediali, videogiochi portatili e periferiche per computer (come router, hard disk di rete ecc...). Importanti rami della famiglia ARM sono i processori XScale e i processori OMAP prodotti da Texas Instruments. LPC1758 (figura 1) usa una architettura Harvard con istruzioni locali separati; frequenza di lavoro superiore a 100 Mhz.

Figura 1: LPC1758.

Possiamo riassumere le caratterristiche nei punti seguenti:

- Processore ARM Cortex-M3 con frequenza superiore a 100Mhz

- 512 kB di memoria Flash # Bootloader software

- SRAM

- 8 canali per DMA controller

- 2 SSP controllers per FIFO

- Bus CAN

- ADC 12 bit

Applicazioni di questo microprocessori si possono trovare nel campo del network, controlli motori e sistemi di allarmi.

LPC1758

L’architettura Harvard è un particolare tipo di architettura in grado di separare la memorizzazione e le trasmissioni dei dati da quella delle istruzioni. In un’architettura Harvard le memorie per i dati e per le istruzioni possono essere anche diverse, in particolare in alcuni sistemi la larghezza di parola delle istruzioni è superiore a quella dei dati e in altri sistemi i programmi sono memorizzati in una memoria a sola lettura (ROM) mentre i dati sono normalmente in una memoria a scrittura e lettura (RAM). In un’ Architettura classica di von Neumann la CPU legge le istruzioni e i dati dalla memoria utilizzando lo stesso bus, quindi quando la CPU carica un’istruzione non può contemporaneamente caricare anche un dato. In un’architettura di Harvard il processore è in grado di accedere in modo indipendente a dati e istruzioni dato che questi sono separati e memorizzati in memorie separate. Un’architettura Harvard quindi può eseguire più compiti in parallelo dato che può parallelizzare le operazioni di lettura e scrittura della memoria. L’aumento di velocità viene compensato dalla presenza di circuiti più complessi all’interno del processore. L’ARM Cortex è una famiglia di microprocessori presentata nel 2005 dalla ARM Holdings e basati sul set di istruzioni ARMv7. La famiglia Cortex è formata da una serie di blocchi funzionali che possono essere collegati tra loro al fine di soddisfare le esigenze dei clienti, quindi un specifico processore Cortex non ha necessariamente tutte le unità funzionali della famiglia. I processori Cortex sono disponibili in configurazione singolo core o multicore e per ogni famiglia esistono più core con prestazioni diversi. Rispetto alla versione 6 la famiglia Cortex introduce le seguenti novità:

- L’unità NEON sviluppata per eseguire operazioni SIMD su vettori di 64 o 128 bit. L’unità è dotata di registri dedicati ed i vettori possono contenere numeri interi a 16 o 32 bit o numeri in virgola mobile a singola precisione a 32 bit. L’unità opera in parallelo alla pipeline principale, la pipeline principale interviene solo durante il caricamento delle istruzioni da eseguire.

- L’unità in virgola mobile VFPv3 raddoppia i registri della precedente versione portandoli a 32 e introduce alcune nuove operazioni.

- Il set di istruzioni Thumb-EE è un derivato del set di istruzioni Thumb-2 ed è nato per sostituire le istruzioni Jazelle. Queste istruzioni vengono utilizzate per accelerare l’esecuzione di codice eseguito da macchine virtuali come quello richiesto dal linguaggio Java.

- TrustZone è una modalità di esecuzione sicura nata per permettere l’esecuzione di codice sicuro o per eseguire meccanismi di digital rights management (DRM).

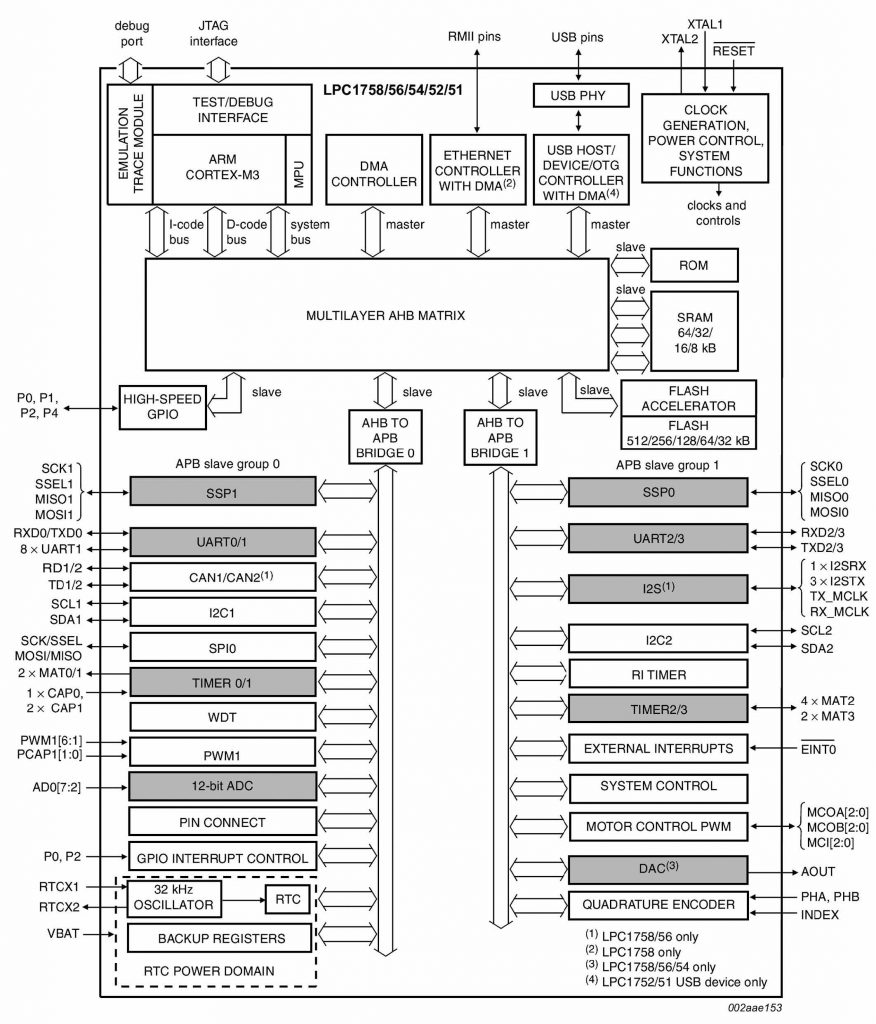

La famiglia Cortex è suddivisa nella serie A (Application), la serie R (Realtime) e la serie M (Microcontroller). La serie A è la serie indirizzata ai computer, telefoni cellulari evoluti e più in generale le applicazioni che necessitano di potenza di calcolo e flessibilità. Questa è la serie più completa e oltre al set di istruzioni classico ARM gestisce le istruzioni Thumb-2, Thumb-EE, include le unità Vector Floating Point (unità di calcolo in virgola mobile) e NEON (unita SIMD). Il processore è dotato di cache di primo e secondo livello, PMMU e tecnologia TrustZone. La serie R è sviluppata per applicazioni realtime, il set di istruzioni Thumb-2 è presente, le istruzioni Vector Floating Point sono opzionali e la cache è configurabile. La protezione della memoria è presente opzionalmente tramite la MPU, un’unità più limitata della PMMU. La serie M è la serie più ridotta, implementa solamente il set di istruzioni Thumb-2, la cache non è presente e la MPU è opzionale. Il modello M3 è particolarmente utilizzato nel campo automotive dove sono richieste elevati criteri di affidabilità. La famiglia Cortex A è stata sviluppata al fine di ottenere prestazioni elevate e consumi ridotti. I processori di questa serie si suddividono in tre core, il core 5, 8 e 9. Il core 5 ha una pipeline a 8 stadi, il core 8 ha due pipeline a 13 stadi e il core 9 ha due pipeline a 8 stadi. Le pipeline dei primi ARM erano a 3 stadi e in seguito sono state sviluppate unità fino a 9 stadi. Lo sviluppo di un processore a 13 stadi si è reso necessario per innalzare la frequenza di funzionamento del processore. Al fine di evitare che i salti condizionati deprimessero eccessivamente le prestazioni per via della pipeline lunga tutti i core implementa un’unità di predizione delle diramazioni che secondo le dichiarazioni del costruttore predice correttamente il 95% dei salti. Il processore al fine di non richiedere un numero eccessivo di transistor non implementa nel core 8 l’esecuzione fuori ordine delle istruzioni, mentre il core 9 introduce anche questa caratteristica, il core 3 avendo una sola pipeline non più eseguire più di un’istruzione per ciclo di clock. Nel core 8 la prima istruzione viene caricata dalla prima pipeline, la seconda istruzione viene caricata dalla seconda pipeline; nel caso di vincoli l’istruzione vincolata viene bloccata fino a quando l’altra istruzione non è completata e quindi il vincolo è risolto. Le pipeline sono indipendenti ed equivalenti, tranne per l’operazione di moltiplicazione che può essere eseguita solo dalla prima pipeline. Questo normalmente non è un grave vincolo dato che le operazioni di moltiplicazioni sono normalmente rare. Il core 9 gestendo l’esecuzione fuori ordine analizza il codice e ricerca due istruzioni non vincolate per eseguirle in parallelo, fornendo prestazioni migliori del core 8. Il core 9 gestisce anche la ridenominazione dei registri al fine di ridurre i vincoli e migliorare l’esecuzione parallela delle istruzioni. I core 5 e 9 possono essere assemblati in integrati che possono contenere fino a 4 core. LPC1758 include 3 tipi di bus AHB-lite: il bus di sistema, il bus I-code e il bus Dcode. Gli ultimi due sono bus più veloci rispetto al bus di sistema e sono simili al TCM: un bus dedicato alle istruzioni fetch (I-code) e un altro per trasmissione dati (D-code). L’uso dei due bus permette l’esecuzione di operazioni in contemporanea. In figura 2 possiamo osservare la mappa di memoria del LPC1758.

Figura 2: Memory map.

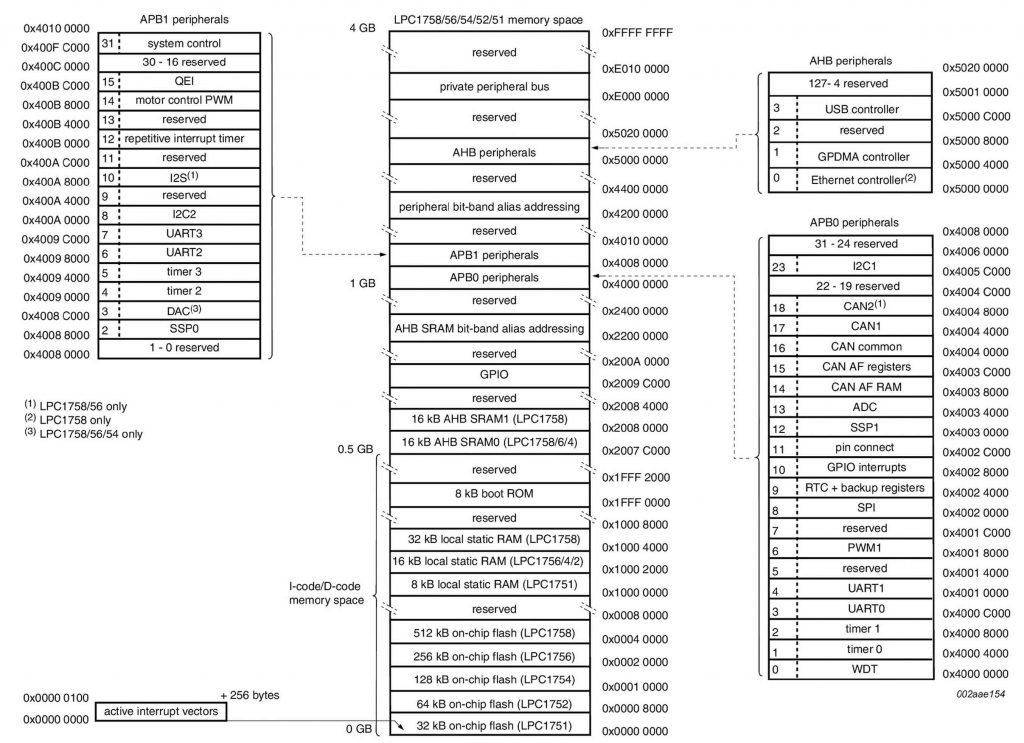

LPC1758 – CLOCKING

Il LPC1758 (figura 3) include 3 oscillatori indipendenti. Il principale, oscillatore ITC e gli altri RTC. Ognuno di questi oscillatori possono essere comandati via software. L’oscillatore principale può anche essere usato come clock per la CPU senza l’uso del PLL. La frequenza di lavoro può essere settata tra 1 Mhz fino a 25 Mhz.

Figura 3: Clocking generation.

LPC1758 – POWER CONTROL

LPC1758 supporta una varietà di power control: sleep mode, deep-sleep mode, power-down mode and deep power-down mode. In particolare nello sleep mode il clock è fermo mentre nel deep power-down mode è consentito solo l’uso del blocco RTC.