“One Chip is All You Need”, questa è l’espressione che Actel (ora Microsemi) usa per descrivere la sua FPGA Fusion. Questo chip integra all’interno non solo blocchi digitali, tipici di una FPGA, ma anche un flessibile set di periferiche analogiche. Nell’articolo si presentano le caratteristiche distintive e le tecniche di programmazione di Actel Fusion.

Fusion PSC (Programmable System Chip) è la prima FPGA di Actel (ora Microsemi) di tipo mixed-signal, che integra periferiche analogiche configurabili (tra cui ADC), blocchi di memoria Flash di elevata capacità, efficienti modalità di generazione del master clock ed una logica programmabile dalla elevate prestazioni: tutto questo in un singolo circuito integrato (Figura 1).

L’innovativa architettura proposta da Actel (ora Microsemi) per questa FPGA può essere interfacciata con i core ARM7 (CoreMP7) e 8051 (Core8051). Essa rappresenta una piattaforma di programmazione completa e potente. Esistono quattro modelli di Fusion previsti da Actel (ora Microsemi):

- AFS090

- AFS250

- AFS600

- AFS1500

Le caratteristiche di ognuno di essi sono riportate nella Tabella 1.

Tabella 1. Fusion è la prima FPGA di Actel di tipo mixed-signal. Esistono quattro differenti modelli, con caratteristiche tecniche ed architetturali differenti

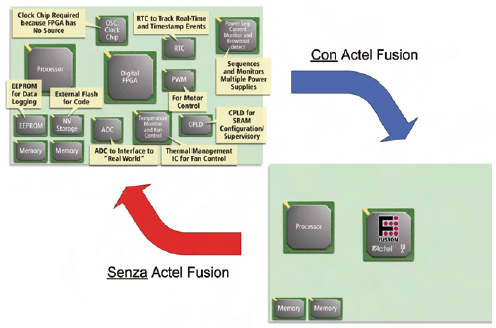

La possibilità di disporre di periferiche analogiche, oltre che dei blocchi digitali, offre al progettista la possibilità di ridurre notevolmente il numero di componenti esterni aggiuntivi (vedere Figura 2).

Figura 2. La flessibilità dei blocchi analogici e digitali della FPGA Fusion, riduce enormemente il numero di componenti esterni da utilizzare

PROGRAMMARE ACTEL FUSION

Ambiente di sviluppo e starter kit

Per supportare questa nuova tecnologia, Actel (ora Microsemi) ha sviluppato una serie di tool che massimizzano la produttività, riducendo al minimo lo sforzo del progettista. Tali strumenti sono integrati nell’ambiente di sviluppo tipico dei prodotti Actel (ora Microsemi): Libero IDE. Questo nuovo strumento consente al progettista di istanziare e configurare facilmente periferiche, stabilire dei collegamenti tra esse, creare od importare blocchi pre-costituiti (detti Fusion applet) o progetti di esempio, eseguire verifiche hardware. Esiste anche la possibilità di eseguire il debug del codice.

Le fasi del progetto

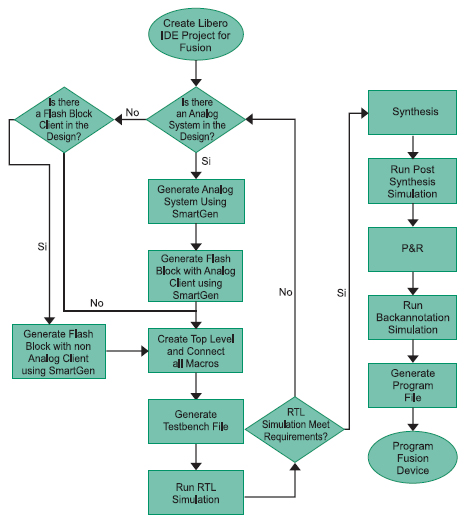

Le principali fasi di progettazione sono due. Nella prima l’oggetto viene descritto come entity, cioè come il componente viene visto dall’esterno. Questa sezione comprende generalmente le porte di comunicazione, i tempi di ritardo, la larghezza dei bus e i parametri di configurazione. Nella seconda si progetta l’architettura interna in cui si descrive come il dispositivo funziona: è questa la parte più importante perché costituisce la descrizione funzionale vera e propria. Di solito vengono usati due stili per descrivere questa seconda parte: behavioural o structural. Con il primo si descrive la relazione funzionale ingressi-uscita tramite una funzione o un algoritmo; se invece si usa lo stile structural si rappresenta la struttura interna del dispositivo formata da componenti di più basso livello ed i loro collegamenti (RTL, cioè Register Transfer Level), ovvero si decide già con quali oggetti realizzale la funzionalità e li si connette tra di loro. Nella progettazione di un nuovo dispositivo, di solito, si parte da una descrizione behavioural di alto livello, per passare poi ad una descrizione RTL ovvero costituito dai componenti fondamentali digitali come i registri, l’ALU, i bus e le macchine a stati. L’ultimo passo di traduzione del modello RTL in una netlist è eseguito in maniera automatica dal software utilizzato; tale processo è detto Synthesis. Il sintetizzatore produce una netlist ovvero un file vhdl o verilog di istanze di celle della tecnologia su cui viene “mappato” il circuito digitale. Durante l’esecuzione di tutto il flusso di progettazione si effettuano delle simulazioni per verificare che sia mantenuta la congruenza tra i vari modelli behavioural, RTL e netlist. Per effettuare queste simulazioni si usa un testbench, scritto anche esso in vhdl, che ha la funzione di generare gli stimoli sugli ingressi del circuito e di verificare la correttezza delle uscite. Nel caso di Fusion, essendo una FPGA, vale tale discorso. A questo, però, si aggiunge l’ulteriore fase di istanziare e configurare anche i blocchi analogici di cui è dotata. In Figura 3 si riportano le fasi di progettazione da seguire relativamente a Fusion.

Figura 3. Le fasi di progettazione di una FPGA Actel Fusion consistono in: configurare i blocchi analogici e digitali, creazione della netlist, simulazione, sintesi e programmazione

UN ESEMPIO: POWER MANAGEMENT

Per entrare nel dettaglio della progettazione di un dispositivo Fusion e per acquisire praticità nell’uso dell’ambiente integrato Libero IDE di Actel, si farà riferimento ad un esempio di power management. In genere, si utilizza questo termine per descrivere il processo di monitoraggio dell’alimentazione dei circuiti integrati, al fine di prevenire condizioni anomale di funzionamento. L’esempio a cui si farà riferimento deve monitorare la tensione di alimentazione, quella fornita al carico e la relativa corrente. Sulla base di valori di soglia pre-configurati (di correte e tensione), sarà controllato un gate della FPGA con il compito di fornire o bloccare la tensione di alimentazione al carico. Lo schema di principio è riportato in Figura 4.

Figura 4. Schema di principio per implementare la funzione di power management. Essa consente controllare la corrente erogata al carico, evitando condizioni anomale di funzionamento che possano danneggiare i circuiti elettronici

In particolare, i segnali sono indicati con AV33V, AC33V e AV33VLOAD. Gli step da seguire per andare dall’idea funzionale del progetto fino alla programmazione del chip si posso riassumere come segue (si fa notare che tali fasi valgono per qualunque progetto con Actel Fusion):

- Creazione di un progetto in Libero IDE

- Configurazione Analog System con

- SmartGen

- Configurazione Flash Memory System con SmartGen

- Creazione della Netlist e. Creazione Testbench

- Simulazione RTL

- Sintesi

- Simulazione post-sintesi

- Place-and-Route

Sarà fornita ora una breve descrizione di ognuno di questi passi, con le relative schermate del software Libero IDE.

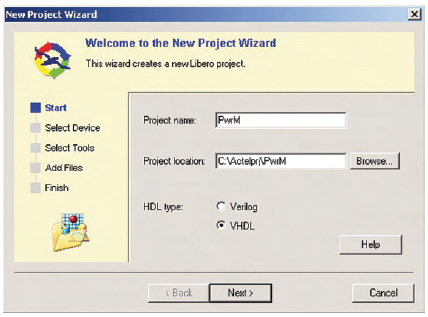

Creazione di un progetto in Libero IDE

- .Selezionare FilexNew Project.

- Inserire il nome del progetto, selezionare il linguaggio HDL (nel caso in esame si sceglierà il VHDL).

- Fare click su Next (Figura 5).

Nella schermata successiva, selezionare:

Family= Fusion, Die=AFS600, Package=256 FBGA. Fare click su Finish e sarà così creato un nuovo progetto (Figura 6).

Configurazione Analog System con SmartGen

Sarà mostrato come creare il blocco analogico per il monitoraggio della corrente e tensione di alimentazione. Il discorso è analogo per gli altri blocchi.

- Fare click su SmartGen;

- Selezionare Analog System Builder;

- Selezionare Current Monitor ed inserire i parametri relativi all’acquisizione;

- Fare click su Add to System per la configurazione del Current/Voltage Monitor (Figura 7). Sarà necessario specificare le soglie entro cui considerare questi valori normali;

- Fare click su OK;

- La schermata visualizzata, detta Analog System Builder elenca le periferiche analogiche configurate;

- La stessa procedura dovrà essere ripetuta per ciascuno dei blocchi analogici che si desidera aggiungere. Al termine di questa fase fare click sul pulsate Generate ed immettere il nome del core analogico (nell’esempio usare AS_PwrM). Fare click su OK.

- Chiudere la finestra Analog System Builder.

Configurazione Flash Memory System con SmartGen

Dopo aver creato i blocchi analogici, è indispensabile generare una corrispondente versione nella memoria Flash. Durante la fase b, infatti, viene generato un file NCF che deve essere importato nel Flash Memory System della FPGA. Per fare questo:

- Richiamare SmartGen;

- Richiamare Flash System builder;

- Selezionare Analog System dalla lista Available Client Types e fare click su Add to System;

- Selezionare AS_PwrM nella relativa combo box e fare click sul pulsante OK.

- Nella schermata presentata dal software, fare click su Generate per completare il progetto ed immettere il nome del Flash Block (nell’esempio si utilizza nvm_sysm);

Creazione della Netlist

È necessario creare una netlist in VHDL (o alternativamente in Verilog) per istanziare e connettere tutti i sotto-blocchi, esattamente come avviene in qualunque progetto HDL. Il codice completo di questo esempio è contenuto nel file Powe_Management.vhd nella cartella di esempi di Libero IDE. Per importare il file selezionare FilexImport, indicare il percorso e fare click su Import. Nel Listato 1 si riporta parte del codice VHDL.

library ieee;

use ieee.std_logic_1164.all;

library fusion;

entity Power_Management is —- Top level entity

port(...);

end Power_Management;

architecture DEF_ARCH of Power_Management is

component AS_PwrM is—-Analog System generated by SmartGen

port(...

INIT_ADDR : in std_logic_vector(8 downto 0); INIT_DATA :

in std_logic_vector(8 downto 0); INIT_DONE, INIT_ACM_WEN,

INIT_ASSC_WEN, INIT_EV_WEN, INIT_TR_WEN : in std_logic

... );

end component;

component nvm_sysm is —- Flash Memory System generated by SmartGen

port(INIT_CLK, SYS_RESET, INIT_POWER_UP : in std_logic;

INIT_DONE : out std_logic; INIT_DATA :

out std_logic_vector(8 downto 0); INIT_ADDR :

out std_logic_vector(8 downto 0); INIT_ACM_WEN,

INIT_ASSC_WEN, INIT_EV_WEN, INIT_TR_WEN : out std_logic);

end component;

begin

INIT_DONE<=INIT_DONE_net;

nvm_system_inst:nvm_sysm—-Flash Memory System instantiation

port map (

INIT_CLK=>SYS_CLK,

SYS_RESET=>SYS_RESET,

INIT_POWER_UP=>INIT_POWER_UP,

INIT_DONE=>INIT_DONE_net,

INIT_DATA=>INIT_DATA_to_INIT_DATA,

INIT_ADDR=>INIT_ADDR_to_INIT_ADDR,

INIT_ACM_WEN=>INIT_ACM_WEN,

INIT_ASSC_WEN=>INIT_ASSC_WEN,

INIT_EV_WEN=>INIT_EV_WEN,

INIT_TR_WEN=>INIT_TR_WEN

);

analog_system_inst AS_PwrM —- Analog System Instantiation

port map (

...

INIT_DATA => INIT_DATA_to_INIT_DATA,

INIT_ADDR => INIT_ADDR_to_INIT_ADDR,

INIT_DONE => INIT_DONE_net,

INIT_ACM_WEN => INIT_ACM_WEN,

INIT_ASSC_WEN => INIT_ASSC_WEN,

INIT_EV_WEN => INIT_EV_WEN,

INIT_TR_WEN => INIT_TR_WEN

);

AV33V_ON_ON <= (not AV33V_UNDER2P5) and (not AV33V_OVER4P0) and (not

AC33V_OVER1P5A) and (not AV33VLOAD_OVER3P75); —-Gate Driver Turn-ON/OFF

condition

end DEF_ARCH;

| Listato 1 |

Creazione Testbench

A questo punto che sono stati definiti i singoli blocchi (punti a,b e c) e le relative interconnessioni (punto d), è necessario disporre di un file di Testbench se si vuole effettuare la simulazione dell’hardware. È possibile crearne uno manualmente oppure importare quello contenuto nella cartella di esempi (tb_new_pwr_1.vhd). Per importare il file selezionare FilexImport e selezionare Stimulus Files dal menu a tendina; cercare il file suddetto. Fare click su Import.

Simulazione RTL

Per avviare la simulazione:

- Richiamare ModelSim.

- Avviare la simulazione per 6ms

- Verificare che il risultato della simulazione rispetti quanto previsto in fase di progettazione

Sintesi

Per trasformare quanto finora configurato in un linguaggio comprensibile dalla FPGA richiamare Synplify e fare click sull’icona Synthesis. Fare click su Run per eseguire la sintesi.

Simulazione post-sintesi

Dopo aver eseguito la sintesi, fare click sull’icona Simulation per continuare con la simulazione post-sintesi.

Place-and-Route

Fare click su Place-and-Route e seguire le istruzioni riportate nella finestra del Wizard per selezionare il dispositivo appropriato. Nell’esempio selezionare:

- Die: AFS600

- Package: 256FBGA

- Speed: -2

- Die Voltage: 1.5

Fare click sul pulsate Next.