In questo articolo si cerca di fornire ai progettisti e agli sviluppatori che lavorano con FPGA, alcune indicazioni per sviluppare un progetto power sensitive, il cui obbiettivo principale sia mantenere basso il consumo di potenza.

Spesso a determinare quale FPGA utilizzare per un progetto sono le specifiche stesse del progetto. Solitamente queste sono catalogabili in categorie ricorrenti riguardanti la potenza consumata, le prestazioni (o la velocità), la logica da implementare, il numero di I/O necessari. La scelta del dispositivo FPGA è quindi frutto di un attenta valutazione dei parametri elencati in precedenza.

PROGETTI SENSIBILI AL COSTO E AL CONSUMO DI POTENZA

Negli ultimi anni i progetti di dispositivi a batteria e a basso costo hanno avuto un aumento notevole, questo ha generato una conseguente richiesta di semiconduttori a bassa potenza. Il consumo di potenza è perciò diventato parte integrante delle specifiche di progetto. Contemporaneamente la domanda di nuove funzionalità e performance crescenti rimane una costante per i nuovi progetti, ora però viene imposto come vincolo, oltre a quello di non incrementare i costi, quello di non assorbire ulteriore corrente dalla batteria. Nel passato per rispondere a requisiti di basso assorbimento gli sviluppatori si sono affidati ad ASIC anziché alle FPGA. Oggi, con prodotti che hanno una vita sempre più breve, frequenti rischi di errore dovuti ai tempi brevi dedicati alla progettazione per esigenze di arrivare quanto prima sul mercato, le ASIC con il loro contenuto immutabile risultano rischiose e spesso impraticabili. Il risultato è stato che, per i prodotti con un ciclo di vita breve, le PLD sono diventate la scelta preferita. Questo ha generato tra i produttori di logiche programmabili una gara a soddisfare le esigenze del mercato, in particolare con riferimento ai prodotti lowower si è scatenata la sfida per il prodotto con i consumi più ridotti.

POTENZA STATICA E POTENZA DINAMICA

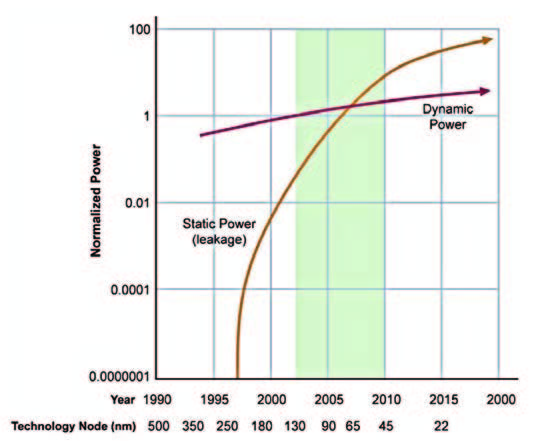

Non qualsiasi logica programmabile risulta adatta per un progetto low-power, alcune delle attuali FPGA spacciate per low-power consumano anche 30mA che è almeno un ordine di grandezza superiore a quello che dovrebbe essere il consumo di un dispositivo alimentato a batteria attento al consumo di corrente. Molti dei dispositivi FPGA SRAM-based, ossia che ad ogni avvio richiedono la programmazione, sono soggetti a correnti di inrush e di boot elevate. Questo si traduce in un consumo di corrente prelevato dalla batteria. I dispositivi flash-based, tipicamente le CPLD, al contrario non richiedono la configurazione allo startup e quindi neppure un dispositivo contenente il codice di configurazione (boot PROM, flash, microcontrollori, etc.) che si attivi ad ogni nuovo ciclo di alimentazione del prodotto. La scelta di un dispositivo flash-based quindi comporta una riduzione dei componenti sulla scheda, un risparmio di spazio e un risparmio di corrente. Non solo, si incrementa l’affidabilità, si semplifica la gestione del magazzino e si abbattono i costi complessivi fino ad un 70% rispetto alla scelta di una FPGA SRAMbased. Dopo che l’FPGa è stata configurata, il consumo di potenza può avvenire in due forme, statico o dinamico (o anche detto attivo). La potenza statica è legata al consumo di corrente dell’FPGA quando viene alimentata, configurata e lasciata non operativa. La potenza dinamica invece si rileva quando il dispositivo sta lavorando attivamente. Come presumibile il contributo maggiore tra le due è dovuto alla potenza dinamica. Per questi motivi esistono tecniche che mirano a ridurre principalmente questo tipo di consumi. Nel corso degli anni grazie ai progressi tecnologici si avuto una costante riduzione di tecnologia nei processi produttivi dei semiconduttori, richiedono tensioni di alimentazione ai dispositivi sempre più basse. Non bisogna però dimenticare che questo si traduce in un consumo di potenza statica superiore, necessario per adattare i livelli a quelli abituali dei circuiti elettronici, prima che questi risultino disponibili sui pin della FPGA. In pochi anni questo ha determinato un ribaltamento della situazione con i consumi statici che sono comparabili se non superiori a quelli dinamici. In figura 1 è mostrato l’andamento delle due componenti della potenza nel corso degli anni. Sull’asse x è mostrato anche il progresso tecnologico nella tecnologia di produzione dei semiconduttori.

Figura 1: potenza statica e potenza dinamica, andamento nel tempo con l’evolvere della tecnologia.

Sull’asse y la potenza normalizzata. Per rendere più appetibili i loro prodotti molti costruttori di FPGA sono a proporre dei chip che integrano sia una FPGA SRAM-based che una memoria flash. Il tutto integrato in un unico package. Ma questa è solo una soluzione intermedia che non elimina il consumo di potenza richiesto per la configurazione. Solamente nelle FPGA non volatili (flash-based) la configurazione è fissata nell’array e non comporta consumo di potenza ma bensì migliora i tempi di risposta e la sicurezza del sistema. Le FPGA flash-based non utilizzano milioni di bit di configurazione per memorizzare l’array, quindi consumano molto meno potenza statica e questo le rende ideali per dispositivi low-power. Oltre a questo dispongono di tool software che permettono di ridurre notevolmente il consumo di potenza. Se si sceglie via software di realizzare un layout pilotato dalla potenza si possono ridurre fino al 30% i consumi rispetto a un software di piazzamento e sbroglio (place and route) tradizionale. Questa tipologia di Layout è spesso chiamata power-driven, non impatta sulle temporizzazioni ma permette di indirizzare il piazzamento del layout fisico del progetto in modo da minimizzare il consumo di potenza dinamica nelle applicazioni sensibili ai consumi. Il layout power driven opera in modo da ridurre il carico capacitivo sulle reti mediante la minimizzazione della lunghezza delle connessioni di sbroglio (routing). Il software cerca anche di ridurre la potenza necessaria per il pilotaggio delle reti di clock mediante la diminuzione delle risorse globali utilizzate dai clock. Oltre al layout power-driven, sono disponibili tool avanzati che consentono di ottenere una stima dei consumi già in fase di design. Ovviamente sono richiesti dati relativi al periodo in cui l’applicazione rimane in funzione o in standby poiché gli attuali tool analizzano la potenza sulla base dei consumi totali del progetto misurati in funzione del tempo. Tool di questo tipo permettono ai progettisti di creare un profilo di potenza per un dato design. Tale profilo può essere ottenuto da una combinazione di modalità dinamica, statica e in standby. La stima della potenza totale è basata sulla media ponderata del consumo di potenza in tutte le modalità,questo permette di ottenere una valutazione molto realistica dei consumi.

TECNICHE PER RISPARMIARE POTENZA

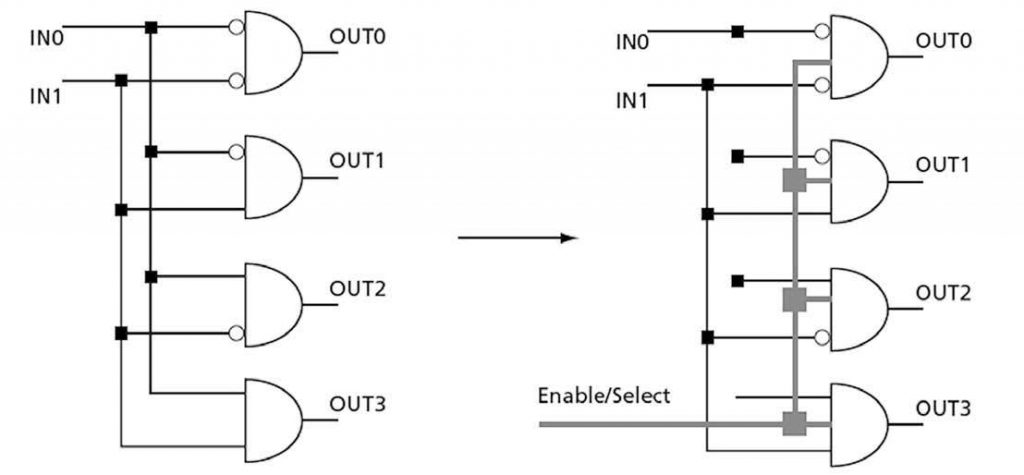

Come detto in precedenza, impostare attraverso i tool software un layout power-driven è un buon punto di partenza per il progetto. Esistono però altre cose che si possono definire per ridurre ulteriormente i consumi. Una di queste è ridurre la capacità di switching e la frequenza degli I/O, un alternativa potrebbe essere disaccoppiare gli I/O nelle fasi di sleep. Spesso quest’ultima cosa non è facilmente realizzabile, un alternativa può essere togliere l’alimentazione al core e lasciare l’alimentazione degli I/O applicata. Un’altra possibilità e ridurre lo swing di tensione per gli I/O, spesso è disponibile un opzione relativa al controllo dello slew-rate che permette di ridurre la corrente la corrente di switching in uscita. Se non si usa un intero banco di I/O perché non utilizzato dal progetto si può pensare di non alimentarlo, anche così si risparmia corrente. Spesso ci sono zone del progetto che non necessitano di frequenze di clock elevate, un eventuale riduzione di velocità potrebbe far risparmiare potenza. In questo caso il risparmio sulla potenza dinamica è direttamente proporzionale alla riduzione di frequenza. In molti casi tra le opzioni di ottimizzazione è prevista anche quella riportata come “enable register retiming to optimization” in questo modo il tool di place and route privilegerà i consumi. Oltre a questi suggerimenti legati soprattutto agli strumenti software che realizzando la compilazione e il fitting dell’FPGA, esistono alcuni utili consigli relativi alla codice HDL realizzato. In primo luogo la codifica di contatori e soprattutto macchine a stati. Quando si valuta la potenza dinamica, il numero di stati e soprattutto le transizioni tra gli stati incidono sul consumo. Utilizzare una codifica Gray piuttosto che una semplice codifica binaria aiuta sia il numero di transizioni logiche per passare da uno stato all’altro, sia il numero di transizioni complessive per un ciclo del contatore. Questo perché i flip-flop che commutano nel passaggio da uno stato al successivo sono meno se si utilizza una codifica Gray rispetto ad una codifica binaria. L’obbiettivo deve essere sempre quello di non far commutare segnali se non è indispensabile, poiché questo va ad incrementare la potenza dinamica consumata, in quest’ottica anche per un semplice decoder è bene non creare commutazioni in uscita se lo stesso non è utilizzato (figura 2).

Figura 2: utilizzo dei segnali di enable per ridurre le commutazioni indesiderate.

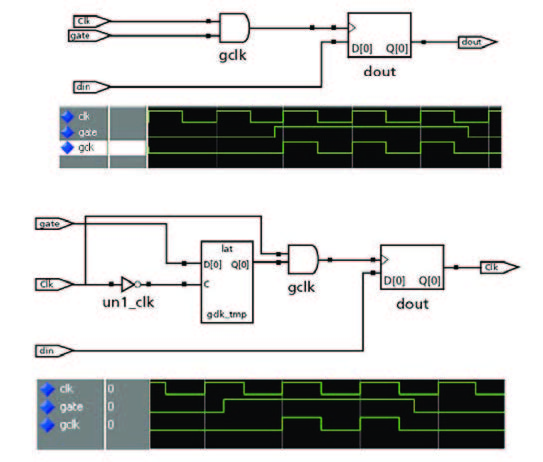

Il clock gating a livello RTL è un altro punto molto importante da considerare. Esitono due tipi di circuiti per il clock gating, ossia per decidere se inoltrare o meno il clock alla logica che segue, con o senza latch. In figura 3 si possono vedere i due circuiti a confronto.

Figura 3: Clock gating.

Il circuito senza latch impone che il segnale di gate debba essere mantenuto costante dal fronte di salita del clock al fronte di discesa , per prevenire glitch sul segnale di clock risultante. Con l’aggiunta di un latch si garantisce il mantenimento del segnale di enable per il clock e l’imposizione precedente non è più necessaria. Se nel design si identificano gruppi di flipflop che condividono lo stesso segnale di enable è bene, utilizzando il circuito di figura 3 con il latch, disabilitare le eventuali commutazione generate quando la logica non viene utilizzata. Un ulteriore accortezza che consente di ridurre il consumo di potenza, è quella di ridurre i glitch attraverso una riorganizzazione della logica. In figura 4 un esempio che illustra bene questo concetto.

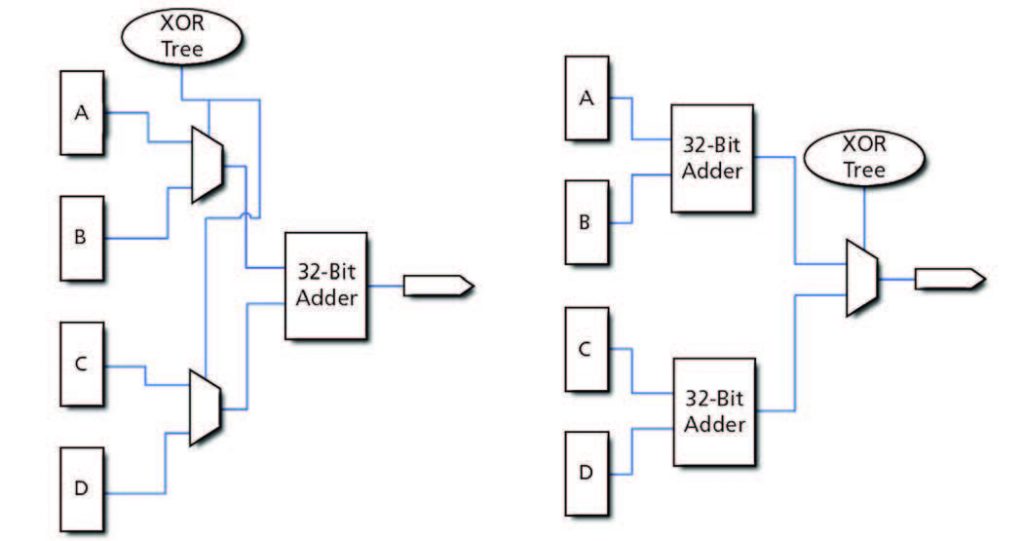

Figura 4: Riduzione dei glitch attraverso la riorganizzazione della logica.

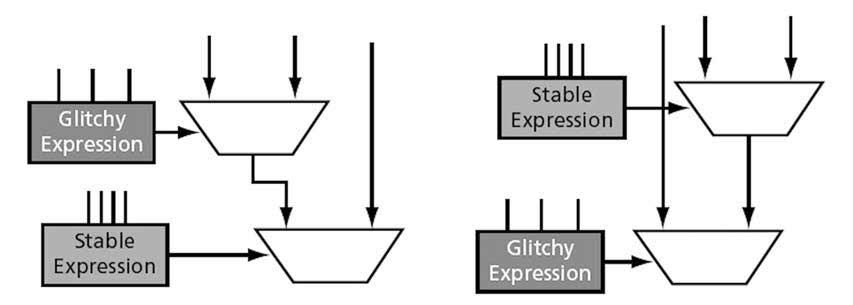

I dati A, B, C e D sono stabili poiché provengono da dei registri, se però il segnale del multiplexer non lo è, gli ingressi del sommatore a loro volta non risultano stabili e determinano un consumo di potenza. Modificando il circuito come nella parte destra di figura 4 si aumenta la quantità di logica richiesta si aumenta la quantità di logica richiesta per eseguire la stessa funzione, tuttavia i sommatori lavorano su dati stabili. Per ridurre la potenza causata dai glitch, altre tecniche utili sono fare uso di pipeline e introdurre le espressioni che possono causare glitch il più possibile avanti nella catena di propagazione del segnale (figura 5).

Figura 5: Riduzione della potenza minimizzando la propagazione delle commutazioni indesiderate.

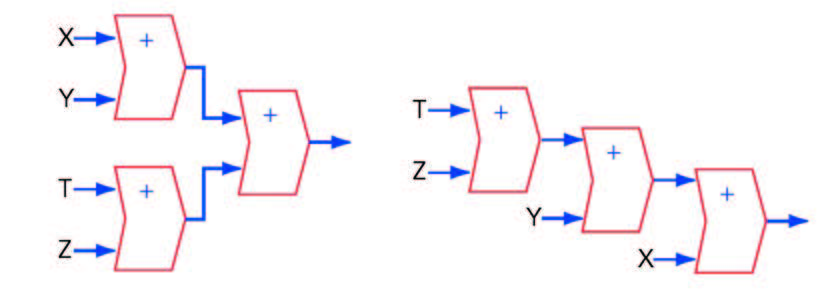

Un aiuto nel ridurre la potenza dinamica consumata è avere un idea della probabilità di switching dei segnali, in figura 6 sul lato destro abbiamo un esempio di un sommatore per quattro segnali, così come lo realizzerebbe un qualsiasi tool di sintesi, minimizzando il ritardo dei segnali.

Figura 6: Riduzione della potenza in base alla probabilità di commutazione.

Tale circuito è ottimo se i quattro segnali coinvolti avessero tutti la stessa probabilità di comunicazione, se invece un segnale ha una probabilità più alta, per esempio X allora il circuito sul lato destro di figura 6 è da preferire poiché una commutazione di X determina una minore attività di tutta la rete e un risparmio di potenza.

CONCLUSIONI

Nella realizzazione di un progetto con FPGA orientato ad ottenere di bassi consumi di potenza, non ci si può limitare a considerare solo la potenza statica o la potenza dinamica, ma devono essere valutate entrambe. Le tecniche di riduzione dei consumi intervengono soprattutto sulla potenza dinamica e devono essere un mix di adeguate impostazioni dei tool software e di codice HDL pensato e scritto con un occhio di riguardo ai consumi di corrente. Per la riduzione dei consumi statici la scelta migliore è di affidarsi a dispositivi flash-based sempre che questo ponga un limite relativamente al numero di I/O o alle dimensioni del progetto. Per concludere sicuramente abbinare una FPGA flash-based e utilizzare le tecniche di design low-power descritte in precedenza è un punto di partenza ottimale per un design attento ai consumi con FPGA.