Considerare una segnale digitale coma un’onda quadra ideale è solo un’approssimazione che non sempre è applicabile. Ecco cosa succede in realtà.

Tutti ci rendiamo conto che considerare un segnale digitale come una onda quadra ideale, è una comoda semplificazione della realtà. Tanto più si riducono i tempi di commutazione ed aumentano le frequenze, tanto meno la forma d’onda reale assomiglia ad un’onda quadra. Ogni distorsione del segnale riduce, fino a compromettere completamente, l’affidabile riconoscimento del dato trasmesso.

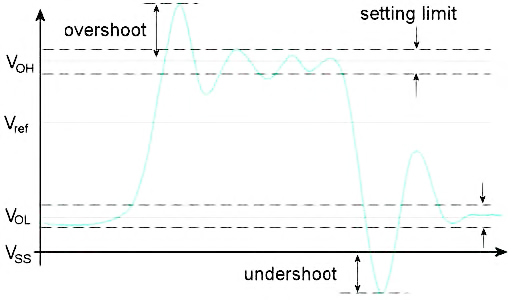

Figura 1: segnale digitale reale.

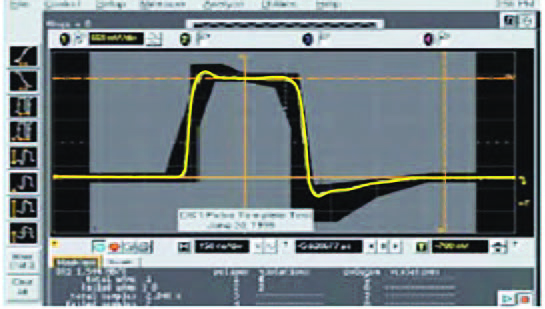

Possiamo avere distorsioni dei livelli in tensione del segnale, con overshoot/undershoot, “scalini” nei fronti di salita e discesa, innalzamento del livello minimo raggiunto o abbassamento del livello massimo (attenuazione). La cosa è resa evidente osservando la forma d’onda tipica di un segnale digitale in figura 1. Possiamo anche avere distorsioni temporali, con raggiungimento del livello logico in ritardo o falsi impulsi creati da oscillazioni sovrapposte ai fronti di commutazione, abbastanza ampie da attraversare le soglie logiche e creare false commutazioni. Come vediamo in figura 2, esiste un campo di definizione, una “maschera” che deve racchiudere il nostro segnale affinché ne sia garantita la qualità, o Signal Integrity, cioè la certezza che il segnale sia riconosciuto correttamente come stato logico e temporizzazione all’ingresso del circuito ricevente, al termine di una generica interconnessione.

Figura 2: maschera di accettazione di un segnale (oscilloscopio Agilent Infinium).

La riduzione di dimensioni dei transistor nei moderni circuiti integrati e l’uso di frequenze di commutazione sempre più elevate, esasperano il fenomeno, facendo dire a qualcuno che i progettisti digitali si dividerebbero in due categorie: quelli che hanno problemi di Signal Integrity e quelli che ne avranno a breve. Forse qui c’è un po’ di esagerazione, ma la frase rende bene l’idea del “trend”. La diffusione di collegamenti inter-integrato veloci come i SERDES (Serializzatori-Deserializzatori) e bus come PCI basati su gruppi di connessioni seriali, invece che bus paralleli, hanno molto contribuito a spingere le applicazioni digitali nel campo in cui occorre prestare molta attenzione a problematiche di Signal Integrity. Il rischio incombe sulla funzionalità dei prototipi, ma forse, soprattutto, sull’affidabilità dei prodotti finiti e la loro robustezza verso variazioni delle condizioni ambientali ed evoluzioni tecnologiche dei componenti impiegati nel corso della vita in produzione (shrink di geometria). Infatti, è tipico di una classe di problemi SI, vedere improvvisamente aumentare malfunzionamenti ove non ve ne erano mai stati e scoprirne la causa in una versione aggiornata di circuiti integrati funzionalmente equivalenti, ma con tempi di commutazione più veloci. Sotto il generico cappello “Signal Integrity” sono racchiuse varie problematiche legate alla propagazione dei segnali interni ad una applicazione digitale:

- Integrità del singolo segnale

- Crosstalk (diafonia)

- Power Collapse

- EMI.

Tutte queste problematiche diventano più severe al crescere delle frequenze operative ed al decrescere dei tempi di transizione. Vediamo in maggiore dettaglio ciascuna area. La cura dell’integrità del singolo segnale coincide sostanzialmente con quanto anticipato. Esiste un campo di definizione desiderabile nello spazio tempo/tensione, cui attenersi. I detrattori sono molteplici, a partire dalle riflessioni di segnale causate sulla linea da discontinuità nell’impedenza. Anche le attenuazioni in frequenza dovute ad effetto pelle possono diventare rilevanti e condurre a riduzioni dell’ampiezza o allungamento dei tempi di assestamento inaccettabili. Siamo interessati ad avere una transizione pulita, senza inversioni di polarità o incertezze, in particolare nella banda grigia tra le soglie di riconoscimento dei livelli alto e basso. Anche l’assenza di sotto e sovra elongazioni del segnale è auspicabile (undershoot e overshoot), potendo comportare eccessive situazioni di stress elettrico ed abbreviare la vita utile del componente. Abbiamo fenomeni di “Crosstalk” quando segnali diversi si influenzano a vicenda per accoppiamenti capacitivi o induttivi creati dai parametri parassiti del nostro circuito, cioè da componenti virtuali distribuiti nell’applicazione e creati dagli effetti fisici della presenza di conduttori ed isolanti. Tipicamente abbiamo un segnale aggressore, che altera lo stato elettrico di un segnale indipendente, magari anche statico. L’aggressore è solitamente caratterizzato dall’avere fronti ripidi e/o elevate frequenze di commutazione. Una particolare forma di Crosstalk si ha in presenza di molti driver in commutazione simultanea, si pensi ad un bus dati/indirizzi verso memorie. Tale fenomeno è indicato come SSN (Simultaneous Switching Noise) o SSO (Simultaneous Switching Outputs). Purtroppo, poco si può fare a livello di board o di sistema se un componente presenta elevata rumorosità SSN/SSO intrinseca. Fenomeni di Power Collapse (chiamato anche IR-drop o V) si verificano localmente nell’alimentazione del singolo circuito integrato, quando il sistema di alimentazione della board non presenta impedenza sufficientemente bassa in corrispondenza di alcune gamme di frequenza operativa dei componenti (vedi in Riferimento 2 una presentazione generale delle problematiche di Power Integrity). La richiesta di rapidi picchi di corrente causa, in tal caso, cadute di tensione istantanee che possono condurre la circuiteria logica ad operare fuori specifica, anche se per tempi molto brevi. Questo può condurre a rilassamento dei fronti di commutazione e conseguenti violazioni dei tempi di setup e hold time con generazione e propagazione di errori logici. Il fenomeno contribuisce anche all’incremento del jitter sul segnale (cioè l’indeterminazione nell’istante di commutazione). L’emissione di interferenze elettromagnetiche (EMI) è un capitolo ampio ed articolato che va ben oltre l’integrità di segnale, pur essendovi strettamente legato. Ogni qualvolta abbiamo overshoot o undershoot nel nostro percorso di segnale, ci esponiamo al rischio di emissioni elettromagnetiche superiori ai livelli che devono essere garantiti dalle normative internazionali. Abbiamo, quindi, un danno multiplo da componenti di segnale ad altra frequenza assolutamente non necessarie alla funzionalità del circuito, potenzialmente nocivo per la sua affidabilità, per di più sorgente di potenziale crosstalk verso i circuiti vicini e di emissioni inopportune. L’emissione potrebbe anche essere vista, in generale, come una perdita di energia che in tal modo viene resa indisponibile al ricevitore di segnale. La maggiore differenza tra le problematiche SI ed EMI sta nell’ampiezza dei segnali coinvolti. Nel considerare SI lavoriamo su ampiezze pari a qualche percento della tensione di alimentazione, quindi dell’ordine delle decine o centinaia di millivolt. Segnali nell’ordine di due o tre ordini di grandezza inferiori, sono spesso sufficienti a creare problemi di compatibilità elettromagnetica, se le frequenze in gioco sono abbastanza elevate. Poche e semplici buone abitudini di progettazione dovrebbero essere sempre applicate per evitare problemi. Assieme al percorso di segnale, andrebbe attentamente progettato anche il ritorno delle correnti coinvolte, la cosidetta “massa”, evitando interruzioni e strozzature (quali l’attraversamento del footprint di un connettore, ad esempio). I segnali dovrebbero vedere una impedenza quanto più possibile costante lungo il loro percorso, anche se non necessariamente un valore imposto come nelle boards ad impedenza controllata. Le geometrie delle connessioni di segnale su un PCB dovrebbero avere geometrie regolari, con spessori e distanza dalla propria massa (return path) costanti, evitando salti tra strati distanti dello stampato. Il dimensionamento della distribuzione dell’alimentazione dovrebbe essere fatto non solo in continua, ma verificando la capacità di rispondere a richieste di transitori di corrente nell’intera gamma di frequenze operative del circuito. La banda passante del sistema andrebbe mantenuta quanto minore possibile, evitando di utilizzare componentistica più veloce del necessario. Notare che questo può essere assai difficile da ottenere in pratica, innanzitutto per l’impossibilità di modulare a piacere i parametri temporali dei componenti, poi perché quasi mai i costruttori dichiarano i tempi di transizione minimi. Il parametro funzionalmente più critico è, infatti, normalmente il tempo di transizione massimo, tanto più veloce tanto meglio, da un punto di vista puramente

circuitale. Purtroppo non è cosi dal punto di vista SI/EMC. Quando queste regole di base non sono sufficienti e le tecniche di Signal Integrity vanno applicate nella loro interezza e complessità? Certamente non è possibile garantire a priori che un dato progetto sia esente da problemi di SI, dipendendo troppo questi ultimi dalle geometrie, dimensioni e topologie specifiche di ogni applicazione. Si possono, però, indicare, alcuni criteri per comprendere se ci possiamo attendere problemi e convenga approfondire l’analisi SI:

a) Il ritardo nella propagazione del segnale lungo l’interconnessione è superiore al 20% della durata del fronte di salita del segnale. Le riflessioni saranno in tal caso in grado di distorcere apprezzabilmente il segnale.

b) Vi sono segnali digitali “veloci” nell’applicazione. Per fare dei numeri e cercare di definire “veloce”, diremo che lavoriamo con frequenze maggiori di 20 MHz e/o rise/fall time minori di 1 nsec.

c) Sono necessari compromessi quali piani di massa parziali e non estesi a tutta la scheda.

d) Densi collegamenti digitali, paralleli per tratti significativi (vedi bus di memoria).

Non sempre si conoscono con precisione a priori, i parametri dei segnali con cui abbiamo che fare.

Alcune assunzioni ragionevoli, valide per segnali ripetitivi, come clocks:

- Rise e Fall Time possono essere considerai uguali e di durata pari all’1% del periodo del segnale.

- La banda passante di un segnale digitale può essere considerata pari a 5 volte la frequenza di clock.

- La relazione tra banda passante (BW) e Rise Time ( ) si può considerare pari a BW = 35.

Nei casi sopra identificati, le regole di progettazione diventano assai più stringenti, anche se chiaramente da applicare non alla totalità dei segnali del circuito. I circuiti più veloci vanno chiaramente identificati ed il layout va progettato in modo da separarli fisicamente il più possibile da potenziali “vittime”. Le interconnessioni ed i segnali vanno trattati come linee di trasmissione ad impedenza costante (entro pochi %). L’impedenza deve corrispondere alla sorgente e destinazione e le linee devono essere opportunamente terminate all’estremità remota per evitare riflessioni. La distanza da segnali potenzialmente aggressori andrà mantenuta maggiore di un minimo valore per evitare crosstalks (separazione almeno due volte la larghezza della traccia di segnale). L’impedenza del percorso di ritorno dei segnali va minimizzata, assegnando strati del PCB dedicati (o comunque rame quanto più abbondante possibile). Connessioni differenziali andranno preferite dove possibile, traendo beneficio dalla parziale cancellazione del campo elettromagnetico, dovuto alla prossimità del segnale di andata e ritorno e dall’immunità presentata dal ricevitore differenziale a rumore e crosstalk sovrapposto alle due linee (rumore di modo comune). Le porzioni critiche (high speed) devono essere modellizzate e simulate prima della costruzione del prototipo fisico, in modo da poterle ottimizzare al costo minimo (vedremo qualcosa sulla modellizzazione in uno dei prossimi Tips’n Tricks). I prototipi fisici andranno poi sottoposti a misure della qualità dei segnali in nodi critici del circuito e saranno eseguiti stress test, applicando condizioni limite per evidenziare possibili debolezze. Un possibile esempio consiste nel verificare il rispetto delle maschere di accettazione alimentando il circuito alla tensione minima e condizione di dissipazione massima, possibilmente anche elevando la temperatura ambiente. Violazioni non evidenti in condizioni nominali possono cosi essere meglio identificate e risolte. Certamente queste poche note costituiscono solo una elementare introduzione alla materia. Per approfondire, suggerisco di iniziare con l’ottimo corso online indicato in Riferimento 3.